# Fiber Distributed Data Interface (FDDI) Databook

# **FDDI**DATABOOK

1991 Edition

FDDI Overview

DP83200 FDDI Chip Set

Development Support

Application Notes and System Briefs

Appendix/Physical Dimensions

#### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Microtalker™ SABRTM Embedded System MICROWIRE™ Script Chek™ Abuseable™ Processor<sup>TM</sup> Anadig™ E-Z-LINK™ MICROWIRE/PLUSTM SCXTM SERIES/800™ ANS-R-TRAN™ **FACTTM** MOLETM APPSTM МРАТМ Series 900TM FACT Quiet Series™ **ASPECT™** FAIRCAD™ MSTTM. Series 3000TM Auto-Chem Deflasher™ Fairtech™ Naked-8TM Series 32000® ВСРТМ FAST® National® Shelf ChekTM BI-FETTM 5-Star Service™ National Semiconductor® Simple Switcher™ BI-FET IITM FlashTM National Semiconductor SofChek<sup>TM</sup> BI-LINETM **GENIXTM** Corp.® SONICTM NAX 800TM **SPIRETM BIPLANTM GNXTM** BLCTM **GTOTM** Nitride Plus™ Staggered Refresh<sup>TM</sup> STARTM BI XTM Nitride Plus Oxide™ **HAMRTM** ВМАСТМ HandiScan™ **NMLTM** Starlink<sup>TM</sup> Brite-Lite™ HEX 3000™ NOBUSTM STARPLEX™ **BSITM НРСТМ** NSC800TM Super-Block™ **BTLTM** 13L® **NSCISETM** SuperChip<sup>TM</sup> CDDTM **ICMTM** NSX-16™ SuperScript<sup>TM</sup> CheckTrackTM INFOCHEX™ NS-XC-16™ SYS32TM СІМТМ Integral ISETM NTERCOM™ TapePak® **CIMBUSTM** Intelisplay™ TDSTM **NURAMTM** ISETM **CLASICTM OXISSTM** TeleGate™ Clock**/**Chek™ ISE/06TM P2CMOSTM The National Anthem® COMBO® ISE/08TM PC Master™ Time/ChekTM COMBO ITM ISF/16TM Perfect Watch™ TINATM COMBO IITM ISE32™ Pharma Chek™ TLCTM COPSTM microcontrollers **ISOPLANAR™** PLANTM Trapezoidal<sup>TM</sup> **CRDTM** ISOPLANAR-ZTM **PLANAR™** TRI-CODE™ DA4TM **PLAYERTM** KeyScan™ TRI-POLYTM Datachecker® LMCMOS™ Plus-2TM TRI-SAFETM M2CMOS™ **DENSPAKTM** Polycraft™ TRI-STATE® DIBTM POŚilink™ Macrobus™ TURBOTRANSCEIVER™ Digitalker® Macrocomponent<sup>TM</sup> POSitalker<sup>TM</sup> VIPTM DISCERNIM MAXI-ROM® Power + Control™ VR32TM

ABEL™ is a trademark of Data I/O Corporation.

GAL® is a registered trademark of Lattice Semiconductor.

IBM®, PC® and PC-AT® are registered trademarks of International Business Machines Corporation.

PAL® is a registered trademark of and used under license from Advanced Micro Devices, Inc.

Meat ✓ Chek™

MenuMaster™

MICRO-DACTM

μtalker™

Microbus™ data bus

UNIX® is a registered trademark of AT&T Bell Laboratories.

XLNT Manager™ is a trademark of XLNT Designs Incorporated.

#### LIFE SUPPORT POLICY

DISTILL™

DNR®

**DPVMTM**

E2CMOSTM

**ELSTARTM**

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

POWERplanar™

QUAD3000TM

QUIKLOOKTM

**RATTM**

RTX16™

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

WATCHDOG™

**XMOSTM**

Z STARTM

883B/RETSTM

883S/RETSTM

XPI JTM

National Semiconductor Corporation 2900 Semiconductor Drive, P.O. Box 58090, Santa Clara, California 95052-8090 1-800-272-9959 TWX (910) 339-9240

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry or specifications.

#### **Introduction to FDDI (Fiber Distributed Data Interface)**

The role of fiber optics in Local Area Network (LAN) technology is as a high performance supplement to the 10 Mbit/sec IEEE 802.3 Ethernet network. The high performance fiber network of choice will be FDDI as specified by ANSI X3T9.5 Standard.

As computer applications become more complex, they drive the need for high-bandwidth interfaces such as FDDI.

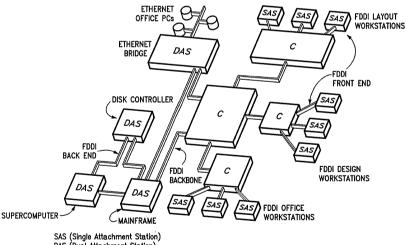

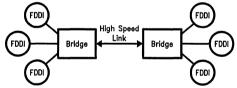

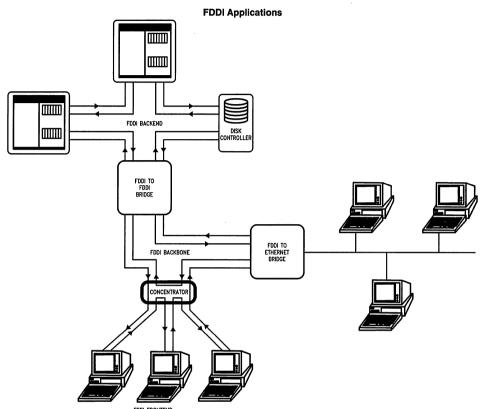

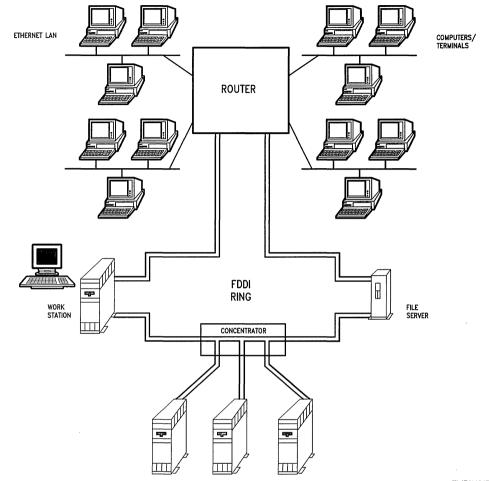

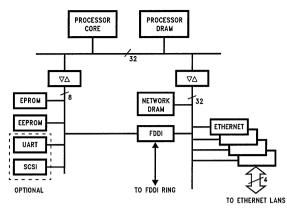

In addition to offering the highest bus speed performance of any standard LAN, FDDI offers a low-cost means for bridging from a conventional speed Ethernet to a high-speed fiber optic link. It works such that a backbone FDDI ring connects local islands of Ethernet workgroups to similar islands located in another part of an interoffice LAN (see *Figure 1*). Data flow across any of the Ethernet configurations—10 Base 2, 10 Base T, twisted-pair—can become bogged down considerably by heavy data transfer activity over an Ethernet backbone network. An FDDI backbone operating at about a 10-times-faster data rate than Ethernet can eliminate this bottleneck by providing a secondary high-speed data highway between these lower-speed workgroups.

FDDI LANs offer higher performance and are overcoming one of their earlier barriers to commercial use: cost-effect-

ive performance. Work has begun to standardize the use of twisted pair over shorter distances.

Because of its favorable cost/performance benefits, highlevel technology and backbone capability, FDDI and Ethernet are projected as the network combination of the future.

#### What FDDI Needs

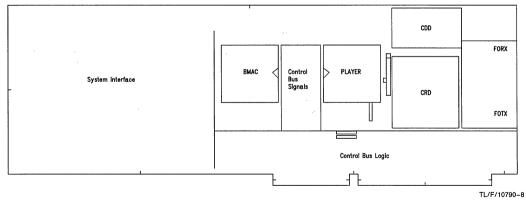

In order for FDDI to grow into a successful primary and backbone network, computer manufacturers need a standard chip set to make it practical and cost-effective. National Semiconductor, already the leading supplier of fully compliant IEEE 802.3 network integrated circuits for Ethernet, has developed a set of chips to support FDDI, the DP83200 FDDI chip set.

The key to building a family of industry-standard FDDI devices is to constantly work toward higher levels of integration. To this end, National has created semiconductor technologies that are migratable from today's multi-chip designs to tomorrow's single-chip solutions. Further integration to a 2-chip and single chip solution will provide even greater cost and performance benefits to network builders.

DAS (Dual Attachment Station) C (CONCENTRATOR)

FIGURE 1. FDDI can serve as a high-speed backbone for Ethernet or as a fast network to speed data between high-performance workstations, supercomputers and mainframes.

TL/F/10822-1

#### **Proven By The Process**

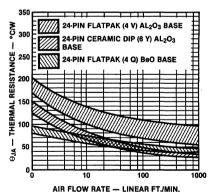

CMOS is the technology of choice for FDDI ICs. But CMOS varies considerably, according to manufacturer. National's version, called M²CMOS™, is one of the few types that can accommodate high-performance logic, memory and analog circuitry on the same substrate. National has also developed one of the leading BiCMOS processes in the industry. Since FDDI data rates are among the highest of any standard data communications application, a BiCMOS process with high-speed bipolar capability and low power consumption will be required in certain parts of the fiber-optic interface circuitry. Packaging will also become a crucial issue in the development of a chip set since it impacts both cost and performance.

#### Lab Work

As FDDI integrated network products enter the real world of the office or engineering workgroups, system integrators must ensure that all hardware and software components operate correctly with each other. Because of the complexity of the networks, workstations and their software, system integrators must perform interoperability tests. These are designed to verify the proper operation of the complete system.

Unfortunately, assembling all of the hardware and software needed to conduct interoperability testing outside the actual system is extremely difficult. But such testing is so important to chip and system designers that National has set up a dedicated FDDI LAN laboratory that allows its engineers and customers to accelerate their development of ad-

vanced networking products. Also available to customers on request is a document describing the interoperability testing performed by National.

The FDDI LAN lab is equipped with software, computers, printers and cable equipment from a variety of manufacturers. National engineers assist customers by testing the performance of individual components, including National's own networking chip sets, as well as entire systems.

The lab is a test bed for the FDDI chip set. Using the lab facilities, engineers can exercise the devices in all modes of operation to discover any problems before a system user does. If a user does discover a problem—at the chip or system level—the lab provides a resource in which to find a solution.

#### The Next Generation Solution

Designing and building the integrated circuit portion of FDDI is a great challenge to any semiconductor manufacturer. Not only are processing and packaging expertise essential, the successful chip maker must be well-versed in high-level behavioral modeling, top-down design methodologies, advanced software and CMOS/BiCMOS circuit design. The need for a high-performance fiber optic network is unquestioned. Evaluating hardware implementations is the first step in providing you with the performance and network management capabilities offered by the FDDI protocol.

National Semiconductor, with its long resume of Ethernet leadership and IC excellence, application support materials and experience, is positioned to take the hardware lead in these next-generation FDDI networking solutions.

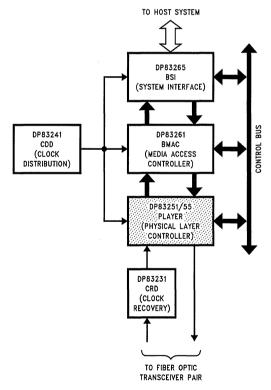

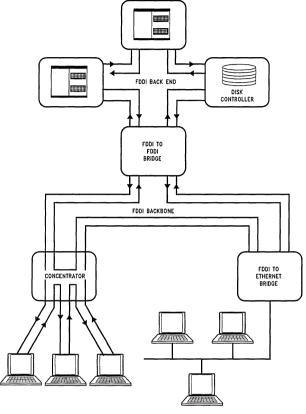

#### National DP83200 FDDI Chip Set Block Diagram

TL/F/10822-2

#### **Product Status Definitions**

#### **Definition of Terms**

| Data Sheet Identification     | Product Status            | Definition                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advance Information           | Formative or<br>In Design | This data sheet contains the design specifications for product development. Specifications may change in any manner without notice                                                                                                                                     |  |  |  |

| Preliminary                   | First<br>Production       | This data sheet contains preliminary data, and supplementary data will be published at a later date. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |

| No<br>Identification<br>Noted | Full<br>Production        | This data sheet contains final specifications. National Semiconductor Corporation reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                       |  |  |  |

National Semiconductor Corporation reserves the right to make changes without further notice to any products herein to improve reliability, function or design. National does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.

## **Table of Contents**

| Alphanumeric Index                                                        | ix             |

|---------------------------------------------------------------------------|----------------|

| Section 1 FDDI Overview                                                   |                |

| An Overview of FDDI: The Fiber Distributed Data Interface                 | 1-3            |

| Section 2 DP83200 FDDI Chip Set                                           |                |

| DP83231 CRD Device (FDDI Clock Recovery Device)                           | 2-3            |

| DP83241 CDD Device (FDDI Clock Distribution Device)                       | 2-18           |

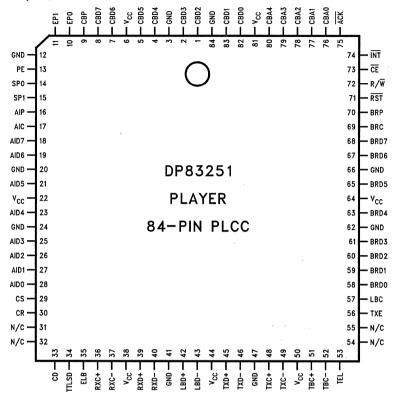

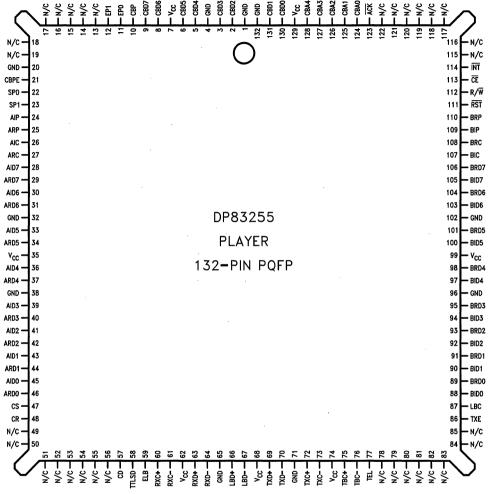

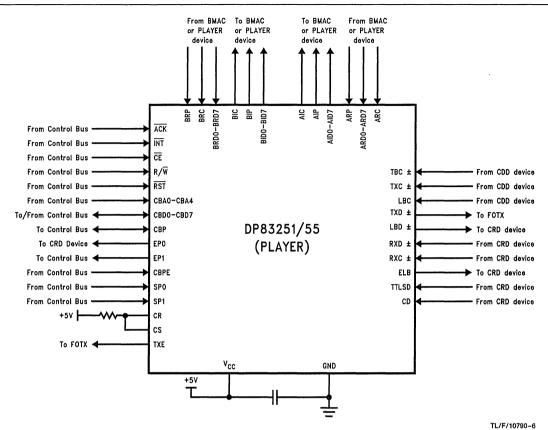

| DP83251/DP83255 PLAYER Device (FDDI Physical Layer Controller)            | 2-36           |

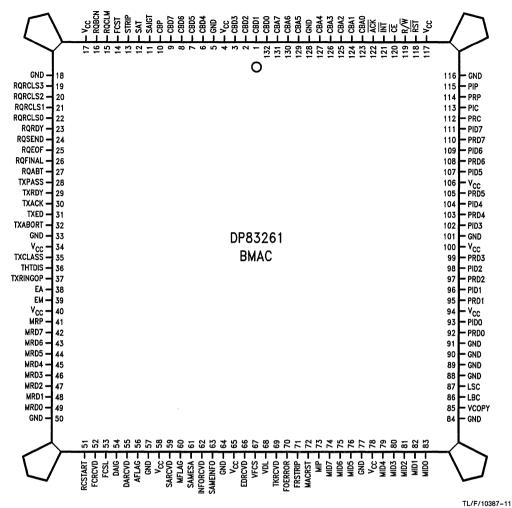

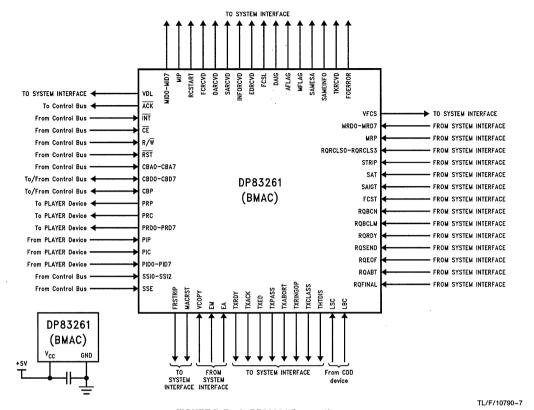

| DP83261 BMAC Device (FDDI Media Access Controller)                        | 2-130          |

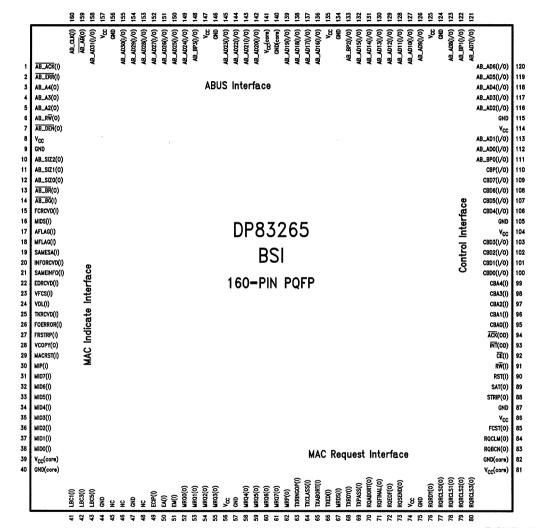

| DP83265 BSI Device (FDDI System Interface)                                | 2-260          |

| Section 3 Development Support                                             |                |

| DP83200EB FDDI AT Evaluation Kit                                          | 3-3            |

| DP83200SMT XLNT Manager FDDI Station Management (SMT) Software Support    |                |

| Package                                                                   | 3-15           |

| Section 4 Application Notes and System Briefs                             |                |

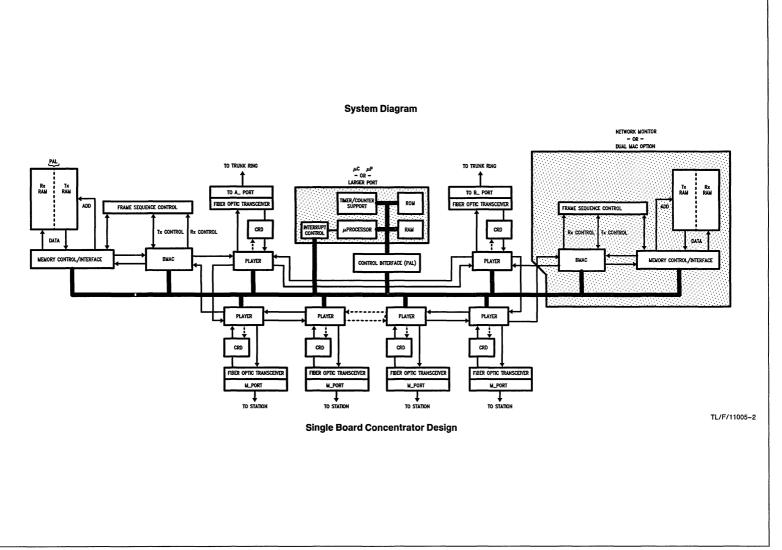

| AN-675 Designing FDDI Concentrators                                       | 4-3            |

| AN-741 Differentiating FDDI Concentrators                                 | 4-11           |

| AN-740 Incorporating FDDI MAC Level Bridging                              | 4-28           |

| AN-726 Station Management Simplified                                      | 4-36           |

| AN-727 A Guide to the Implementation of Physical Connection Management    | 4-46           |

| AN-728 FDDI Station Management with the National Chip Set                 | 4-59           |

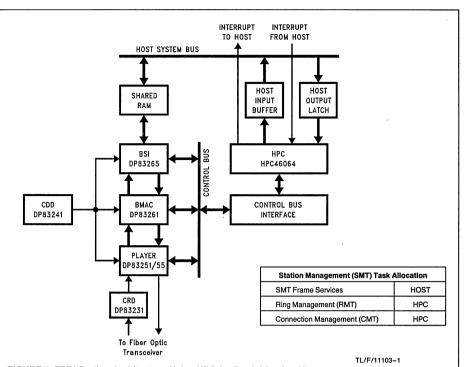

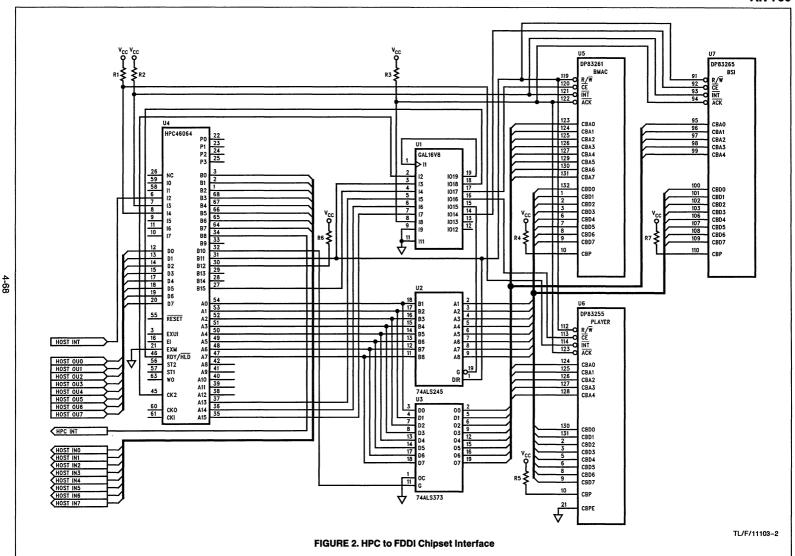

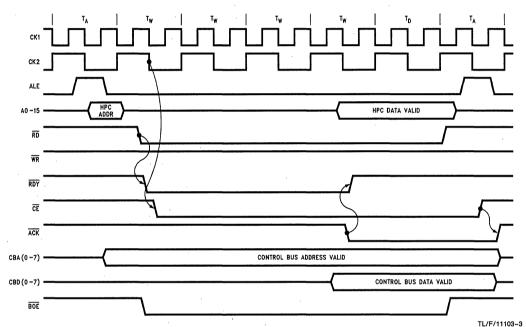

| AN-736 Interfacing the HPC46064 to the DP83200 FDDI Chip Set              | 4-66           |

| AN-678 BMAC Device Software Design Guide                                  | 4-72           |

| AN-689 BMAC Device Hardware Design Guide                                  | 4-78           |

| AN-730 BSI Device Software Design Guide                                   | 4-99<br>4-109  |

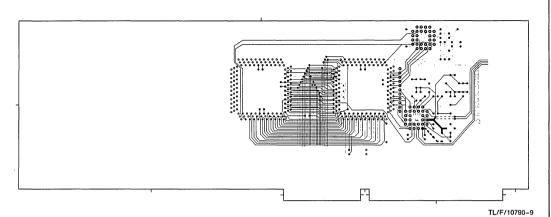

| AN-674 Layout Recommendations for a System Using National's FDDI Chip Set | 4-109<br>4-150 |

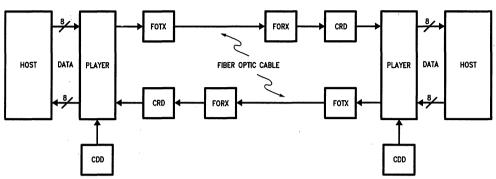

| SB-107 High-Speed, Point-to-Point, Fiber, Data Communication              | 4-150          |

| SB-112 FDDI Concentrator                                                  | 4-160          |

| SB-115 An FDDI-Ethernet Router                                            | 4-163          |

| SB-116 FDDI-Adapter Card                                                  | 4-165          |

| Section 5 Appendix/Physical Dimensions                                    |                |

| FDDI and Networking Acronyms                                              | 5-3            |

| Glossary of Terms for FDDI                                                | 5-4            |

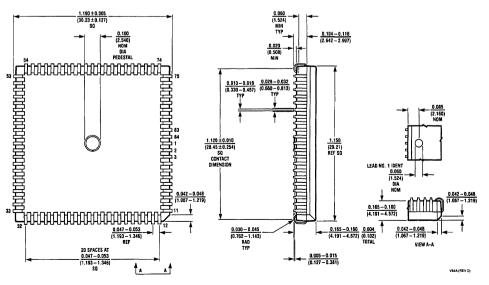

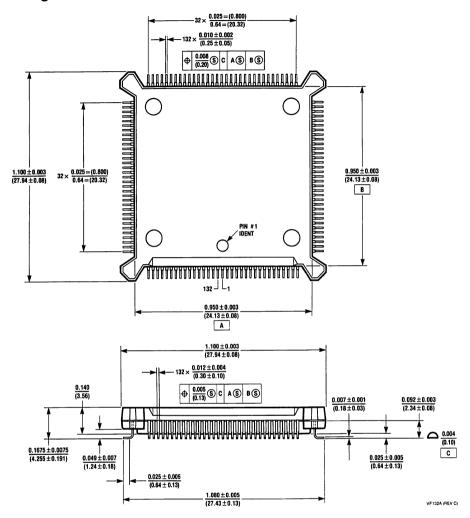

| Physical Dimensions                                                       | 5-7<br>5-7     |

| Bookshelf                                                                 | ٠,             |

| Distributors                                                              |                |

# Alpha-Numeric Index

| An Overview of FDDI: The Fiber Distributed Data Interface                        | 1-3   |

|----------------------------------------------------------------------------------|-------|

| AN-674 Layout Recommendations for a System Using National's FDDI Chip Set        | 4-109 |

| AN-675 Designing FDDI Concentrators                                              | 4-3   |

| AN-678 BMAC Device Software Design Guide                                         | 4-72  |

| AN-679 Point-to-Point Fiber Optic Links                                          |       |

| AN-689 BMAC Device Hardware Design Guide                                         | 4-78  |

| AN-726 Station Management Simplified                                             |       |

| AN-727 A Guide to the Implementation of Physical Connection Management           | 4-46  |

| AN-728 FDDI Station Management with the National Chip Set                        |       |

| AN-730 BSI Device Software Design Guide                                          |       |

| AN-736 Interfacing the HPC46064 to the DP83200 FDDI Chip Set                     | 4-66  |

| AN-740 Incorporating FDDI MAC Level Bridging                                     |       |

| AN-741 Differentiating FDDI Concentrators                                        | 4-11  |

| DP83200EB FDDI AT Evaluation Kit                                                 |       |

| DP83200SMT XLNT Manager FDDI Station Management (SMT) Software Support Package . |       |

| DP83231 CRD Device (FDDI Clock Recovery Device)                                  |       |

| DP83241 CDD Device (FDDI Clock Distribution Device)                              |       |

| DP83251 PLAYER Device (FDDI Physical Layer Controller)                           | 2-36  |

| DP83255 PLAYER Device (FDDI Physical Layer Controller)                           | 2-36  |

| DP83261 BMAC Device (FDDI Media Access Controller)                               |       |

| DP83265 BSI Device (FDDI System Interface)                                       | 2-260 |

| FDDI and Networking Acronyms                                                     | 5-3   |

| Glossary of Terms for FDDI                                                       |       |

| SB-107 High-Speed, Point-to-Point, Fiber, Data Communication                     |       |

| SB-112 FDDI Concentrator                                                         | 4-160 |

| SB-115 An FDDI-Ethernet Router                                                   | 4-163 |

| SB-116 FDDI-Adapter Card                                                         | 4-165 |

Section 1

FDDI Overview

#### **Section 1 Contents**

# An Overview of FDDI: The Fiber Distributed Data Interface

FLOYD E. ROSS

Abstract—Fiber Distributed Data Interface (FDDI), which employs an optical fiber medium, is a 100 Mbit/s local area network (LAN) based on a token ring protocol. Updating earlier efforts on this subject by the author and others, this paper presents an overview of this technology and explores the basis for its success. Particular emphasis is placed on the technical specifications for an upwards-compatible version of FDDI, FDDI-II, which adds the capability for circuit-switched services to the packet services of the basic FDDI, thus creating an integrated services LAN.

#### I. Introduction

The Fiber Distributed Data Interface (FDDI) is a 100 Mbit/s local area network (LAN). Using optical fiber as the medium, the FDDI protocol is based on a token ring access method. FDDI is being developed in Accredited Standards Committee (ASC) X3T9—chartered to develop computer input/output (I/O) interface standards. In the late 1970's, ASC X3T9 recognized the need for a new I/O channel standard as an alternative to Federal Information Processing Standards (FIPS) 60–63. By late 1982, work had been started on FDDI in the ASC X3T9.5 technical committee. In mid-1983, two proposals encompassing the Physical layer and the Media Access Control for FDDI were submitted by Sperry.

Through this same time period, the Institute of Electrical and Electronics Engineers (IEEE) P802 standards project was developing local area network (LAN) standards with data rates up to 20 Mbits/s. FDDI followed the packet data architectural concepts of IEEE P802 and chose the emerging 4 Mbits/s token ring protocol of IEEE P802.5 as the starting point for the FDDI protocol. These choices placed FDDI in an ideal position to be both the backbone network and the follow-on network to the IEEE P802 LAN's.

Meanwhile, in another standards arena, the Open Systems Interconnection (OSI) model had been put in place. This layered the design of computer interconnections, allowing the development of separate standards for the different layers, and provided the proper framework for the development of a set of FDDI standards.

Another factor of significance in the development of FDDI was an increased use of high-performance video workstations for a variety of applications. These brought an emphasis on facilitating low-cost implementations.

Driven by these forces, FDDI grew from the original Sperry proposals to satisfy the needs of many applications, including the back-end (I/O channel) interface, LAN backbone, and front-end high-performance LAN applications. In the course of its development, each new wave of supporters

Manuscript received May 15, 1988; revised March 1, 1989. The author is with UNISYS, Malvern, PA 19355. IEEE Log Number 8929561.

© 1990 IEEE. Reprinted, with permission, from IEEE Journal on Selected Areas in Communications, Volume 7, Issue 7, pps 1043-1051, Sept 1989.

brought new demands which, in turn, were accommodated by the emerging FDDI standards. As a result, the set of services offered by FDDI is broad enough to allow individual optimization of FDDI networks to satisfy the needs of diverse environments.

One enhancement, FDDI-II, will offer significantly increased services by integrating circuit-switched data traffic capabilities into what had originally been strictly a packet LAN. The impetus for FDDI-II came from the new generation of digital PBX's of the early 1980's. Their needs were similar to those of many real-time applications including digital voice and video networks as well as sensor and control data streams. All of these disciplines contributed to the emerging FDDI-II design definition which began in late 1984.

#### A. OUTLINE OF PAPER

Section II of this paper addresses several issues of overall significance to FDDI. Section III describes general FDDI characteristics, with the Physical layer, MAC layer, and SMT operation more fully described in Sections IV, V, and VI, respectively. Section VII supplies an overview of FDDI-II concepts, with Section VIII providing details on FDDI-II operation. The status of the FDDI standardization effect is covered in Section IX.

#### II. FDDI as the Solution

The widespread acceptance of FDDI has been due to a number of factors. The IEEE P802 effort provided several medium-speed (1–20 Mbit/s) LAN's. In effect, IEEE P802 popularized the LAN, and by doing so, created a market for a higher speed LAN to perform the backbone function for lower speed IEEE 802 LAN's and to satisfy applications that require a higher performance LAN.

Contributing also to the acceptance of FDDI is the dramatic improvement in the price and performance characteristics of optical fiber and related components such as optical transmitters and receivers. With the many other advantages that the use of optical fiber offers—high data bandwidth, security, safety, immunity to electromagnetic interference, and reduced weight and size—the concept of an all-fiber LAN was most attractive. Because the FDDI design has been optimized to the use of optical fiber since its inception, FDDI is now in a leadership role in the development of optical fiber LAN technology.

FDDI has maximized the value of standardization. The true value of standards is being recognized in all market-places—from the individual customer to multi-national corporations and the federal government. With emphasis firmly on standards, FDDI has conformed to the ISO Model. The rich functionality that has been integrated into FDDI to meet the needs of a number of market segments means that it can be the one standard satisfying the requirements of the broad, high-speed LAN marketplace. The value of one high-speed optical fiber LAN standard is immense.

#### A. ADVANTAGES OF A RING DESIGN

No paper on FDDI would seem complete without at least a cursory summary of the advantages that a ring design offers. A ring can be shown to offer superior reliability, availability, and serviceability, even in the face of physical damage to the network. A ring topology can be designed to be capable of continued operation despite any projected failure.

Other advantages include the interconnect simplicity of the physical hardware at the interface level. The point-to-point connections around the ring not only provide an easy focus of standardization, but also allow different ring links to have different characteristics and optimization points. Optical fiber, which does not adapt well to bus configurations, can be easily accommodated. Optical fiber has sufficient bandwidth that bit-serial transmission may be used, thus significantly reducing the size, cost, and complexity of the hardware required by a network.

Ring topologies offer advantages in the ease of initial configuration and reconfiguration as the network requirements change. Failing stations or fiber links can be isolated through the use of appropriate protocols. These protocols also provide for the logical addition and deletion of stations without detrimental effects on existing ring traffic. Actual physical addition or removal of stations from the network is also facilitated because ring initialization, failure isolation, recovery, and reconfiguration mechanisms can provide for continued operation even while the cables are being rearranged.

Ring topologies inherently impose no restrictive logical limit on the length of ring links, the number of stations, or the total extent of the network that can be accommodated.

Ring topologies, and the protocols supported by them, offer significant performance advantages. These include insensitivity to load distribution, the ease of fairly allocating the available bandwidth, low arbitration times, bounded access delay, and no requirement for long preambles.

In today's technology, a ring topology appears to best satisfy the requirements of high-performance networks operating from 20 to 500 Mbits/s where high connectivity and large extents are required. Some of the references, and in particular [10], are recommended for an in-depth review of the advantages that a ring design offers.

#### **III. FDDI Characteristics**

The initial version of FDDI uses optical fiber with light-emitting diodes (LED's) transmitting at a nominal wavelength of 1325 nm over multimode fiber. Connections between stations are made with a dual fiber cable employing a polarized duplex connector. A single-mode fiber (SMF) version of Physical Layer Medium Dependent (PMD) uses laser diode transmitters, with two power levels categories specified, the lower of which retains the same receivers as the basic PMD. SMF-PMD will allow individual links to be extended up to 60 or possibly even 100 km.

The data transmission rate is 100 Mbits/s. The effective sustained data rate at the data link layer can be well over 95 percent of this peak rate. The four out of five code used on the optical fiber medium requires a 125 Mbaud transmission rate. The nature of the clocking, which adjusts for accumulated jitter between frames, limits frames to 4500 octets maximum. Multiple frames may, however, be transmitted on the same access opportunity.

A total of 1000 physical connections and a fiber path of 200 km have been used as the basis for calculation of the default values of the recovery timers. Considering reconfiguration requirements, these choices allow a maximum configuration of 500 stations (each station represents two physical connections) linked by 100 km duplex cable. The choice of longer times than the default values for the recovery timers will allow larger networks to be configured. For smaller networks, performance can be optimized by choosing shorter times for the recovery timers. There is no minimum configuration requirement.

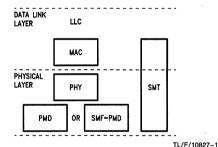

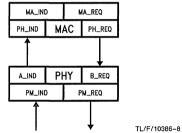

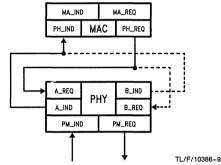

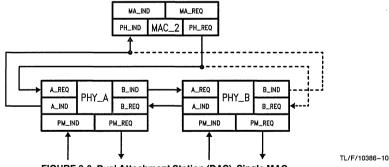

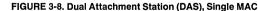

#### A. STATION ORGANIZATION

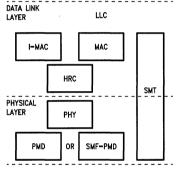

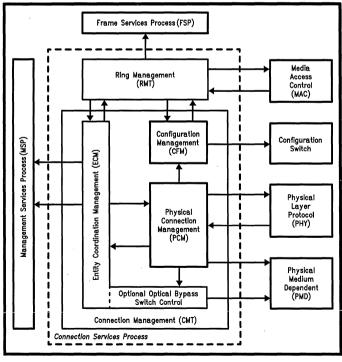

Figure 1 shows the component entities necessary for an FDDI station. Identified components, conforming to both the IEEE 802 structure and the OSI concept of layering, are: Station Management (SMT), which specifies the local portion of the network management application process, including the control required for the proper internal configuration and operation of a station in an FDDI ring; Media Access Control (MAC), which specifies the lower sublayer of the data link layer, including the access to the medium, addressing, data checking, and data framing; Physical Layer Protocol (PHY), which specifies the upper sublayer of the physical layer, including the encode/decode, clocking and framing for transmission; and Physical Layer Medium Dependent (PMD), which specifies the lower sublayer of the physical layer, including power levels and characteristics of the optical transmitter and receiver, interface optical signal requirements, the connector receptacle footprint, the requirements of confirming optical fiber cable plants, and the permissible bit error rates. Two alternative versions of PMD are shown; the basic PMD and SMF-PMD which allows the use of single-mode optical fiber.

FIGURE 1. FDDI Relationship to OSI Model

FDDI MAC provides a superset of the services required by the Logical Link Control (LLC) protocol developed by IEEE P802.2. Figure 1 assumes the use of the IEEE 802.2 LLC as the upper sublayer of the data link layer. Any other appropriate LLC may be used.

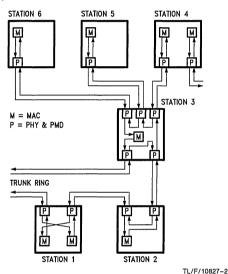

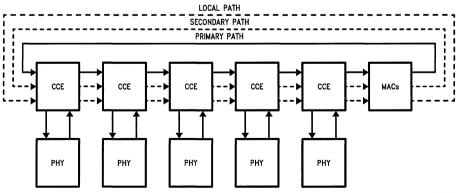

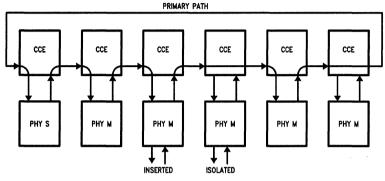

These basic component entities allow a variety of station types as shown in the FDDI topology example of *Figure 2*. As shown, the FDDI trunk ring consists of a pair of counterrotating rings. Two main classes of stations, depending on whether or not they are allowed to attach directly to the trunk ring, as specified. A dual attachment station has two PHY entities. It may attach directly to the trunk ring or indirectly via a concentrator. It may have one or more MAC entities. In the case of two MAC entities, one may be in each of the counterrotating rings or both may be in the same ring. A dual attachment station may have optical bypass switches to remove it from both rings, at the same time healing them, if the station is powered down or disabled by SMT.

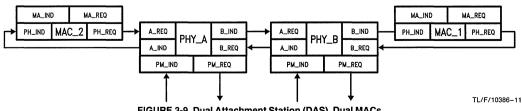

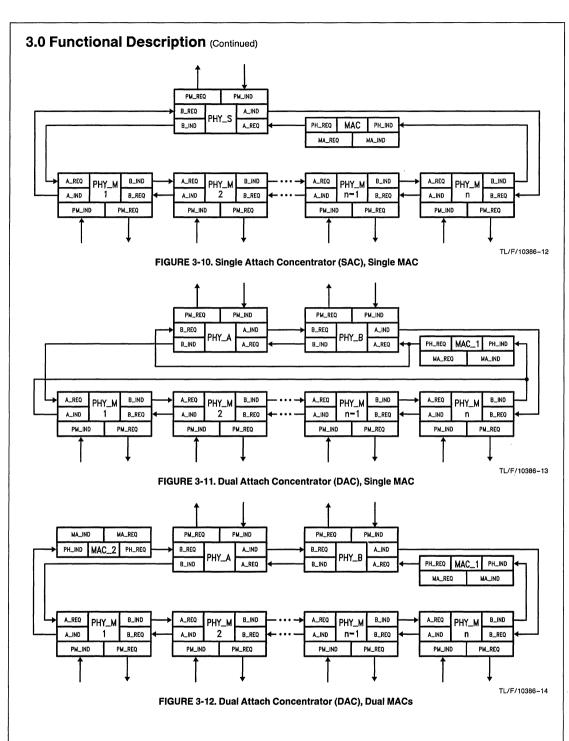

A single attachment station has one PHY and one MAC, and therefore cannot be attached directly into the main FDDI ring. Instead, it must be attached to the ring via a concentrator. A concentrator is a special station that has extra PHY's used to attach other stations that are to be inserted into the main FDDI ring. Varying levels of functionality, including multiple MAC's, are permitted in concentrators.

In Figure 2 stations 1, 2, and 4 are dual attachment stations. Station 3 is a concentrator connecting stations 4, 5, and 6 into the FDDI ring. Stations 5 and 6 are single attachment stations. Station 4, even though it is a dual attachment station, must perform as a single attachment station insofar as its attachment to the ring via the concentrator is concerned. Operation of the second PHY of station 4 on some other ring is allowed, but there must not be any interconnection of the two rings within this station at a level visible to MAC or PHY

FIGURE 2. FDDI Topology Example

TL/F/10827-3

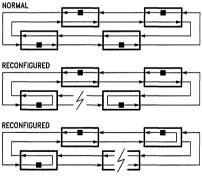

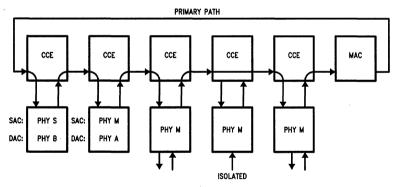

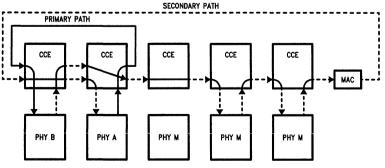

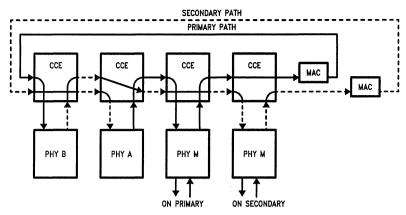

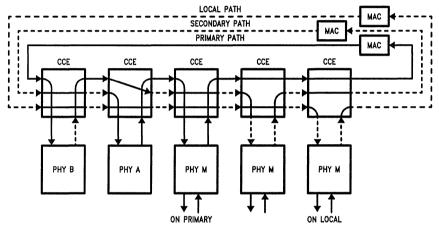

FIGURE 3. Reconfiguration of Counterrotating Rings

#### **B. RELIABILITY PROVISIONS**

Ring topologies allow for the isolation of failing attachments through several mechanisms. Counterrotating rings, as shown in *Figure 3*, are basic to the FDDI structure. The counterrotating ring concept uses two rings connected to

each station or concentrator—one clockwise and the other counterclockwise. When a failure in a link occurs, the stations on either side reconfigure internally as shown in the middle diagram. The functional stations adjacent to the break make use of the connection in the reverse direction to close the ring, thus eliminating the bad link. In this figure, the dark squares represent the logical (MAC) attachment within the stations. Should a station itself fail, as shown in the bottom diagram of this figure, the stations on either side reconfigure to eliminate the failing station and both of the links to it

Stations may offer a bypass capability, whereby an optical switch is used to bypass a station's receiver and transmitter connections so that the signal from the previous station is passed directly to the next station. Bypassing may be activated by a station itself, at the instigation of its neighbor, by a human operator, automatically at the removal of power, or by some overall network-controlling function.

Yet another approach is the use of concentrators, as shown in *Figure 2*, that are attached directly to the trunk ring and, in turn, provide drop connections for a number of stations—in this case, stations 4, 5, and 6. A concentrator may then monitor all of its slave stations and isolate any faulty station. It may also provide for the graceful logical insertion and removal of stations from the ring.

**TABLE I. Symbol Coding**

| Decimal | Code<br>Group | Symbol | Name      | Assignment         |  |  |  |  |

|---------|---------------|--------|-----------|--------------------|--|--|--|--|

| 00      | 00000         | Q      | QUIET     | Line State Symbol  |  |  |  |  |

| 31      | 11111         | 1      | IDLE      | Line State Symbol  |  |  |  |  |

| 04      | 00100         | Н      | HALT      | Line State Symbol  |  |  |  |  |

| 24      | 11000         | J      |           | Starting Delimiter |  |  |  |  |

| 17      | 10001         | K      |           | Starting Delimiter |  |  |  |  |

| 05      | 00101         | L      |           | Starting Delimiter |  |  |  |  |

| 13      | 01101         | Т      |           | Ending Delimiter   |  |  |  |  |

| 07      | 00111         | R      | RESET     | Control Indicator  |  |  |  |  |

| 25      | 11001         | S      | SET       | Control Indicator  |  |  |  |  |

| 30      | 11110         | 0      |           | Data Symbol 0000   |  |  |  |  |

| 09      | 01001         | 1      |           | Data Symbol 0001   |  |  |  |  |

| 20      | 10100         | 2      |           | Data Symbol 0010   |  |  |  |  |

| 21      | 10101         | 3      |           | Data Symbol 0011   |  |  |  |  |

| 10      | 01010         | 4      |           | Data Symbol 0100   |  |  |  |  |

| 11      | 01011         | 5      |           | Data Symbol 0101   |  |  |  |  |

| 14      | 01110         | 6      |           | Data Symbol 0110   |  |  |  |  |

| 15      | 01111         | 7      |           | Data Symbol 0111   |  |  |  |  |

| 18      | 10010         | 8      |           | Data Symbol 1000   |  |  |  |  |

| 19      | 10011         | 9      |           | Data Symbol 1001   |  |  |  |  |

| 22      | 10110         | Α      |           | Data Symbol 1010   |  |  |  |  |

| 23      | 10111         | В      |           | Data Symbol 1011   |  |  |  |  |

| 26      | 11010         | С      |           | Data Symbol 1100   |  |  |  |  |

| 27      | 11011         | D      |           | Data Symbol 1101   |  |  |  |  |

| 28      | 11100         | Е      |           | Data Symbol 1110   |  |  |  |  |

| 29      | 11101         | F      |           | Data Symbol 1111   |  |  |  |  |

| 01      | 00001         | ٧      | Violation | Not Transmitted    |  |  |  |  |

| 02      | 00010         | ٧      | Violation | Not Transmitted    |  |  |  |  |

| 03      | 00011         | ٧      | Violation | Not Transmitted    |  |  |  |  |

| 06      | 00110         | V      | Violation | Not Transmitted    |  |  |  |  |

| 08      | 01000         | V      | Violation | Not Transmitted    |  |  |  |  |

| 12      | 01100         | V      | Violation | Not Transmitted    |  |  |  |  |

| 16      | 10000         | V      | Violation | Not Transmitted    |  |  |  |  |

The use of all three techniques allows FDDI networks to be configured to tolerate a variety of station or link failures and physical network configurations without catastrophic consequences. When failures occur, the network automatically reconfigures, eliminating any failing element and maintaining ring operation. Continuous monitoring of the failed link or station allows the network to automatically reconfigure and restore normal operation when repair is effected. Any of these reconfigurations may result in the loss of individual frames, which then need to be retransmitted.

#### C. DATA ENCODING

Information on the medium uses a four out of five group code, with each code group called a symbol. As shown in Table I, in the 32-member symbol set, 16 symbols are data symbols, each representing four bits of ordered binary data. Three symbols are used for line-state signaling which is recognized by the physical layer hardware, two are used as control indicators, and four are used for starting and ending delimiters. One of the starting delimiters (L) is not used in the basic FDDI, but is reserved for FDDI-II. The remaining seven symbols of the symbol set are not to be transmitted since they violate code run length and dc balance requirements. The QUIET symbol is a necessary member of the line-state symbol set since it is used to indicate the absence of any functional signal.

#### D. FRAME AND TOKEN FORMATS

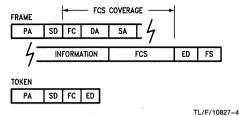

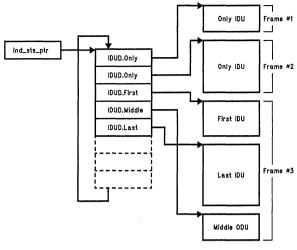

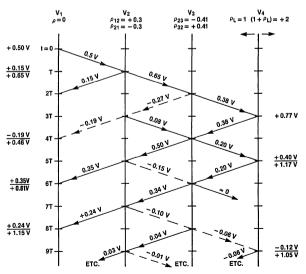

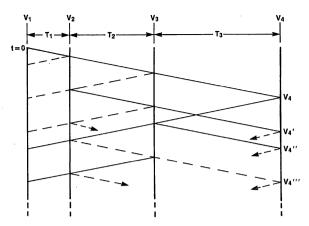

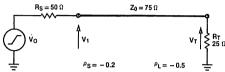

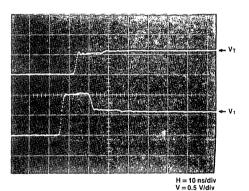

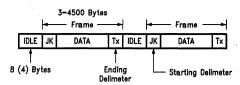

Information is transmitted on the FDDI ring in frames which are variable in length. Tokens are special short fixed-length "frames" that are used to signify the right to transmit data. Figure 4 shows the frame and token formats.

The Preamble (PA) field, consisting nominally of 16 IDLE symbols (a maximum frequency signal that is used for establishing and maintaining clock synchronization), precedes every transmission. The Starting Delimiter (SD) field consists of a two-symbol sequence (JK) that is uniquely recognizable independent of previously established symbol boundaries. The SD establishes the symbol boundaries for the content that follows.

The Frame Control (FC) is a two-symbol field that defines the type of frame and its characteristics. It distinguishes between synchronous and asynchronous frames, the length of the address field (16 or 48 bits), and the kinds of frame (e.g., LLC or SMT). One set of FC values is reserved for implementer frames that have no defined format and are to be repeated unchanged by all conforming FDDI stations. The FC field also provides for two kinds of tokens, restricted and nonrestricted. The latter is used in a special class of service which provides for extended dialogs among a limited set of cooperating stations. Two Ending Delimiter (ED) symbols (TT) complete a token.

The Destination Address (DA) and Source Address (SA) fields may be either 16 or 48 bits long, depending on the FC value. DA may be either an individual or a group address, the latter of which has the potential to be recognized by more than one station.

The 32-bit Frame Check Sequence (FCS) field is a cyclic redundancy check using the standard polynomial used in the IEEE 802 protocols. The information field of a frame, like the other fields covered by the FCS check, consists only of data symbols. Data symbols are not used in fields not covered by the FCS check.

The ED field of a frame is one delimiter symbol (T). It is followed by the Frame Status (FS) field that has a minimum of three control indicator symbols that are modified by the

station as it repeats the frame. These indicate, when set, that an error has been detected in the frame by the station, that the addressed station has recognized its address, and that the frame has been copied by the station.

FIGURE 4. Frame and Token Formats

# IV. Physical Layer (PHY and PMD) Operation

PHY provides the protocols and PMD the optical fiber hardware components that support a link from one FDDI station to another. PHY simultaneously receives and transmits. The transmitter accepts symbols from MAC, converts these to five-bit code groups, and transmits the encoded serial data stream on the medium.

The receiver recovers the encoded serial data stream from the medium, establishes symbol boundaries based on the recognition of a start delimiter, and forwards decoded symbols to MAC. Additional symbols (QUIET, IDLE, and HALT) are interpreted by PHY and used to support SMT functions.

PHY also provides the bit clocks for each station. The total ring, including all stations and links, must remain the same apparent bit length (i.e., no bits may be created or deleted) during the transmission of a frame around the ring. Otherwise, an error would be generated in the frame as it is repeated around the ring. In the face of jitter, voltage, temperature, and component aging effects, such stability can only be realized through special provision. PHY provides an elasticity buffer which is always inserted between the receiver and the transmitter. The receiver employs a variable frequency clock, using standard techniques such as a phaselocked loop oscillator, to recover the clock of the previous transmitting station from the received data. The transmitter. in contrast, uses a local fixed-frequency clock. The elasticity buffer in each station compensates for the difference in frequency between the local clock and that of the upstream station by adjusting the bit delay through the station. The elasticity buffer in each station is reinitialized to its center position during the preamble (PA) that precedes each frame or token. This has the effect of increasing or decreasing the length of the PA, which is initially transmitted as 16 or more symbols, as it proceeds around the ring.

The transmitter clock has been chosen with 0.005 percent stability. With a minimum elasticity buffer of 10 bits, frames of up to 4500 octets in length can be transmitted without exceeding the limits of the elasticity buffer.

Simulations of early FDDI designs, presented to the technical committee, showed that rather than maintaining a nominal 16 symbol PA length, there was a tendency for the PA lengths in long rings to move toward a flat unbounded distribution. Longer PA's created no problem by themselves, but came at the expense of shorter, or even negative, length PA's. A negative PA indicates that the PA has been so severely shortened that it has completely disappeared and that symbols have consequently been lost off the end of a frame, resulting in the loss of the entire frame. This problem

was solved by means of a smoothing buffer function incorporated into PHY. This examines the PA length between frames and either inserts or deletes, as the case may be, preamble symbols (or bytes) in order to maintain the PA near the nominal 16 symbol length, thus ensuring that the preamble never decreases below 4 or 5 bytes. Simulation work presented to the technical committee showed that the algorithm chosen, even under worst case conditions, reduced the probability of frame loss to less than  $10^{-12}$ . Later work presented to the technical committee has reaffirmed this result with extended testing of a large physical ring configuration.

# V. Token MAC Functional Operation

A major function of any station is deciding which station has control of the medium. MAC schedules and performs all data transfers on the ring.

The basic concept of a ring is that each station repeats the frame that it has received from its upstream neighbor to its downstream neighbor. If the destination address (DA) of the frame matches that MAC's address and there is no error indicated, then the frame is copied into a local buffer with MAC notifying LLC (or SMT) of the frame's arrival, MAC modifies the indicator symbols in the FS field of the frame as it repeats it to indicate the detection of an error in the frame, the recognition of its own address, and the copying of the frame. The frame propagates around the ring to the station that originally placed it on the ring. The transmitting station may examine the indicator symbols in the FS field to determine the success of the transmission. The MAC of this transmitting station is responsible for removing from the ring all of the frames that it has placed on the ring (a process termed stripping). MAC recognizes these frames for stripping by the fact that the SA contained in them is its own address. IDLE symbols are placed on the medium during stripping.

If MAC has a frame from LLC (or SMT) to transmit, it may do so only after a token has been captured. A token is a special frame that indicates that the medium is available for use. Priority requirements, necessary to assure the proper handling of frames, are implemented in the rules of token capture. Under these rules, if a given station is not allowed to capture the token, then it must repeat it (or in certain cases reissue a token) to the next station in the ring. Only after having captured a token and stripping it from the ring is MAC allowed to transmit a frame or frames. When finished, MAC issues a new token to signify that the medium is available for use by another station.

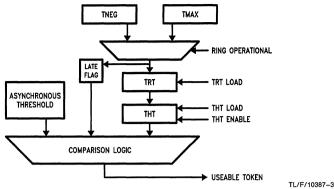

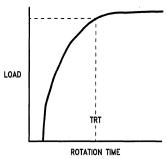

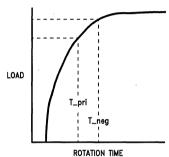

The FDDI MAC uses a Timed Token Rotation (TTR) protocol to control access to the medium. Under this protocol, each station measures the time that has elapsed since a token was last received. The initialization procedures establish the Target Token Rotation Time (TTRT) equal to the lowest value that is bid by any of the stations. Two classes of service are defined. Synchronous service allows use of a token whenever MAC has synchronous frames queued for

transmission. Asynchronous service allows use of a token only when the time since a token last was received has not exceeded the established TTRT. Multiple levels of priority for asynchronous frames may be provided within a station by specifying additional (more restrictive) time thresholds for token rotation.

The use of the TTR protocol imparts some useful operational characteristics. It allows stations to request and establish (via SMT procedures) guaranteed bandwidth and response time for synchronous frames. It establishes a guaranteed minimum response time for the ring because, in the worst case, the time between the arrival of two successive tokens will never exceed twice the value of TTRT. It also provides a guaranteed level of ring utilizations equal to (TTRT-RL)/TTRT where RL is the physical ring latency—essentially the time for a token to propagate around the ring under no load conditions. Reference<sup>[15]</sup> and others by the same author have dealt extensively with these aspects of FDDI operation.

Low values of TTRt (e.g., 4 ms) may be used to establish an average token rotation time of 4 ms and a guaranteed response time not exceeding 8 ms. This would be useful in a time-critical application (e.g., packetized voice). Larger value of TTRT may be used to establish very high ring utilizations under heavy loads. For instance, using TTRT of 50 ms and a ring latency (RL) of 0.25 ms (reasonable for a ring consisting of 75 stations and 30 km of fiber), the above formula shows that a utilization of 99.5 percent can be achieved.

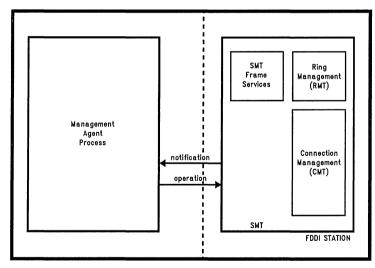

#### VI. Station Management (SMT) Operation

SMT is the local portion of the network management application process, including the control required for proper operation of an FDDI station in an FDDI ring. SMT monitors activity and exercises overall control of station activity. These functions include control and management within a station for such purposes as initialization, activation, performance monitoring, maintenance, and error control. Additionally, SMT communicates with other SMT entities on the network for the purpose of controlling network operation. Examples of these SMT functions include the administration of addressing, allocation of network bandwidth, and network control and configuration.

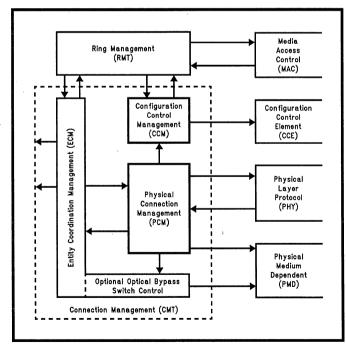

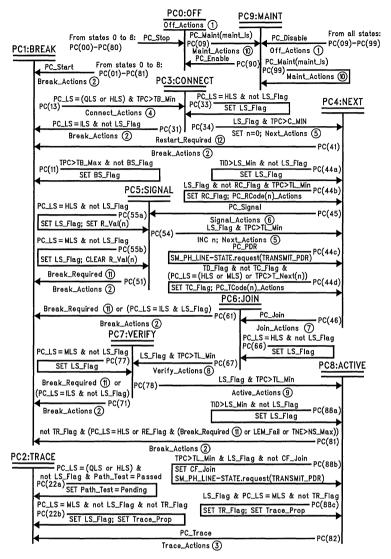

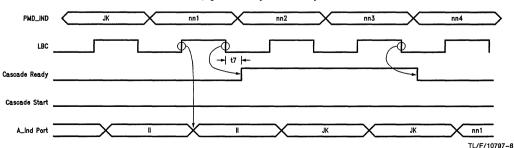

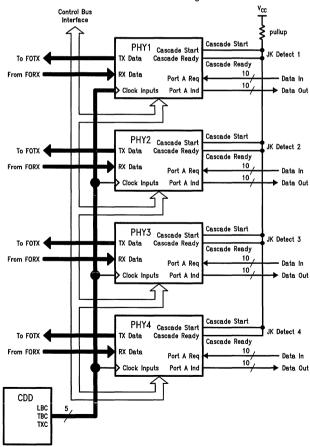

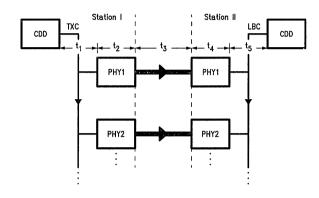

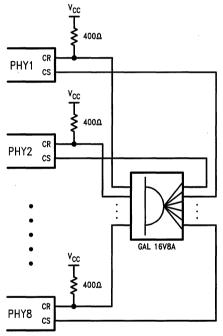

The SMT Connection Management (CMT) function establishes the physical connections between adjacent stations. For this function, CMT uses stream composed of QUIET, HALT, and IDLE symbols in low-level signaling protocols. Once a physical connection is established, CMT creates a logical configuration within the station by activating the appropriate paths between the PHY and MAC entites within that station. A large degree of flexibility is provided in the logical configuration, which may be established consistent with station functionality and desired station personality. This flexibility allows FDDI to support a wide range of topologies and applications.

#### VII. FDDI-II Concepts

FDDI-II is an upward-compatible enhancement of the basic FDDI that adds a circuit-switched service to the existing packet capability.

A packet service is a service where the elements of data to be transferred are placed in frames. Packets may vary in length and are self-defining in that each contains delimiters that mark its beginning and end and an address that specifies the target station. FDDI packets are called frames.

In contrast, a circuit-switched service provides a continuous connection between two or more stations. Instead of using addresses, the connection is established based upon some prior agreement, which may have been negotiated using packet messages or established by some other suitable convention known to the stations involved. This prior agreement typically takes the form of knowing the location of a time slot, or slots, that occur regularly relative to a readily recognizable timing marker.

A common timing marker used in North America is the Basic System Reference Frequency (BSRF), a 125  $\mu s$  clock used by the public networks. Use of this clock is assumed for FDDI-II. In local FDDI usage, this is referred to as the cycle clock and is signaled by the JK starting delimiter of the FDDI-II cycle format.

In FDDI-II, a circuit-switched connection is described as N bits beginning at byte M after the cycle clock marker in Wideband Channel (WBC) number X. The last descriptor is necessary because FDDI-II has 16 WBC's that may be independently assigned to either packet-switched or circuit-switched data. This definition allows connections at data rates of all multiples of 8 kbits/s (i.e., N = 1) up to the 6.144 Mbit/s data rate of a WBC. If need be, multiple WBC's may be used to accommodate higher data rates.

The data transferred in a circuit-switched mode is best described as a stream of data. The data rate is appropriate to the service being provided—with, for example, 64 kbits/s being used for a digital voice data stream. Other data stream rates, even up to many Mbits/s in the case of video, are used for other applications. Once a connection is established, the data rate remains constant.

The contrasting nature of packet-switched and circuit-switched data is of interest. Most packet data traffic occurs in random quantities and at random times. This is referred to as asynchronous traffic. Other packet traffic, more regular in nature and occurring in relatively predictable quantities on a regular time basis, is referred to as synchronous (packet) traffic. In contrast, isochronous data occur in precise amounts on a precise time basis. They typically represent a sequence of digital samples from a sensor (e.g., voice or video). More importantly, isochronous data must be synchronized with clock information to ensure the accurate regeneration of the sampling clock (as distinct from the bit clock) to minimize distortion in data reconstruction. Isochronous data are more easily transferred in a circuit-switched network.

Networks that carry isochronous data must maintain precise synchronism with the cycle clock. For the FDDI ring, this means that one station (called the cycle master) must insert a delay, for all isochronous data so that the ring appears to be an exact multiple of 125  $\mu s$  in length. FDDI incorporates this delay in the cycle master in such a way that it does not

cause any delay in the packet traffic. This is essential in providing an integrated services network with acceptable packet service.

#### VIII. FDDI-II Operation

Figure 5, much like Figure 1, shows how FDDI-II is implemented using one additional standard—Hybrid Ring Control (HRC). HRC becomes the new lowest sublayer of the data link layer, taking its place between MAC and PHY. HRC multiplexes data between the (packet) MAC and the isochronous MAC (I-MAC). This requires that the (packet) MAC be able to transmit and accept data on a noncontinuous basis because packet data are interleaved with isochronous data.

FDDI-II is a network with 100 Mbits/s of bandwidth available. This bandwidth may be devoted totally to operation as a packet network. Alternatively, portions of this bandwidth, in units of WBC's, may be dynamically separated for use with circuit-switched data. Up to 16 WBC's may be assigned. Each WBC is 6.144 Mbits/s, which is four times the North American and three times the European basic access rate to the telephone network. WBC's are full duplex and are independently allocatable and deallocatable. In effect, a broadband circuit capability has been provided with 16 available channels.

TL/F/10827-5

#### FIGURE 5. FDDI-II Relationship to OSI Model

The WBC's provide a bandwidth division mechanism between the packet and isochronous traffic with a granularity of 6.144 Mbits/s. The allocation of virtual services within the isochronous traffic is allowed with an 8 kbit/s granularity. Once a station has been assigned a WBC or a number of WBC's, that station may suballocate the combined bandwidth of these WBC's as required. This suballocation may be in terms of any multiples of 8 kbit/s subchannels, including the commonly used 16, 32, 64 (B channel), 384, 1536, 1920, and 2048 kbit/s subchannels. Mixtures of these data rates in the same WBC are allowed. If preferred, the aggregate of any or all of the allocated WBC's may be used as one virtual service, satisfying the needs of such applications as high-resolution video. Thus, a multiplicity of virtual circuits may be provided within the same FDDI-II ring.

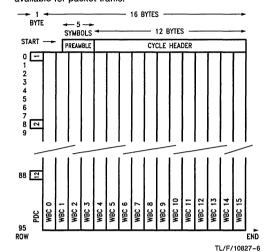

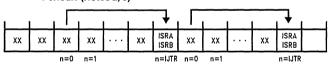

Assignment of all 16 WBC's, each at 6.144 Mbits/s, yields a total bandwidth of 98.304 Mbits/s. After allowance for the preamble and the cycle header, if all WBC's were allocated, a residual 768 kbit/s channel would then be left for packet traffic. This bandwidth, consisting of 12 bytes every cycle (125 ms), known as the Packet Data Group (PDG), is inter-

leaved with the 16 WBC's as shown in Figure 6. The order of transmission is left to right by row starting with the top row. Data steering logic in HRC augments the PDG with the bandwidth of any WBC's that are not assigned. Each WBC is one of the columns in Figure 6 and represents a bandwidth of 6.144 Mbits/s or 96 bytes per cycle. This is an efficient system that allows the bandwidth of all unallocated WBC's to be used by the packet channel. Thus, for example, with eight (i.e., one-half) of the WBC's assigned to isochronous service, 49.92 Mbits/s of bandwidth would be available for packet traffic.

#### FIGURE 6. FDDI-II Cycle Format

A ring is initialized in basic (token) mode and switched to a hybrid mode of operation, combining both packet-switched and circuit-switched data capabilities, only after a station has negotiated for and won the right to be cycle master and has the synchronous bandwidth allocation required to support it. This cycle master then generates cycles at an 8 kHz rate (every 125  $\mu$ s) and inserts the latency required to maintain an integral number of cycles synchronously on the ring. Alternative designs may allow the ring to be initialized directly in hybrid mode.

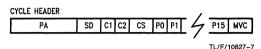

The cycle header format is shown in *Figure 7*. It follows the Preamble (PA) which is nominally five symbols long. The Starting Delimiter (SD) is the same symbol pair (JK) used as the SD for frames when FDDI is operating in basic mode. In hybrid mode, frames use an IL symbol pair, readily recognized in the rigidly formatted context of hybrid mode, as their starting delimiter. The Cycle Sequence (CS) byte provides a modulo 192 cycle sequence count. The Maintenance Voice Channel (MVC) byte provides a 64 kbit/s voice channel for maintenance purposes.

The 16 symbols of programming information (P0-P15) determine whether the corresponding WBC (0-15) is allocated to packet or isochronous traffic. Thus, each of these (Pn) controls the multiplexing of one of the columns (WBCn) shown in *Figure 6*. The C1 and C2 symbols are used for synchronization control in the transfer of this programming information to the other stations by the cycle master.

#### A. FDDI-II PRIORITY LEVELS

Four kinds of traffic may coexist in an FDDI-II ring. Once WBC's have been allocated, the isochronous traffic within them has the highest priority.

Second highest priority is given to synchronous packet traffic where predictable units of data are to be delivered at regular intervals. Delivery is guaranteed with a delay not exceeding twice TTRT. These data may be transmitted following the capture of either a restricted or nonrestricted token.

#### FIGURE 7. Cycle Header Format

The bandwidth required for both isochronous and synchronous traffic is allocated from the available FDDI bandwidth. The allocation algorithm must ensure that the total allocation does not exceed 100 percent. Unallocated bandwidth is used on an as-available basis for asynchronous packet traffic

Third highest priority is given to asynchronous traffic operating in restricted token mode. Such traffic may be transmitted upon the capture of either a restricted or a nonrestricted token. Cooperating stations may enter a restricted token mode of operation, which allows them to issue and use restricted tokens, only after negotiating an agreement using nonrestricted tokens. Restricted token mode operation allows stations to vie for available asynchronous bandwidth on a dialog basis.

Lowest priority is given to asynchronous traffic that may be transmitted only by capturing a nonrestricted token. This mode of operation allows stations to vie for the available asynchronous bandwidth on a single frame basis.

#### **B. FDDI-II APPLICATIONS**

FDDI-II considerably expands the range of applications that may be addressed by FDDI rings. An FDDI-II ring may connect high-performance processors, mass storage systems, high-performance workstations, and perform the backbone function to a number of lower performance LAN's. The same ring may have some of its bandwidth allocated to isochronous services provided by the WBC's. This isochronous bandwidth may in turn be suballocated into a variety of virtual circuit services such as video, voice, and quite possibly, control or sensor data streams. The division of bandwidth between these two kinds of services may be adjusted based on the time of day or other requirements. In practice, no single instance of FDDI connects to all these types of equipment, and certainly not to all the equipment of a large site. Instead, multiple instances of FDDI-II rings will coexist with high traffic units, such as processors, attaching to multiple FDDI networks.

In a packet-switched mode, FDDI can be a backbone for bridges to a variety of other lower-speed LAN's, for example, the various IEEE 802 media access methods. It may also provide a backbone for gateways to the public data networks. In both cases, connections to processors and mass storage subsystems can be provided. Connections to high-performance workstations are likewise provided.

It is anticipated that FDDI-II implementations will follow those of the basic FDDI by one to two years. Committee X3T9.5 has specified the rules of coexistence of these two FDDI implementations to ensure interconnectability and interoperability of FDDI-II implementations operating in basic mode with the basic FDDI implementations. This also allows the use of FDDI-II chips for all applications once they become available.

# IX. FDDI Standards Effort and Status

The FDDI standardization effort is taking place in the ASC X3T9.5 committee which meets bimonthly with an attendance of well over 100. The official voting membership, limited to one per corporation, is approximately 80. Ad hoc working meetings, scheduled as required, are presently focusing on SMT, FDDI-II, and SMF-PMD detail design definitions as well as issues concerning MAC-level bridging.

After completion by ASC X3T9.5, a draft proposed American National Standard (dpANS) is forwarded to ASC X3T9 for a technical letter ballot which approves forwarding to X3. X3 conducts a four-month public review, followed by an X3 letter ballot. Finally, the dpANS is forwarded to the Board of Standards Review (BSR) for formal approval. Upon approval, the standard is given a final editing to conform to ANSI requirements and published.

MAC (Rev. 10) is an American National Standard (ANSI X3.138-1987) and was published in July 1987. Current activities are focused on potential enhancements to MAC, including formalization of the 48-bit addressing structure used in IEEE 802 LAN's, reliability enhancement in the criteria for frame recognition, and incorporation of the FDDI-II requirements.

PHY (Rev. 15) is also an American National Standard (ANSI X3.148-1988) and was published in December 1988.

PMD (Rev. 8), X3.166-198x, completed the X3 four-month public review in late 1987. This initial forwarding had been intended to allow a full set of comments on the optical parameters documented in it. Five sets of comments received resulted in a number of refinements to the optical specifications of PMD. There were also a number of comments on the connector choice and its documentation. In April 1988, X3T9.5 finalized the optical specifications and reaffirmed its connector choice. PMD, having completed a second (two-month) public review in December 1988, is now being processed for final approval as a standard.

Work has progressed smoothly on the SMF-PMD project which was started in mid-1987. An X3T9 technical letter ballot approved the SMF-PMD document (Revision 4) and it has been forwarded to X3 for the four-month public review and final approval as a standard.

The technical definition of FDDI-II, long maintained in a working paper, has now been completed and is contained in Revision 5 of the Hybrid Ring Control (HRC) document. This document also passed an X3T9 technical letter ballot and has also been forwarded to X3 for public review and approval.

Participation in the working meetings on SMT has been high through much of 1987 and into 1989, with well over 100 attendees at the most recent meetings. Representing the meeting ground between the widely differing FDDI implementation and usage philosophies, SMT has proved a difficult task. Contentious items have included the use of concentrators without a MAC, link confidence test duration, physical layer link error monitoring, and physical layer signaling. But the committee's determination to produce an SMT standard assuring interoperability has prevailed and SMT is progressing toward a technical letter ballot in the latter part of 1989.

In a similar process designed to produce technically equivalent ISO standards for FDDI, the FDDI documents are being processed by ISO/IEC JTC1/SC 13. This process has resulted in the approval of MAC (IS 9314-2) and PHY (IS 9314-1) as ISO standards. PMD (DIS 9314-3) has passed the letter ballot for approval as an International Standard with publishing expected in late 1989. SMF-PMD and HRC are currently being processed for submission to ISO.

Led by the ASC X3T9.5, this FDDI standards effort has continued to reflect the FDDI product implementations of its many supporters, including a number of semiconductor manfacturers working towards FDDI chip sets. Several FDDI chip sets available either now or in the near future promise cost-effective implementations of these FDDI standards in the near future.

#### X. Conclusion

FDDI has proved a very successful standardization effort, far more successful than those who conceived it could ever have imagined. Users, system houses, chip designers, and component vendors have come together to produce a set of standards of lasting significance. With the widespread use of the basic FDDI will come a broad based market for FDDI which satisfies the much wider range of requirements typical of voice, video, and sensor/control based data streams.

#### References

- [1] ANSI/IEEE Standard, 802.5-1985, "Token Ring Access Method and Physical Layer Specifications."

- [2] American National Standard, "FDDI Token Ring Media Access Control (MAC)," ANSI X3.139-1987.

- [3] American National Standard, "FDDI Token Ring Physical Layer Protocol (PHY)," ANSI X3.148-1988.

- [4] Draft Proposed American National Standard, "FDDI Token Ring Physical Layer Medium Dependent (PMD)," ACS X3T9.5 Rev. 9, Mar. 1989 (ANSI X3.166-198x).

- [5] Draft Proposed American National Standard, "FDDI Hybrid Ring Control (HRC)," ASC X3T9.5 Rev. 5, Apr. 1989.

- [6] Draft Proposed American National Standard, "FDDI Token Ring Station Management (SMT)," ASC X3T9.5, Rev. 5, May 1989.

- [7] Draft Proposed American National Standard, "FDDI Token Ring Single-Mode Fiber Physical Layer Medium Dependent (SMF-PMD)," ASC X3T9.5 Rev. 4, Apr. 1989.

#### References (Continued)

- [8] F. Ross, "FDDI—A Tutorial," IEEE Commun. Mag., May 1986.

- [9] V. Iyer and S. Joshi, "FDDI's 100-Mbps Protocol Improves on 802.5 spec's 4-Mbps Limit," EDN, May 2, 1985.

- [10] F. E. Ross, "Rings are Round for Good," IEEE Network Mag., Jan. 1987.

- [11] M. J. Johnson, "Reliability Mechanisms of the FDDI High Bandwidth Token Ring Protocol," Comput. Networks ISDN Syst., Vol. II, No. 2, pp. 121–131, 1986.

- [12] H. Salwen, "In Praise of Ring Architecture for Local Area Networks," Comput. Design, pp. 183–192, Mar. 1983.

- [13] R. M. Grow, "A Timed Token Protocol for Local Area Networks," Presented at Electro '82, Token Acess Protocol (17/3), May 1982.

- [14] M. J. Johnson, "Fairness of Channel Access for Non-Time-Critical Traffic Using the FDDI Token Ring Protocol," in *Proc. Seminar Real-Time Local Area Networks*, Bandol, France, Apr. 1986, pp. 145–157.

- [15] \_\_\_, "Proof That Timing Requirements of the FDDI Token Ring PROTocol are Satisfied," *IEEE Trans. Commun.*, vol. COM-35, pp. 620–625, 1987.

- [16] F. E. Ross, "FDDI—A Perspective," in 1988 Fiber Optics Source-Book, 3rd Annu. Ed., pp. 193–210.

- [17] M. J. Johnson, "Analysis of FDDI Synchronous Traffic Delays," in Proc. Syst. Design Networks, Apr. 1988, pp. 65–72.

- [18] \_\_, "Performance Analysis of FDDI," Presented at EFOC/LAN '88, June 1988.

- [19] J. Hamstra, "FDDI Design Tradeoffs," Presented at the 13th Conf. Local Comput. Networks, Oct. 1988.

- [20] W. E. Burr, "The FDDI Optical Data Link," IEEE Commun. Mag., May 1986.

Floyd E. Ross received the B.A. degree in mathematics and physics from Mount Allison University in 1955 and did postgraduate work at McMaster University, Hamilton, Ont., Canada.

He is a Staff Engineer with UNISYS, Devon, PA, with responsibilities in communications networks and in LAN definition and implementation. He is an active contributor to accredited standards committee X3T9 on I/O Interfaces and to IEEE 802. He is Vice Chairman of X3T9.5 and has been the leader of the FDDI standards development effort since its inception in that committee. He has chaired many of the FDDI working meetings including those on SMT and FDDI-II and is technical editor of the four basic FDDI standards. He has also presented and authored a number of papers on both local area networks and FDDI.

|  |  | 4 |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

Section 2

DP83200 FDDI Chip Set

#### **Section 2 Contents**

| DP83231 CRD Device (FDDI Clock Recovery Device)                | 2-3   |

|----------------------------------------------------------------|-------|

| DP83241 CDD Device (FDDI Clock Distribution Device)            | 2-18  |

| DP83251/DP83255 PLAYER Device (FDDI Physical Layer Controller) | 2-36  |

| DP83261 BMAC Device (FDDI Media Access Controller)             | 2-130 |

| DP83265 BSI Device (EDDI System Interface)                     | 2-260 |

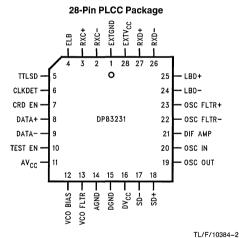

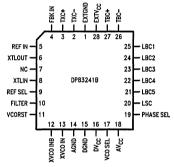

#### DP83231 CRD™ Device (FDDI Clock Recovery Device)

#### **General Description**

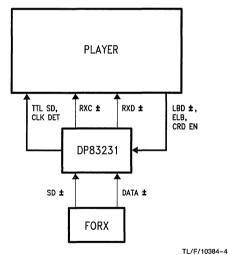

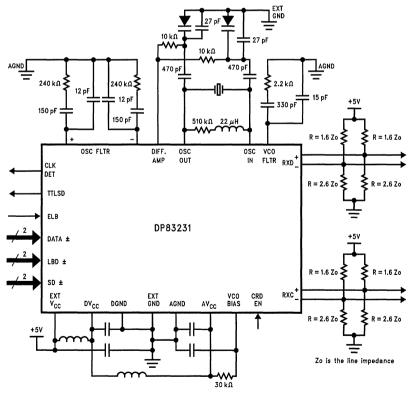

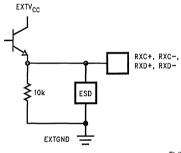

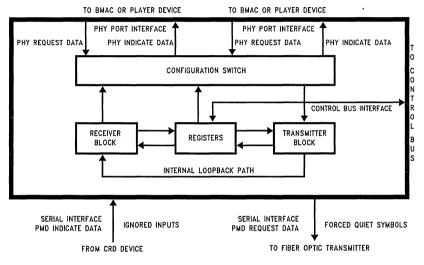

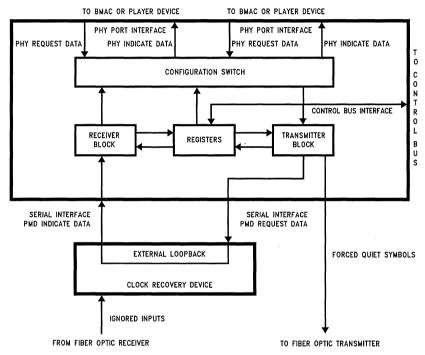

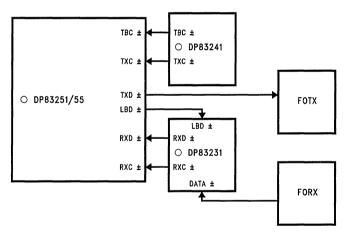

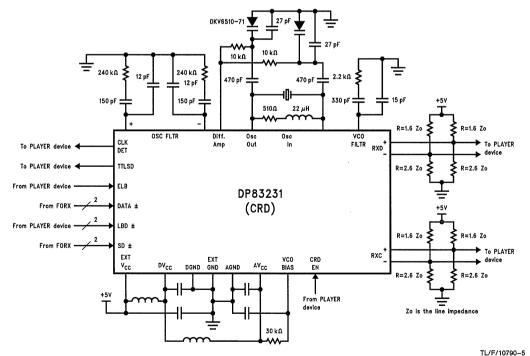

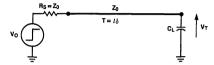

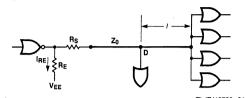

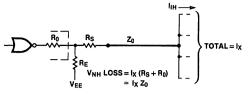

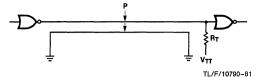

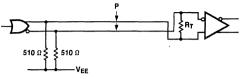

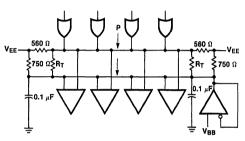

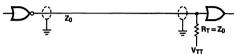

The DP83231 CRD device is a clock recovery device that has been designed for use in 100 Mbps FDDI (Fiber Distributed Data Interface) networks. The device receives serial data from a Fiber Optic Receiver in differential ECL NRZI 4B/5B group code format and outputs resynchronized NRZI received data and a 125 MHz received clock in differential ECL format for use by the DP83251/55 PLAYER™ device.

#### **Features**

- Clock recovery at 100 Mbps data rate

- Internal 250 MHz VCO

- 0.1% VCO operating range

- Crystal controlled

- Precision window centering delay line

- Single +5V supply

- 28-pin PLCC package

- BiCMOS processing

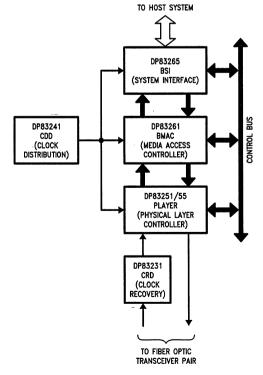

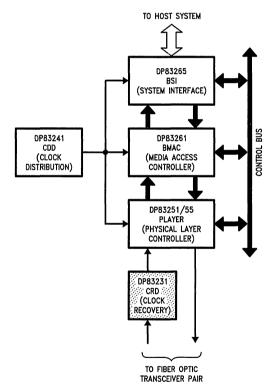

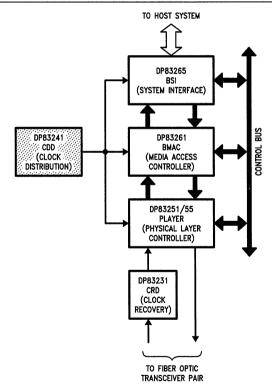

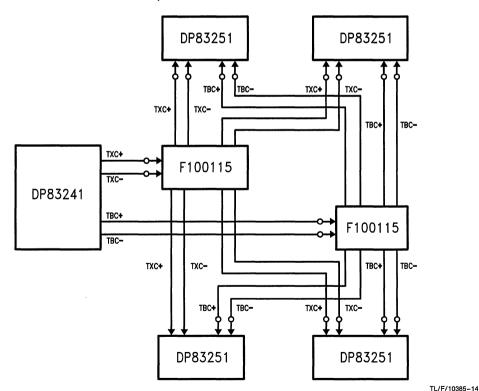

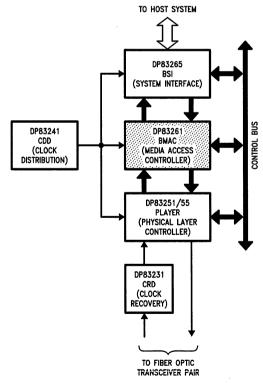

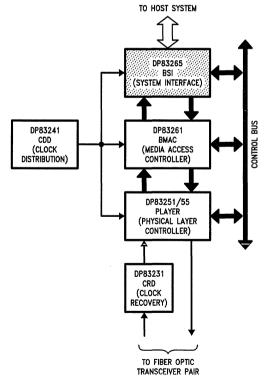

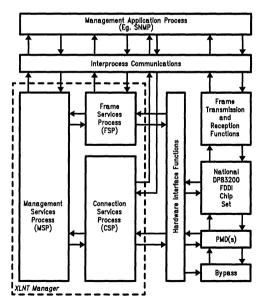

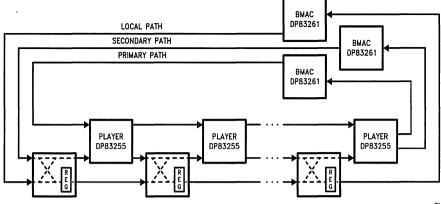

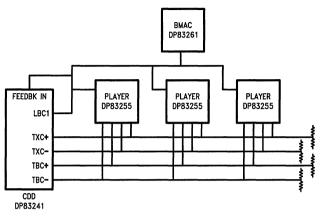

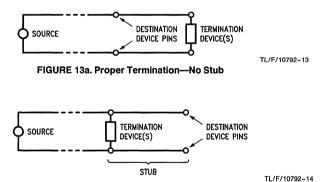

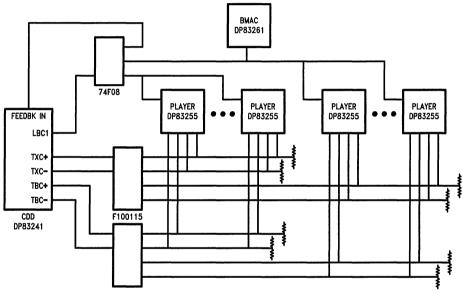

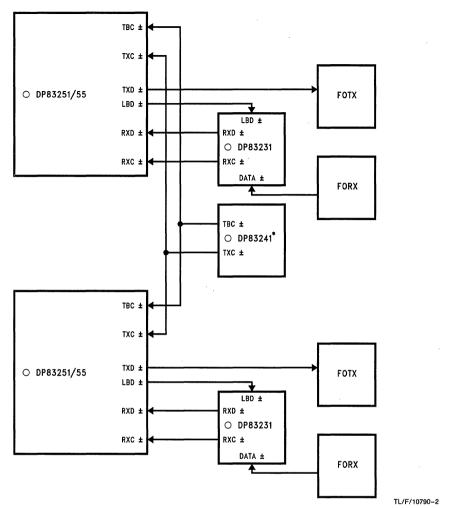

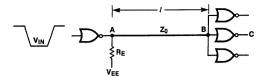

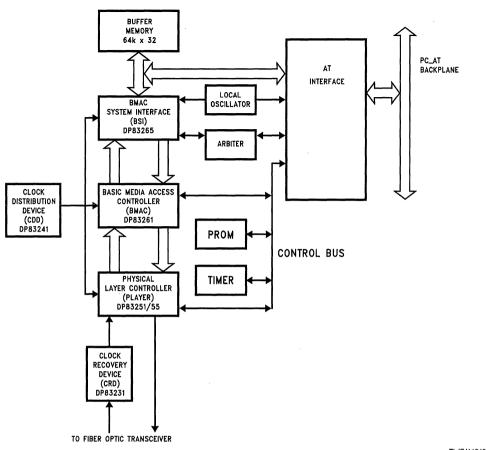

FIGURE 1-1. FDDI Chip Set Block Diagram

TL/F/10384-1

#### **Table of Contents**

# 1.0 FDDI CHIP SET OVERVIEW 2.0 FUNCTIONAL DESCRIPTION 3.0 PIN DESCRIPTIONS

#### 4.0 ELECTRICAL CHARACTERISTICS

- 4.1 Absolute Maximum Ratings

- 4.2 Recommended Operating Conditions

- 4.3 DC Electrical Characteristics

- 4.3 AC Electrical Characteristics

#### **5.0 DETAILED INFORMATION**

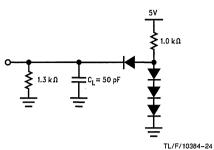

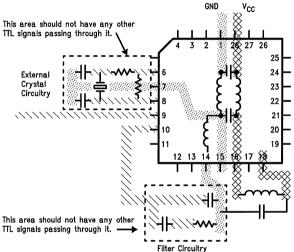

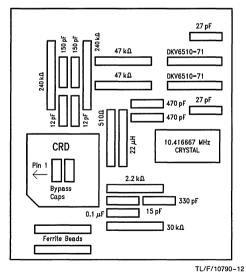

- 5.1 Special External Components

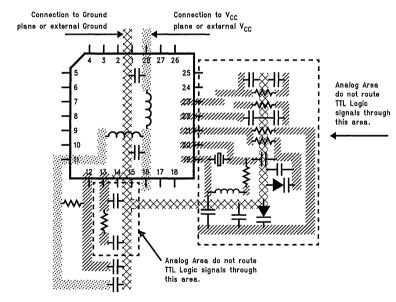

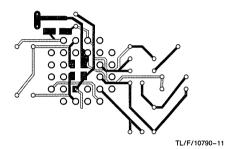

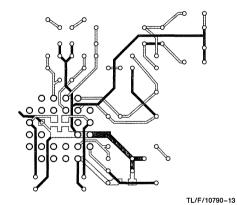

- 5.2 Layout Recommendations

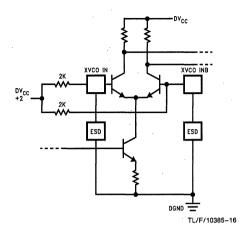

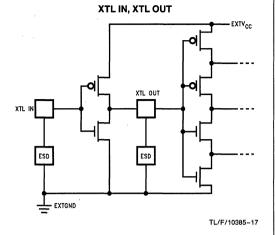

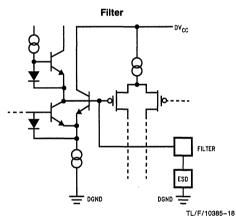

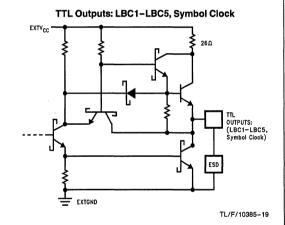

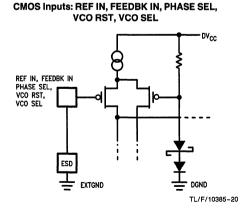

- 5.3 Input and Output Schematics

- 5.4 Debug Procedure

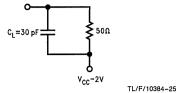

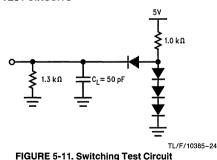

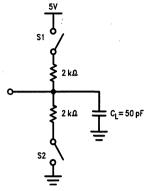

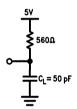

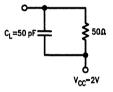

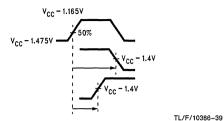

- 5.5 AC Test Circuits

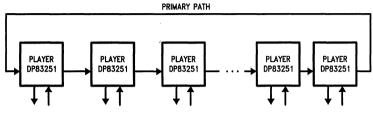

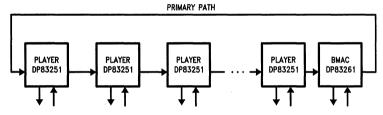

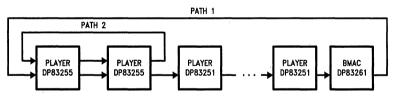

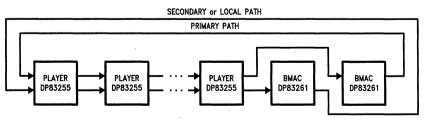

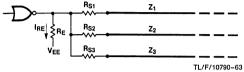

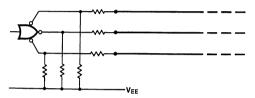

#### 1.0 FDDI Chip Set Overview

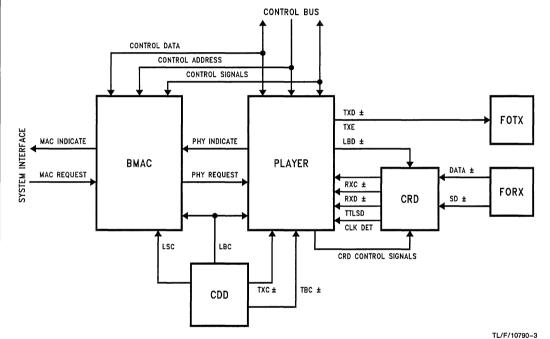

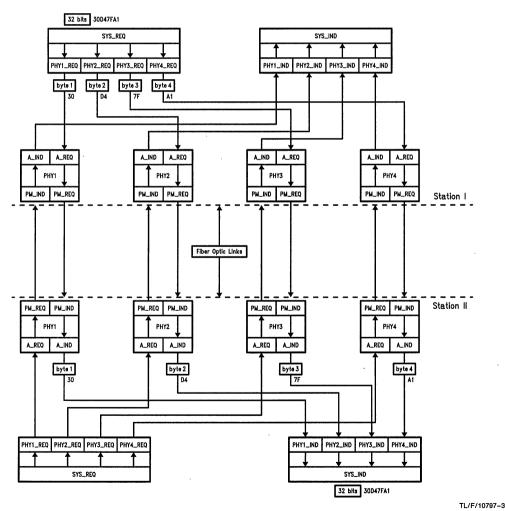

National Semiconductor's FDDI chip set consists of five components as shown in *Figure 1-1*. For more information about the other devices in the chip set, consult the appropriate data sheets and application notes.

# DP83231 CRD™ Device Clock Recovery Device

The Clock Recovery Device extracts a 125 MHz clock from the incoming bit stream.

#### **Features**

- · PHY Layer loopback test

- · Crystal controlled

- Clock locks in less than 85 µs

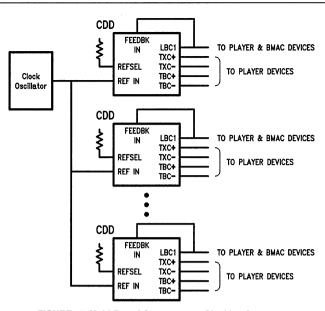

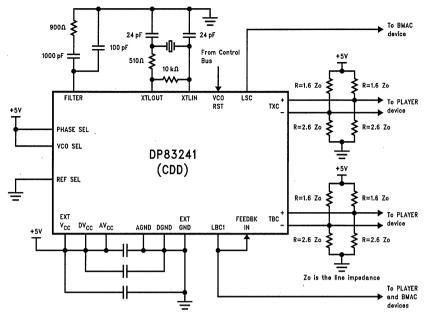

## DP83241 CDDTM Device Clock Distribution Device

From a 12.5 MHz reference, the Clock Distribution Device synthesizes the 125 MHz, 25 MHz and 12.5 MHz clocks required by the BSI, BMAC, and PLAYER devices.

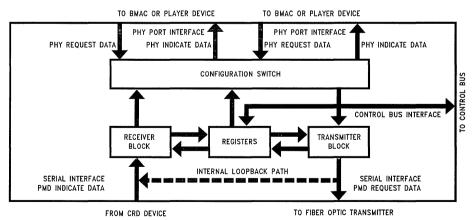

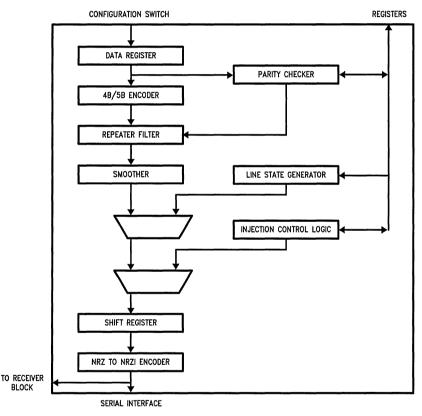

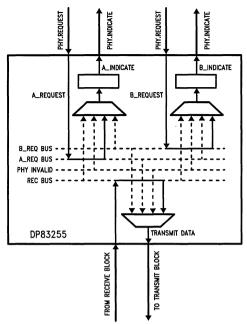

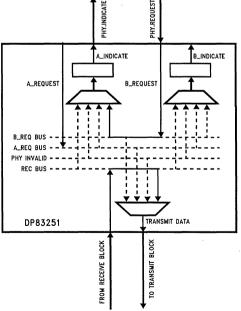

# DP83251/55 PLAYER™ Device Physical Layer Controller

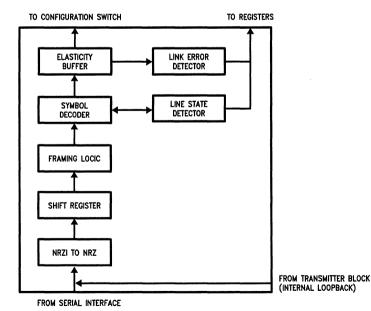

The PLAYER device implements the Physical Layer (PHY) protocol as defined by the ANSI FDDI PHY X3T9.5 Standard.

#### **Features**

- 4B/5B encoders and decoders

- Framing logic

- · Elasticity Buffer, Repeat Filter, and Smoother

- · Line state detector/generator

- · Link error detector

- Configuration switch

- · Full duplex operation

- Separate management port that is used to configure and control operation.

In addition, the DP83255 contains an additional PHY\_Data.request and PHY\_Data.indicate port required for concentrators and dual attach stations.

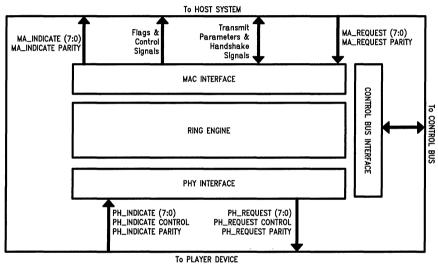

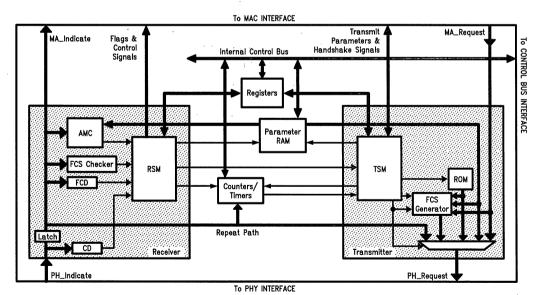

# DP83261 BMAC™ Device Media Access Controller

The BMAC device implements the Timed Token Media Access Control protocol defined by the ANSI FDDI X3T9.5 MAC Standard.

#### **Features**

- · All of the standard defined ring service options

- Full duplex operation with through parity

- Supports all FDDI Ring Scheduling Classes (Synchronous, Asynchronous, etc.)

- Supports Individual, Group, Short, Long, and External Addressing

- · Generates Beacon, Claim, and Void frames internally

- · Extensive ring and station statistics gathering

- · Extensions for MAC level bridging

- Separate management port that is used to configure and control operation

- · Multi-frame streaming interface

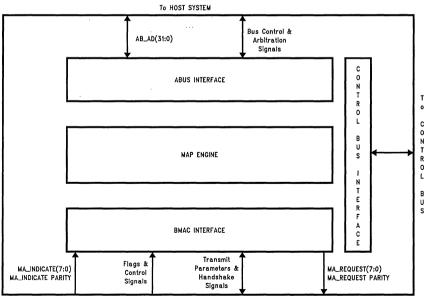

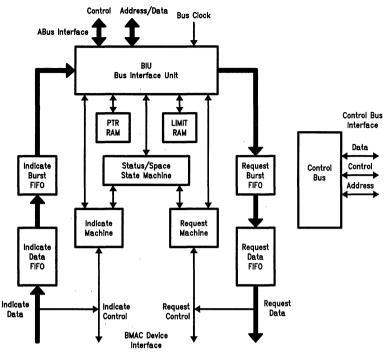

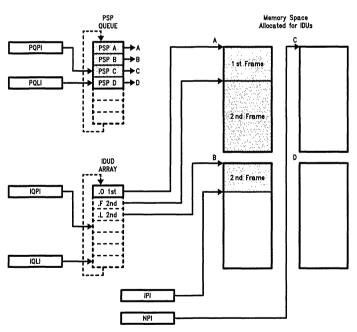

#### DP83265 BSI™ Device System Interface

The BSI Device implements an interface between the National FDDI BMAC device and a host system.

#### **Features**

- 32-bit wide Address/Data path with byte parity

- Programmable transfer burst sizes of 4 or 8 32-bit words

- · Interfaces to low-cost DRAMs or directly to system bus

- · Provides 2 Output and 3 Input Channels

- · Supports Header/Info splitting

- Efficient data structures

- · Programmable Big or Little Endian alignment

- · Full Duplex data path allows transmission to self

- · Comfirmation status batching services

- · Receive frame filtering services

- Operates from 12.5 MHz to 25 MHz synchronously with host system

#### 2.0 Functional Description

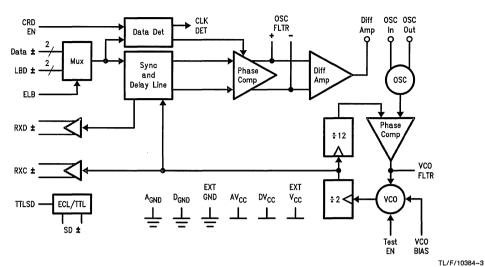

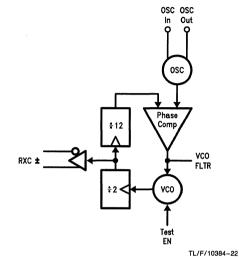

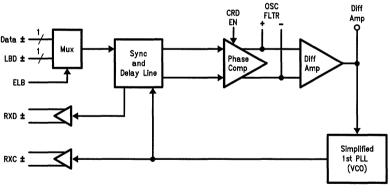

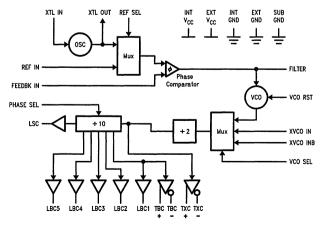

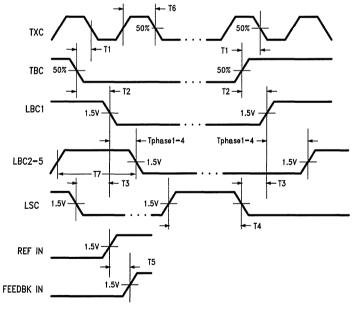

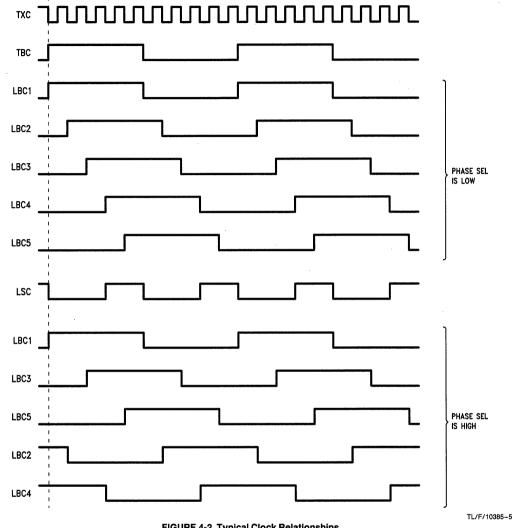

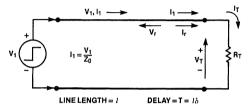

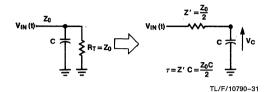

The DP83231 uses two phase locked loops (PLL's) to perform the clock recovery function. The function of the first PLL is to establish a 250 MHz Voltage Controlled Oscillator (VCO) with a narrow frequency range which can be pulled by the second PLL. The function of the second PLL is to force this same VCO to track the incoming data so that a Receive Clock output and a data synchronizing flip-flop can be driven from it. Operation of the VCO at 250 MHz ensures that the received clock output operating at half of the VCO frequency has a 50% duty cycle waveform independent of any VCO waveform dissymmetry.

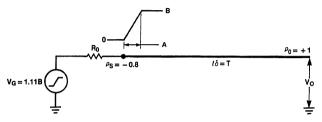

The first PLL uses a 10.41666 MHz crystal as a pullable frequency reference to generate the 250 MHz VCO. The limited frequency pulling range of the crystal ensures that the capture range of the 250 MHz VCO is limited to less than 0.1% of the specified data transition rate, thus eliminating the possibility of fractional or harmonic lock up modes. The output of the VCO is divided by twenty four and applied to the feedback input of the phase detector in the first PLL. The phase detector compares the phase of the VCO divided by twenty four signal against the phase of the crystal to maintain VCO lock at 250 MHz. If the phase transition of the signal derived from the VCO arrives at the phase detector before that of the crystal, the charge pump circuitry will apply a negative current pulse to the VCO FLTR node who's width is proportional to the phase error. The charge pulled out of the filter capacitors will drive the voltage applied to the VCO downward. This reduction in the VCO's control voltage will slow down the frequency of the VCO and will appear during successive cycles to reduce the VCO's phase and frequency error. As the frequency of the crystal varies, in response to the second PLL, the frequency of the 250 MHz VCO will change in an attempt to remain 24 times the crystal's frequency.

The second PLL delays the phase transitions of the selected incoming stream of data (DATA± or LBD±), and then compares them against the phase transitions of a gated 125 MHz signal derived from the 250 MHz VCO. The delayed incoming data is applied to the reference input of a phase detector and the gated VCO signal is applied to it's feedback input. If the positive and negative phase transitions of the incoming data do not line up with the phase transitions of the gate VCO signal, the charge pump circuitry associated with that phase detector will apply current pulses to the OSC FLTR± nodes which are proportional to the phase error. The change in the charge on the filter capacitors will modify the reverse bias on the varactors in the crystal's tank circuit thus causing the frequency of the 10.41666 MHz crystal (and consequently the VCO) to shift

in the direction which will reduce their phase error. When the phase of the VCO and the incoming data are aligned, a VCO divided by two signal can be used as the Receive Clock output. Because the two PLL's share a common VCO feedback path, the cutoff frequency of the loop filters associated with the second PLL are specified to be approximately 10 times lower than the cutoff frequency of the first PLL to prevent instability between the two loops.

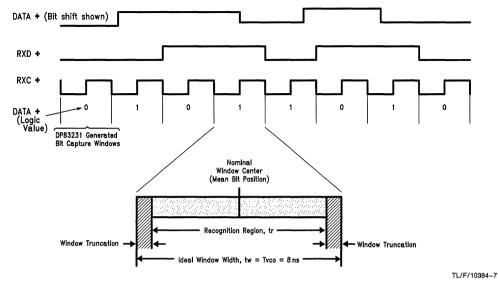

The delay line associated with the second PLL precisely centers the data transitions within the data window. The delay line remains accurate independent of temperature, power supply, IC process variation or external components. The design also ensures that the charge pump up and down circuits both produce an active pulse at each zero phase crossing when in lock to guarantee a linear phase detector gain characteristic.

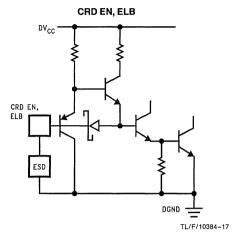

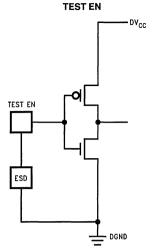

The CRD continually monitors the data frequency at the selected data inputs. If this input frequency drops below ½ the minimum allowed frequency (about 3 MHz) the CRD resets itself by internally deasserting CRD-EN. This centers the crystal frequency, and restarts the internal VCO.

The CRD EN pin is provided to initialize the CLK DET circuitry and enable the crystal to track incoming data. The part is enabled when this pin is active High. Deassertion of this pin will cause the CLK DET circuitry and the OSC FLTR  $\pm$  pins to be disabled in a manner similar to when legitimate data is not being received. Deassertion of the CRD EN pin also momentarily causes (1  $\mu s$ ) the VCO FLTR pin to be pulled to ground and stops the VCO and RXC  $\pm$  outputs. After this time, the VCO will be restarted and its output frequency will climb quickly to approximately 250 MHz.

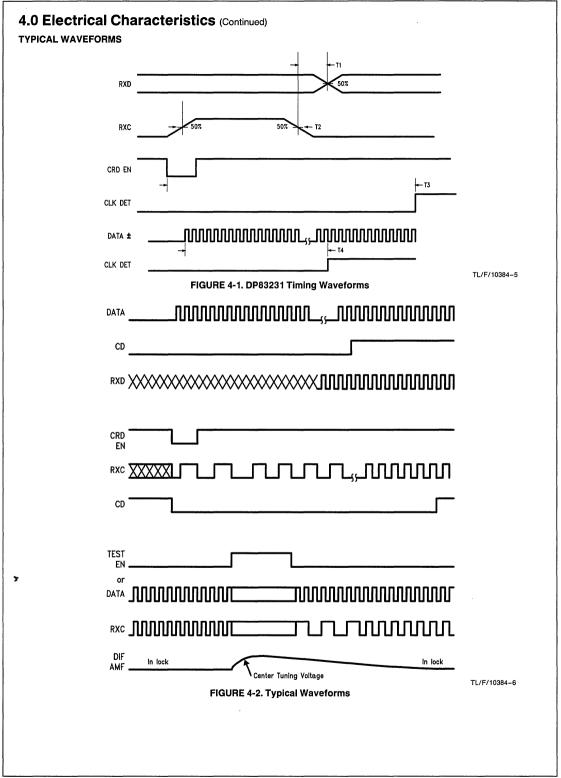

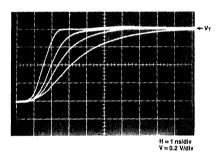

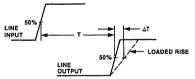

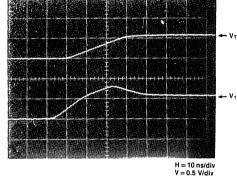

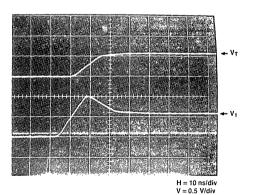

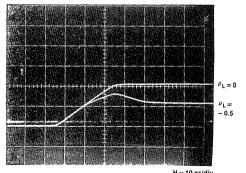

The device is capable of locking on to a stream of Halt or Master line states in less than 100  $\mu s$  when using a 10.41666 MHz crystal to govern the 250 MHz VCO. Lock on time for a stream of Idle line states is less than 10  $\mu s$  once Halt or Master line status is obtained. During quiet line conditions the chip will output a continual stream of Received Clock whose frequency will be within less than 0.1% of the upstream station's data rate. The Received Data outputs are always active. Prior to the CLK DET output transitioning active High, the Received Data outputs may issue invalid data (see Typical Waveforms). When the device is locked, Received Data is presented on the falling edge of the Receive Clock output insuring sufficient setup and hold margin for the receiving device.

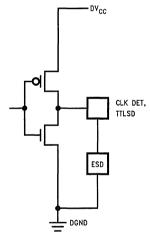

An ECL to TTL translator is provided on the chip to convert the FORX's ECL signal detect output level to TTL for use by the PLAYER device.

#### 2.0 Functional Description (Continued)

FIGURE 2-1. DP83231 Block Diagram

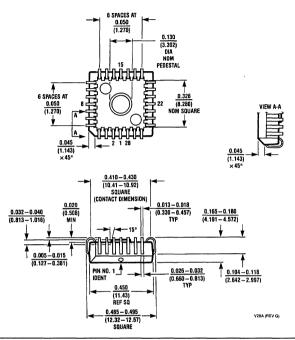

Order Number DP83231AV See NS Package Number V28A

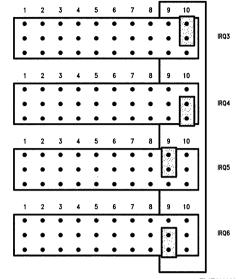

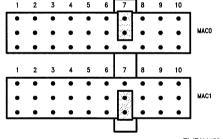

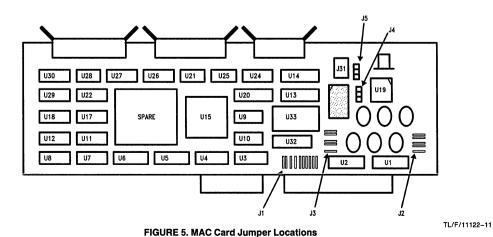

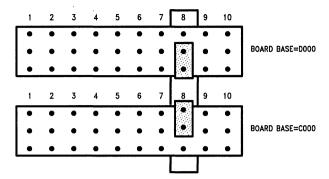

FIGURE 2-2. DP83231 Pinout