# CHARACTERISTICS OF THE MODEL 1604 COMPUTER

CONTROL DATA CORPORATION

# CHARACTERISTICS OF THE MODEL 1604 COMPUTER

Publication No. 018c

©1959 CUNTROL DATA CORPORATION

R.- 5/1/61

The Model 1604 Computer

# GLOSSARY OF TERMS

The following terms, symbols and abbreviations are defined as they pertain to the discussions of the Model 1604 Computer contained in this manual.

| Α                   | Accumulator, or A register                                            |  |

|---------------------|-----------------------------------------------------------------------|--|

| A <sub>n</sub>      | The binary digit in position n of the A register                      |  |

| Adv                 | Advance (add 1)                                                       |  |

|                     | Transmit to                                                           |  |

| b                   | Index designator                                                      |  |

| В                   | Index register                                                        |  |

| (B <sup>b</sup> )   | Contents of the designated index register                             |  |

| Exit                | Proceed to next program step                                          |  |

| f                   | Function code                                                         |  |

| Half exit           | Proceed to lower instruction of a program step                        |  |

| Indirect Addressing | Using the execution address portion of an instruction to specify a    |  |

|                     | storage location which contains the address of the operand            |  |

| j                   | The condition designator for jump and stop instructions and the sub-  |  |

|                     | instruction designator for the external function instruction          |  |

| k                   | Base execution address for shift and scale instructions               |  |

| К                   | Shift count for shift instructions ( $k + B^b = K$ )                  |  |

| LA                  | Lower address - the base execution portion of the lower instruction   |  |

|                     | of a program step                                                     |  |

| LQM                 | Logical (bit-by-bit) product of (Q) and (M)                           |  |

| m                   | Base execution address - the 15-bit portion of an instruction as read |  |

|                     | from storage or the 15-bit portion of an instruction obtained by in-  |  |

|                     | direct addressing                                                     |  |

Execution address - the 15-bit portion of an instruction obtained directly from storage or by indirect addressing which has been modified by the addition of the contents of the designated index register.

If

$$b = 0$$

, or  $(B^b) = 0$ ,  $M = m$

If  $b = 1-6$ ,  $M = m + (B^b)$

| ()                             | Contents of a register or storage location                          |

|--------------------------------|---------------------------------------------------------------------|

| ()'                            | Complement contents of a register or storage location               |

| () <sub>i</sub>                | Initial contents of a register or storage location                  |

| () <sub>f</sub>                | Final contents of a register or storage location                    |

| O <sup>i</sup>                 | Output register i                                                   |

| Р                              | Program address register or P register                              |

| Q                              | Auxiliary arithmetic register or Q register                         |

| R                              | Address buffer register or R register                               |

| s <sup>1</sup> -s <sup>2</sup> | Storage address registers or S registers                            |

| Red                            | Reduce (subtract 1)                                                 |

| Ret Jump                       | Return jump                                                         |

| UA                             | Upper address                                                       |

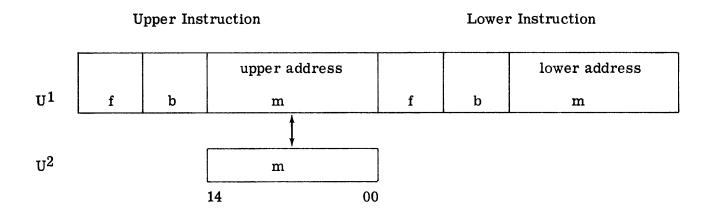

| <b>U</b> <sup>1</sup>          | Program control register or U register                              |

| U <sup>2</sup>                 | Auxiliary program control register                                  |

| x                              | Exchange register or X register                                     |

| У                              | The base execution address for instructions in which the operand is |

|                                | normally contained in the address portion of the instruction        |

| Y                              | The operand specified by $y + (B^b)$                                |

| $z^1$ - $z^2$                  | Storage restoration registers or Z registers                        |

# TABLE OF CONTENTS

|    |                               | Page  |

|----|-------------------------------|-------|

| I. | Introduction                  | I-1   |

|    | Summary of Characteristics    | I-1   |

|    | Principles of Operation       | I-1   |

|    | Physical Description          | I-6   |

|    | Over-all Analysis of Computer | I-6   |

|    | Input-Output Section          | I-6   |

|    | Arithmetic Section            | I-7   |

|    | Storage Section               | I-7   |

|    | Control Section               | I-8   |

| п. | Programming                   | II-1  |

|    | 1604 Address System           | II-1  |

|    | Repertoire of Instructions    | Ш-5   |

|    | Analysis of 1604 Instructions | Ш-9   |

|    | Special Programming Features  | 11-38 |

|    | Special Instructions          | II-38 |

|    | Floating-Point                | II-43 |

|    | Scaling                       | II-44 |

|    | Instruction Faults            | II-45 |

|    | Real Time Clock               | II-46 |

|    | Program Interrupt             | II-47 |

|    | Input-Output Communication    | II-47 |

|    | Indirect Addressing           | II-49 |

| ш.  | Theory of Operation            | III-1          |

|-----|--------------------------------|----------------|

|     | Input-Output Section           | III-1          |

|     | Console Input-Output Equipment | III-3          |

|     | 1607 Magnetic Tape System      | III-4          |

|     | 1605 Adaptor                   | III-6          |

|     | Buffer Control                 | III-8          |

|     | Input-Output Specifications    | III-8          |

|     | Storage Section                | III-15         |

|     | Arithmetic Section             | III-22         |

|     | Control Section                | III-26         |

|     | Program Control Register       | III-27         |

|     | The $U^2$ Accumulator          | <b>III-3</b> 0 |

|     | Index Registers                | III-31         |

|     | Address Buffer Register        | III-31         |

|     | Program Address Register       | III-31         |

|     | Control Sequences              | III-32         |

| IV. | Installation and Operation     | IV-1           |

|     | Operating Controls             | IV-1           |

|     | Installation                   | I <b>V-</b> 1  |

# I. INTRODUCTION

Control Data's Model 1604 is an all-transistorized, stored program, general-purpose digital computer. Having a large storage capacity (32,768 48-bit words), exceedingly fast computation and transfer speeds, and special provisions for input-output communications, the 1604 is designed to handle large-volume data processing and to solve large-scale scientific problems.

The following is a summary of the 1604 features:

- . Stored-program, general-purpose digital computer

- . Parallel mode of operation

- . 48-bit word length

- . Single-address logic, two instructions per 48-bit word:

| operation code         | 6 k        | oits    |

|------------------------|------------|---------|

| designator             | <b>3</b> k | oits    |

| base execution address | •••        | 15 bits |

- . Six index registers

- . Indirect addressing feature

- . 32,768 48-bit words of magnetic core storage:

Storage in two independent 16, 384 word banks, alternate phased

4.8 microseconds effective cycle time (representative program)

6.4 microseconds total cycle time

. Highly versatile input-output facilities:

Three 48-bit buffer input channels

Three 48-bit buffer output registers

- One high-speed 48-bit input transfer channel (4.8 microseconds, 48-bit parallel word)

- One high-speed 48-bit output transfer channel (4.8 microseconds, 48-bit parallel word)

- Program interrupt

- . Control console includes:

350 character per second transistorized photo-electric paper tape reader

60 character per second paper tape punch

Input-output electric typewriter

Translated contents of all operational registers displayed as Arabic numerals (octal)

. Flexible repertoire of 62 instructions provides:

Fixed point arithmetic (integer and fractional) . Floating binary point

arithmetic . Logical and masking operations . Indexing . Memory

searching . Input-output . Sequence control (conditional and unconditional)

. Multiple precision capability (accumulator and auxiliary register treated as a single double-length register), etc.

. Binary arithmetic - modulus  $2^{48}$  minus one (one's complement)

parallel addition, 1.2 microseconds basic add time (without access)

- . Real-time clock

- . Completely solid-state

Diode logic - transistor amplifiers - magnetic core memory

. Small size

Goes in 20' x 20' room

. Low power consumption

In addition to communicating with standard peripheral equipment, such as magnetic tape units, card reader, punch, high-speed printers, and typewriter, the 1604 can also be used for control or communication in radar and sonar systems, real-time instrumentation systems, digital communication systems, and special display systems.

In the 1604 Computer, input-output operations are carried out independently of the main computer program. When transmission of data is required, the main computer program is used only to initiate an automatic cycle which buffers data to and from the computer memory. The main computer program then continues while the actual buffering of data is carried out independently and automatically.

The input-output section of the 1604 contains the facility for several modes of communication. For normal exchange of data with peripheral equipment, independent control is provided for the transfer of data via three 48-bit buffer input and three 48-bit buffer output channels asynchronously with the main computer program. For high-speed communication one 48-bit input transfer channel and one 48-bit output transfer channel are provided so that two or more 1604's can communicate with each other. Communication control is performed by the external function instruction. In addition, the interrupt feature provides requests from peripheral equipment to the computer.

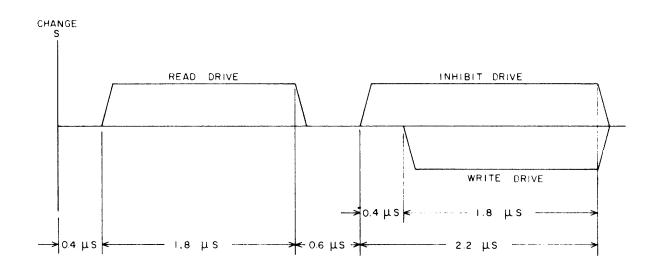

The storage section of the 1604 is a large-capacity magnetic core storage system providing high-speed, non-volatile, random-access storage for 32,768 48-bit words. One 48-bit word may contain either a 48-bit data word or two 24-bit instructions. The read access time, i.e., the time from request of data to delivery from storage, is 2.2 microseconds.

The 1604 instruction repertoire contains a flexible list of 62 instructions which expand into many sub-instructions. These 62 instructions provide fixed binary point arithmetic (integer and fractional), floating binary point arithmetic, logical and masking operations, normal arithmetic operations modulus  $2^{48}$  minus one (one's complement), indexing, memory searching, input-output, sequence control (conditional and unconditional),

I-3

multiple precision capability, etc. Some of the special programming features include ease of handling constants, indirect addressing, four search instructions, high-speed inputoutput transfers, buffering, external function, program interrupt, and a large group of logical commands.

In addition to the standard 1604 console with its display panel (translated contents of all operational registers are displayed in Arabic numerals--octal), typewriter, and paper tape reader and punch, Control Data offers as optional equipment the Model 1607 Magnetic Tape System and the Model 1605 Adaptor. A number of 1607 Magnetic Tape Systems can be attached to a 1604 Computer. Simultaneously among these 1607's three tape handlers can be reading and three can be writing--each at a 30KC character transfer rate. Each 1607 tape system has the facility for simultaneously reading from one tape handler and writing on one tape handler, while the remaining two tape handlers are rewinding. A summary of 1607 features is as follows:

| Tape Width $1/2$ inch                          |

|------------------------------------------------|

| Tape Recording Density 200 characters per inch |

| Read-Write Speed 150 inches per second         |

| Rewind Speed 150 inches per second             |

| Character Transfer Rate 30KC                   |

| Length of Tape                                 |

| Block Length Variable                          |

| Number of Tape Handlers Four per Model 1607    |

The Control Data Model 1605 Adaptor permits communication between the 1604 Computer and any of the following IBM peripheral equipment: 714 Card Reader, 727 Magnetic Tape Units, 717 Line Printer, and 722 Card Punch. Each 1605 Adaptor can be

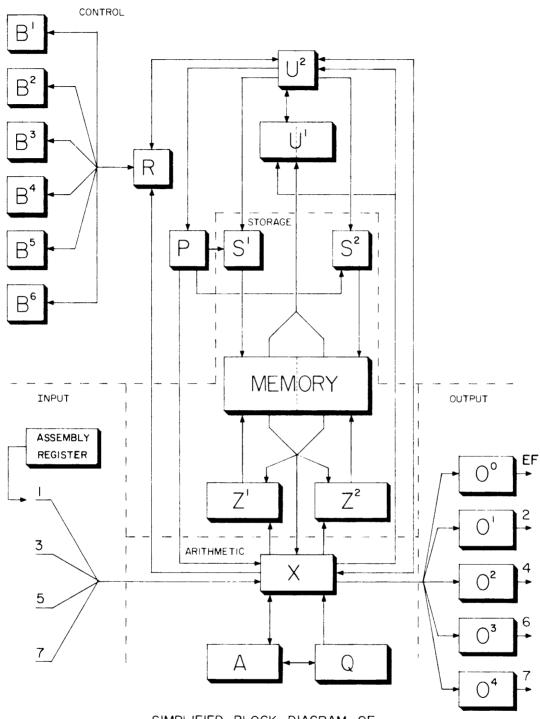

SIMPLIFIED BLOCK DIAGRAM OF THE MODEL 1604 COMPUTER

FIG. I-1

connected to any of the three buffer input channels and three buffer output channels, and each 1605 is independently addressable.

#### PRINCIPLES OF OPERATION

# **Physical Description**

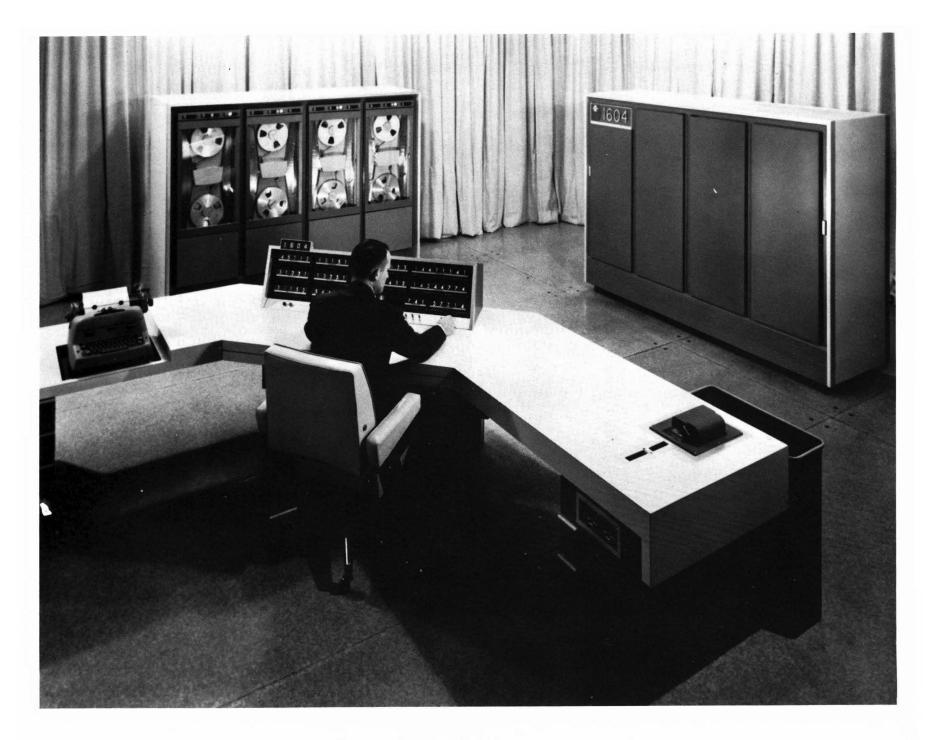

Standard equipment available with the Model 1604 includes the main computer cabinet and the 1604 console. The console consists of an electric typewriter, paper tape punch, and paper tape photo-electric reader. Optional equipment for the 1604 Computer System includes the 1607 Magnetic Tape System, 1605 Adaptor; the 1606 Printer, the 1608 Control Unit for IBM high-speed tape transports and the 1609 Punched Card Control Unit. Over-all Analysis of Computer

The computer can be divided functionally into four major sections: (1) Input-output section which provides the means of communication between the computer and the various external equipments, (2) Arithmetic section which performs both the arithmetic and logical operations required for the execution of instructions, (3) Storage section which provides internal storage for both data and instruction, and (4) Control section which successively obtains the instruction from storage, then interprets each instruction to send the required commands to other sections. The control section coordinates and sequences all the operations which carry out the execution of an instruction. A simplified block diagram of the computer is shown in Figure 1-1.

#### Input-output Section

There are four input channels which bring information into the computer via the X register. Channels 1, 3, and 5 are used for buffer communication; Channel 7 is used in transfer communication -- a very high-speed means of exchanging data. Information from the input-output equipment at the 1604 console is always received via channel 1.

Typically, channel 3 is connected to a 1607 magnetic tape system. Channel 5 provides another means of input which may be used by the 1605 Adaptor, a second 1607, or another equipment.

Output registers  $O^1$ ,  $O^2$ ,  $O^3$ , and  $O^4$  are used to transmit information from the computer to channels 2, 4, 6, and 7, respectively. Function register  $O^0$  is used to transmit control information to the various external equipments.

# **Arithmetic Section**

The A register, or accumulator, is the principal arithmetic register. Nearly all arithmetic and logical operations make use of A. This register has provisions for the parallel addition of (X) to the contents of A. It can be shifted either separately or in conjuction with the Q register.

The Q register is an auxiliary arithmetic register which assists the accumulator in the performance of the more complicated arithmetic operations. It is used in combination with the X register in the formation of logical products. Q may be shifted either separately or in conjunction with A.

The X or exchange register is used in arithmetic operations as well as in most data transmission between various sections of the computer.

## Storage Section

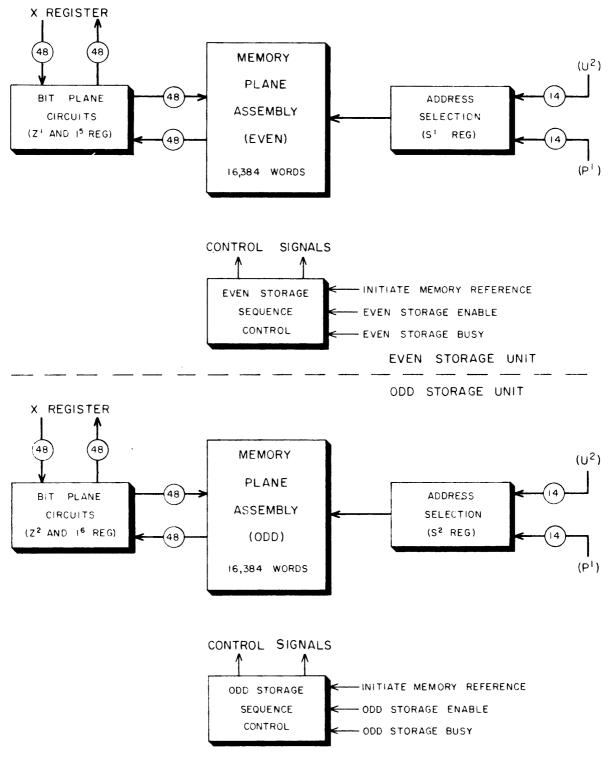

The 32,768 48-bit word magnetic core storage section is controlled by a two-phase timing system, each phase controlling one-half (16,384 48-bit words) of the total storage. All odd storage addresses reference one storage unit; all even addresses reference the other storage unit. The read access time of each section is 2.2 microseconds after which, without delay, the next arithmetic operation is initiated. Each unit has a total cycle time

I-7

of 6.4 microseconds. The storage cycles of the two sections overlap one another in the execution of a program, with the result that the effective cycle time is 3.2 microseconds when addresses of alternate memory banks are referenced. The average effective cycle time for random addresses is about 4.8 microseconds for a representative program.

The address register for the even storage unit is  $S^1$ ;  $S^2$  is the address register for the odd storage unit. In addition, each unit has a storage restoration register ( $Z^1$  and  $Z^2$ ) which holds the word to be written into a given storage location.

Words to be read out of either storage unit are entered in the X register, and from there transmitted to the appropriate register. Words to be entered or written into a storage unit are transmitted from X to the appropriate Z register, and thence to storage.

# Control Section

The control section directs the operations required to execute instructions and to exchange data with external equipment. The major portion of the control section consists of command sequences, static networks for sensing and storing special conditions, and several registers (U, P, R and  $B^1$  through  $B^6$ ). The control section acquires instructions and initiates the command sequences for executing them. The coordination of operations in the various sections of the computer is maintained by the control section.

## GENERAL

Operation of the 1604 Computer is sequenced by an internally stored program. The program is contained, along with the data being processed, in a central random-access storage. The input-output equipments, as well as the internal program, have direct access to this common storage unit, thus permitting input-output operations to proceed during computation.

This chapter describes the make-up of the program that orders machine operation. Included in the chapter are a description of the address system, a summary of the repertoire of instructions, and an analysis of each instruction.

## 1604 ADDRESS SYSTEM

The Control Data 1604 is a single-address computer. As such, one address is explicitly referred to by one instruction. However, the computer is capable of selfmodification during the course of a program by the use of the B-boxes or indirect addressing

As already mentioned, the storage system contains 32,768 addresses divided into two units: an odd unit and an even unit. The locations are identified, generally, by the octal range 00000 through 77777 - the even addresses referring to one unit, the odd addresses to the other.

Certain specific storage locations in the memory are used for control and reference functions. These storage locations may be addressed as operands as well as being addressed implicitly by certain control functions. The address assignments for these functions are listed below and will later be explained in detail:

| Special Address | Function or Purpose                   |

|-----------------|---------------------------------------|

| 00000           | Real Time Clock (60 steps per second) |

| 00001           | Channel 1 control                     |

| 00002           | Channel 2 control                     |

| 00003           | Channel 3 control                     |

| 00004           | Channel 4 control                     |

| 0000 <b>5</b>   | Channel 5 control                     |

| 0000 <b>6</b>   | Channel 6 control                     |

| 00007           | Interrupt program (exit-entrance)     |

# Program Step

A step in the computer program is composed of the orders provided to the computer by the contents of one 48-bit word. This word is treated by halves, each containing a 1604 instruction <u>expressed in 24 bits</u>. The two instructions are thus described as the "upper" and "lower" instructions of the program step.

The two instructions can be considered as logically separate entities in a program sequence. As a practical matter in program coding, however, the pair is an entity similar to a two-address instruction. The two single-address instructions are not separable in the sense that the lower may not be executed without the upper.

If it is desired to place only one instruction in a program step, the other instruction location should contain a "do nothing" or pass instruction, described in a later paragraph.

## Instruction Composition

The 1604 instruction is a 24-bit quantity specifying an operation which the computer is to perform. The composition of the instruction word is shown in the figure below. Shown

in the figure are the general format of the four specific instruction types. These four specific types are obtained by a variance in the interpretation of the designator and base execution address portions of the instruction. The External Function instruction is a special case and is covered in greater detail later in this chapter.

# General Format

| 6 bits         | 3 bits     | 15 bits                | ٦ |

|----------------|------------|------------------------|---|

| Operation Code | Designator | Base Execution Address |   |

Indexed Instructions with storage reference for operand

| f = 6 bits     | b = 3 bits | m = 15 bits        |

|----------------|------------|--------------------|

| Operation Code | Index      | Address of Operand |

# Indexed Instructions with self contained operand

| f = 6 bits     | b = 3 bits | y = 15 bits |

|----------------|------------|-------------|

| Operation Code | Index      | Operand     |

Shift Instructions

| f = 6 bits     | b = 3 bits | k = 15 bits |

|----------------|------------|-------------|

| Operation Code | Index      | Shift Count |

Jump Instructions and sense external or internal condition sub-instructions

| f = 6 bits     | j = 3 bits | m = 15 bits                 |

|----------------|------------|-----------------------------|

| Operation Code | Condition  | Address of Next Instruction |

The breakdown of the instruction word, as indicated in the figure is:

6 bits - Operation Code, f

3 bits - Designator - Index, b

- Condition - j

- Operand, y

## - Shift Count, k

The operation code specifies the general character of the instruction. There are 62 operation codes, identified 01 through 76 (octal), available for use in programming. Two codes, 00 and 77, though capable of being expressed as operation codes, are interpreted as faults which will stop computation when translated by the computer.

Depending upon the particular instruction, the designator is interpreted in one of two different ways. As an address modifier (b), it causes the base execution address to be changed by the addition of the contents of the index register specified by the designator. When used in certain of the instructions as a jump designator (j), it determines a change in program sequence, depending upon the condition of certain specified registers.

An index designation of 7 will indicate that indirect addressing is to be used. (Indirect addressing is a means for expanding the reference capabilities of the instruction execution address.)

Eight jump conditions are specified by the jump designator, j. These provide for change of sequence depending upon the status of the A register, the Q register, or the position of jump and stop select switches on the console. These conditions are completely delineated in later paragraphs describing the instructions.

The base execution address of the instruction format (lower 15 bits) holds the address which is basic to the particular instruction. This base execution address is generally the designator of the location of the operand for the instruction which is to be performed. In some cases, the base execution address itself can become the operand, or the shift count. The operation code determines the particular role and definition of the base execution address.

# REPERTOIRE OF INSTRUCTIONS

# INPUT-OUTPUT

| Operation            | Instruction Code |             | Execution Time µs |              |  |

|----------------------|------------------|-------------|-------------------|--------------|--|

|                      |                  | Min.        | <u>Av.</u>        | Max.         |  |

| Input transfer       | 62 b m           | 4. <b>8</b> | 4.0 + 4.8r        | 6.8+4.8r     |  |

| Output transfer      | 63 b m           | 4.8         | 4.0+4.8r          | 6.8+4.8r     |  |

| External Function    | 74 j y           | 6.4         | 6.4               | 6.4          |  |

|                      | ARITHMETIC       |             |                   |              |  |

| Increase Accumulator | 11 b m           | 2.8         | <b>3</b> .0       | 3.2          |  |

| Add                  | 14 b m           | 4.8         | 7.2               | 9.6          |  |

| Subtract             | 15 b m           | 4.8         | 7.2               | 9.6          |  |

| Multiply Integer     | 24 b m           | 25.2        | 25.2+.8n          | 66.4         |  |

| Divide Integer       | 25 b m           | 63.6        | 65.2              | 66.4         |  |

| Multiply Fractional  | 26 b m           | 25.2        | 25.2+.8n          | 66.4         |  |

| Divide Fractional    | 27 b m           | 63.6        | 65.2              | 66.4         |  |

| Floating Add         | <b>3</b> 0 b m   | 11.2        | 18.8              | 26.8         |  |

| Floating Subtract    | 31 b m           | 11.2        | 18.8              | 26.8         |  |

| Floating Multiply    | 32 b m           | 3.2         | <b>36</b> . 0     | 57.2         |  |

| Floating Divide      | 33 b m           | 3.2         | <b>56</b> .0      | 57.2         |  |

| Replace Add          | 70 b m           | 10.2        | 13.2              | <b>16.</b> 0 |  |

| Replace Subtract     | 71 b m           | 10.2        | 13.2              | 16.0         |  |

| Replace Add One      | 72 b m           | 10.2        | 13.2              | <b>16</b> .0 |  |

| Replace Subtract One | 73 b m           | 10.2        | 13.2              | 16.0         |  |

# SHIFT

| Operation                      | Instruction Code    |             | Execution Time <u>us</u> |             |

|--------------------------------|---------------------|-------------|--------------------------|-------------|

|                                |                     | <u>Min.</u> | <u>Av.</u>               | <u>Max.</u> |

| Accumulator Right Shift        | 01 b k              | 2.8         | 2.8+.4s                  | 54.4        |

| Q Register Right Shift         | 02 b k              | 2.8         | 2.8+.4s                  | 54.4        |

| AQ Right Shift                 | 0 <b>3</b> b k      | 2.8         | 2.8+.4s                  | 54.4        |

| <u>A</u> Left Shift            | 05 b k              | 2.8         | 2.8+.4s                  | 54.4        |

| Q Left Shift                   | 06 b k              | 2.8         | 2.8+.4s                  | 54.4        |

| AQ Left Shift                  | 07 b k              | 2.8         | 2.8+.4s                  | 54.4        |

| Scale $\underline{\mathbf{A}}$ | 34 b k              | 2.8         | 2.8 + .4s                | 54.4        |

| Scale <u>AQ</u>                | 35 b k              | 2.8         | 2.8+.4s                  | 54.4        |

|                                | TRANSMISSIVE        |             |                          |             |

| Enter Q                        | 04 b y              | 2.8         | <b>3</b> .0              | 3.2         |

| Enter <u>A</u>                 | 10 b y              | 2.8         | 3.0                      | 3.2         |

| Load <u>A</u>                  | 12 b m              | 4.8         | 7.2                      | 9.6         |

| Load <u>A</u> , Complement     | 13 b m              | 4.8         | 7.2                      | 9.6         |

| Load <u>Q</u>                  | 16 b m              | 4.8         | 7.2                      | 9.6         |

| Load <u>Q</u> , Complement     | 17 b m              | 4.8         | 7.2                      | 9.6         |

| Store <u>A</u>                 | 20 b m              | 4.8         | 7,2                      | 9.6         |

| Store <u>Q</u>                 | 21 b m              | 4.8         | 7.2                      | 9.6         |

| Substitute Address (upper)     | 60 b m <sub>u</sub> | 4.8         | 7.2                      | 9.6         |

| Substitute Address (Iower)     | 61 b m <sub>1</sub> | 4.8         | 7.2                      | 9.6         |

| Operation            | Instruction Code    |      | Execution Time µs |              |  |

|----------------------|---------------------|------|-------------------|--------------|--|

|                      |                     | Min. | <u>Av.</u>        | <u>Max.</u>  |  |

| Storage Skip         | 36 b m              | 7.2  | 8.8               | 16.0         |  |

| Storage Shift        | 37 b m              | 10.4 | 12.8              | <b>16.</b> 0 |  |

| Selective Set        | 40 b m              | 4.8  | 7.2               | 9.6          |  |

| Selective Clear      | 41 b m              | 4.8  | 7.2               | 9.6          |  |

| Selective Complement | 42 b m              | 4.8  | 7.2               | 9.6          |  |

| Selective Substitute | 43 b m              | 5.2  | 7.4               | 9.6          |  |

| Load Logical         | 44 b m              | 5.2  | 7.4               | 9.6          |  |

| Add Logical          | 45 b m              | 5.4  | 7.4               | 9.6          |  |

| Subtract Logical     | 46 b m              | 5.4  | 7.4               | 9.6          |  |

| Store Logical        | 47 b m              | 4.8  | 7.2               | 9.6          |  |

| SEARCH               |                     |      |                   |              |  |

| Equality Search      | 64 b m              | 3.6  | 4.0+3.6r          | 6.8+3.6r     |  |

| Threshold Search     | 65 b m              | 3.6  | 4.0+3.6r          | 6.8+3.6r     |  |

| Masked Equality      | 66 b m              | 3.6  | 4.0+3.6r          | 6.8+3.6r     |  |

| Masked Threshold     | 67 b m              | 3.6  | 4.0+3.6r          | 6.8+3.6r     |  |

| INDEXING             |                     |      |                   |              |  |

| Enter Index          | 50 b y              | 2.8  | <b>3.</b> 0       | 3.2          |  |

| Increase Index       | 51 b y              | 2.8  | <b>3.</b> 0       | 3.2          |  |

| Load Index (upper)   | 52 b m <sub>u</sub> | 4.8  | 7.2               | 9.6          |  |

| Load Index (lower)   | 53 b m <sub>1</sub> | 4.8  | 7.2               | 9.6          |  |

# LOGICAL

# INDEXING (cont.)

| Operation           | Instruction Code    |             | Execution <u>us</u> |      |

|---------------------|---------------------|-------------|---------------------|------|

|                     |                     | Min.        | <u>Av.</u>          | Max. |

| Index Skip          | 54 b y              | 5.6         | 5.6                 | 5.6  |

| Index Jump          | 55 b m              | 4.4         | 4.4                 | 4.4  |

| Store Index (upper) | 56 b m <sub>u</sub> | 4.8         | 7.2                 | 9.6  |

| Store Index (lower) | 57 b m <sub>1</sub> | 4.8         | 7.2                 | 9.6  |

|                     | JUMPS AND STOP      | <u>PS</u>   |                     |      |

| <u>A</u> Jump       | <b>2</b> 2 j m      | 4.0         | 7.2                 | 11.6 |

| <u>Q</u> Jump       | 23 j m              | 4.0         | 7.2                 | 11.6 |

| Selective Jump      | 75 j m              | <b>3.</b> 0 | 7.2                 | 11.6 |

| Selective Stop      | 76 j m              | <b>3</b> .0 | 7.2                 | 11.6 |

s = number of positions shifted

n = number of one's in multiplier

\*r = number of repeated executions

### ANALYSIS OF 1604 INSTRUCTIONS

The following paragraphs describe the individual instructions. The title line gives the octal code and format, verbal name, mnemonic code in parentheses, and symbolic description of the instruction.

## 01 b k A RIGHT SHIFT (ARS) Shift (A) Right by K

This instruction shifts the contents of the A register to the right the number of bit positions specified by the shift count, K. The sign bit is extended and the lowest order bits are discarded as the shift is performed. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

## 02 b k Q RIGHT SHIFT (QRS) Shift (Q) Right by K

This instruction shifts the contents of the Q register to the right the number of bit positions specified by the shift count, K. The sign bit is extended and the lowest order bits are discarded as the shift is performed. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

# 03 b k AQ RIGHT SHIFT (LRS) Shift (AQ) Right by K

This instruction shifts the contents of the A and Q registers to the right as one 96-bit register. The A register is considered as the left-most 48 bits and the Q register as the right-most 48 bits. The number of bit positions is specified by the shift count, K. The sign bit of the A register is extended as the shift is performed. The lowest order bits of

the A register replace the highest order bits of the Q register and the lowest order bits of the Q register are discarded as the shift is performed. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

04 b y ENTER Q (ENQ)  $Y \rightarrow Q$ , Extend Sign Y

This instruction enters the execution address portion, Y, of the instruction into the Q register. The operand, Y, is entered into the Q register as a 14-bit quantity plus sign. The highest order bit of Y is copied into the remaining higher order bits of the Q register. No operand storage reference is made in this instruction.

05 b k A LEFT SHIFT (ALS) Shift (A) Left by K

This instruction shifts the contents of the A register circularly to the left the number of bit postitions specified by the shift count, K. The lowest order bits are replaced with the higher order bits as the shift is performed. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

06 b k Q LEFT SHIFT (QLS) Shift (Q) Left by K

This instruction shifts the contents of the Q register circularly to the left the number of bit positions specified by the shift count, K. The lowest order bits are replaced with the higher order bits as the shift is performed. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

This instruction shifts the contents of the A and Q registers circularly to the left as one 96-bit register. The number of bit positions is specified by the shift count, K. The right-most bits of the A register are replaced with the left-most bits of the Q register as the shift is performed. The right-most bits of the Q register are replaced with the leftmost bits of the A register during the shift. Shift counts greater than 127 (decimal) are shifted in the normal manner, but are considered shift faults, and produce an interrupt (if selected). An indicator is set which may be sensed by an external function instruction.

10 b y ENTER A (ENA)  $Y \rightarrow A$ , Extend Sign Y

This instruction enters the execution address portion, Y, of the instruction into the A register. The A register is cleared and the operand Y is entered into the cleared A register as a 14-bit quantity plus sign. The highest order bit of Y is copied into the remaining higher order bits of the A register. No operand storage reference is made in this instruction.

11 b y INCREASE A (INA)  $\left[ Y + (A) \right] \rightarrow A$ , Extend Sign Y

This instruction adds the operand, Y, to the previous contents of the A register. The operand Y is treated as a 14-bit quantity plus sign in this operation. The addition is performed as if Y were a 48-bit quantity with the higher order bits copies of the sign bit. No operand storage reference is made in this instruction. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

This instruction replaces the contents of the A register with an operand, contained in the location specified by the execution address. The A register is cleared, and a storage reference is then made to obtain the 48-bit quantity designated. The 48-bit operand is copied into the cleared A register. Negative zero may be loaded into the A register.

13 b m LOAD A, COMPLEMENT (LAC)  $(M)' \rightarrow A$

This instruction replaces the contents of the A register with the complement of an operand contained in the location specified by the execution address. The A register is cleared and a storage reference is made to obtain the 48-bit quantity designated. The 48-bit operand is complemented and entered into the cleared A register. Negative zero may be thus loaded into the A register.

14 b m ADD (ADD)

$$\left[ (A) + (M) \right] \longrightarrow A$$

This instruction adds a 48-bit operand to the previous contents of the A register. A storage reference is made to obtain the 48-bit quantity contained in the location specified by the execution address. The operand is then added to the previous contents of the A register. Occurrence of an overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction. A negative zero may be produced by this instruction if and only if both operands are initially negative zeros.

15 b m SUBTRACT (SUB)  $\left[ (A) - (M) \right] \rightarrow A$

This instruction subtracts a 48-bit operand from the previous contents of the A register. A storage reference is made to obtain the 48-bit quantity contained in the location

specified by the execution address. The operand is then subtracted from the previous contents of the A register. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction. A negative zero may be produced by this instruction if the initial content of A is negative zero and the quantity in storage is a positive zero.

16 b m LOAD Q (LDQ)  $(M) \rightarrow Q$

This instruction replaces the contents of the Q register with an operand contained in the location specified by the execution address. The Q register is cleared and a storage reference is made to obtain the 48-bit quantity designated. The 48-bit operand is then entered into the cleared Q register. Negative zero may be loaded in Q.

17 b m LOAD Q, COMPLEMENT (LQC)  $(M)' \rightarrow Q$

This instruction replaces the contents of the Q register with the complement of an operand contained in the location specified by the execution address. The Q register is cleared and a storage reference is then made to obtain the 48-bit quantity specified. The 48-bit operand is complemented and entered into the cleared Q register. A negative zero may be thus loaded in Q.

# 20 b m STORE A (STA) $(A) \rightarrow M$

This instruction stores the contents of the A register at the storage location specified by the execution address. The contents of the A register are not modified by this instruction.

21 b m STORE Q (STQ)  $(Q) \rightarrow M$

This instruction stores the contents of the Q register at the storage location specified

by the execution address. The Q register content is not modified by this instruction.

22 j m A JUMP (AJP) Jump to m

This instruction has eight sub-instructions which cause a change in the prgoram sequence because of a specified condition of the A register. The index registers are not used for address modification in this instruction. The jump designator, j, in the instruction specifies which sub-instruction is to be performed. In the jump conditions both negative and positive zero are treated as zero.

The sub-instructions and the conditions required to cause a jump in the program sequence are as follows:

| 22 0 m - Jump if the A register content is zero            |

|------------------------------------------------------------|

| 22 1 m - Jump if the A register content is not zero        |

| 22 2 m - Jump if the A register content is positive        |

| 22 3 m - Jump if the A register content is negative        |

| 22 4 m - Return jump if the A register content is zero     |

| 22 5 m - Return jump if the A register content is not zero |

| 22 6 m - Return jump if the A register content is positive |

| 22 7 m - Return jump if the A register content is negative |

|                                                            |

23 j m Q JUMP (QJP) Jump to m

This instruction has eight sub-instructions which cause a change in program sequence because of a specified condition of the Q register. The index registers are not used for address modification in this instruction. The jump designator, j, in the instruction specifies which sub-instruction is to be performed. In the jump conditions both negative and

positive zero are treated as zero.

The sub-instructions and the conditions required to cause a jump in the program sequence are as follows:

23 0 m - Jump if the Q register content is zero

23 1 m - Jump if the Q register content is not zero

23 2 m - Jump if the Q register content is positive

23 3 m - Jump if the Q register content is negative

23 4 m - Return jump if the Q register content is zero

23 5 m - Return jump if the Q register content is not zero

23 6 m - Return jump if the Q register content is positive

24 b m MULTIPLY INTEGER (MUI) (A)  $(M) \rightarrow QA$

This instruction forms a 96-bit product from two 48-bit operands. The multiplier must be loaded into the A register prior to the execution of this instruction. The execution address specifies the location of the multiplicand in storage. The resulting product is contained in the QA register as a 96-bit quantity. If the operands are considered as integers, the product is correctly positioned as an integer in the QA register, i.e., the high order bits in Q and the low order bits in A.

25 b m DIVIDE INTEGER (DVI) (QA) / (M)  $\rightarrow$  A; Remainder = Q<sub>f</sub>

This instruction divides a 96-bit integer dividend by a 48-bit integer divisor. The 96bit dividend must be formed in the QA register prior to the execution of this instruction. The 48-bit divisor is read from the storage specified by the execution address. The

quotient is formed in the A register. The remainder is left in the Q register at the end of the operation. The dividend and remainder bear the same algebraic sign.

A divide overflow produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

NOTE: In the case of Integer Multiply and Divide, it should be noted that the position of the most significant bits in the product and dividend differ from the usual positioning of bits in the AQ register. Since the <u>most</u> significant digits are found in Q, this combined use of A and Q is referred to as QA (See Glossary of Terms for further definitions).

26 b m MULTIPLY FRACTIONAL (MUF) (A)  $(M) \rightarrow AQ$

This instruction forms a 96-bit product from two 48-bit operands. All quantities involved in this operation are treated as fractions with the binary point immediately to the right of the sign digit. The multiplier must be loaded into the A register prior to the execution of this instruction. The multiplicand is read from the storage location specified by the execution address. The product is formed in the AQ register and the multiplier is discarded in the multiplication process.

27 b m DIVIDE FRACTIONAL (DVF) (AQ) / (M)  $\rightarrow$  A: Remainder =  $Q_f$

This instruction divides a 96-bit quantity by a 48-bit divisor. All quantities involved in this operation are treated as fractions with the binary point immediately to the right of the sign digit. The 96-bit dividend must be loaded into the AQ register prior to the execution of this instruction. The 48-bit divisor is read from the storage location specified by the execution address. At the end of the operation the quotient is left in the A register. The remainder and the dividend bear the same algebraic sign.

A divide overflow produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

30 b m FLOATING ADD (FAD)

$$(A) + (M) \rightarrow A$$

This instruction forms the sum of two 48-bit quantities which are packed in floatingpoint format. An operand is read from the storage location specified by the execution address and is added to the previous contents of the A register. The result is normalized and rounded and left in the A register at the end of the operation. The Q register contains the residue from the rounding operation at the end of the sequence. Floating-point range faults (exponent overflow or underflow) produce an interrupt (if selected) and set an indicato which may be sensed by an external function instruction.

31 b m FLOATING SUBTRACT (FSB)  $\left[ (A) - (M) \right] \rightarrow A$

This instruction subtracts an operand in floating-point format from the previous contents of the A register, also in floating-point format. The operand is read from the storage location specified by the execution address. The result is normalized and rounded in the A register. The residue from the rounding operation is left in the Q register at the end of the sequence. A floating-point range fault produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

32 b m FLOATING MULTIPLY (FMU) (A)  $(M) \rightarrow A$

This instruction forms the product of an operand in floating-point format with the previous contents of the A register, also in floating-point format. The operand is read from the storage location specified by the execution address. The result is rounded and

normalized in the A register. The residue from the rounding operation is left in the Q register at the end of the sequence. A floating-point range fault produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

33 b m FLOATING DIVIDE (FDV) (A) / (M)  $\rightarrow$  A

This instruction forms the quotient of two 48-bit quantities in floating-point format. The dividend must be loaded into the A register prior to the execution of this instruction. The divisor is read from the storage location specified by the execution address. The quotient is rounded and normalized in the A register at the end of the operation. The residue from the rounding operation is left in the Q register at the end of the operation. A floating-point range fault produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

34 b k SCALE A (SCA) A left until

$$(A_{47}) \neq (A_{46})$$

or  $k = 0$

Reduce k by one per shift;  $k_f \rightarrow B^b$

This instruction shifts the quantity in the A register circularly to the left until the most significant digit is immediately to the right of the sign digit. The shift count k is reduced by the number of bit positions shifted. The shift is terminated if k becomes zero before the normalizing operation is completed. In any event the reduced shift count is then entered into the designated index register. The range of k is 0 through 7777<sub>8</sub>. The Shift Fault indicator is not affected by the execution of this instruction.

35 b k SCALE AQ (SCQ) AQ left until

$$(A_{47}) \neq (A_{46})$$

or  $k = 0$

Reduce k by one per shift;  $k_f \rightarrow B^b$

This instruction shifts the quantity in the AQ register circularly to the left until the most significant digit is immediately to the right of the sign digit. The shift count k is re-

duced by the number of bit positions shifted. The shift is terminated if k becomes zero before the normalizing operation is completed. In any event the reduced shift count is then entered into the designated index register. The range of k is 0 through 777778. The Shift Fault indicator is not affected by the execution of this instruction.

36 b m STORAGE SKIP (SSK)  $(M_{47})$  Neg: Exit  $(M_{47})$  Pos: Half Exit

This instruction senses the sign digit of the quantity in the storage location designated by the execution address. If the quantity is negative, an exit is performed. If the quantity is positive, a half exit is performed. None of the quantities in the operational registers are modified by this instruction.

37 b m STORAGE SHIFT (SSH)

$$(M_{47})$$

Neg: Exit, Shift Left One  $(M_{47})$  Pos: Half Exit, Shift Left One

This instruction senses the sign digit of the quantity in the storage location designated by the execution address. If the quantity is negative, an exit is performed. If the quantity is positive, a half exit is performed. In either case the quantity in storage is then shifted circularly to the left one bit position. None of the quantities in the operational registers are modified by this instruction.

40 b m SELECTIVE SET (SST) SET  $(A_n) = 1$  for  $(M_n) = 1$

This instruction sets individual bits of the A register to one where there are corresponding ones in the quantity in the storage location designated by the execution address. This is a bit-by-bit function and does not involve normal addition. Bits in the Accumulator corresponding to zeros in the operand are not modified. This is the inclusive "or" function.

41 b m SELECTIVE CLEAR (SCL) Clear  $(A_n)$  to zero for  $(M_n) = 1$

This instruction clears individual bits of the A register to zero where there are corresponding ones in the quantity in the storage location designated by the execution address. This is a bit-by-bit function and does not involve normal addition. Bits in A corresponding to zeros in the operand are not modified.

42 b m SELECTIVE COMPLEMENT (SCM) Complement  $(A_n)$  for  $(M_n) = 1$

This instruction complements individual bits of the A register where there are ones in the quantity in the storage location designated by the execution address. This is a bitby-bit function and does not involve normal addition. Bits in A corresponding to zeros in the operand are not modified. This is the exclusive "or" function.

43 b m SELECTIVE SUBSTITUTE (SSU)  $(M_n) \rightarrow A_n$  for  $(Q_n) = 1$

This instruction substitutes portions of an operand into the A register using the Q register contents as a mask. This may be considered in two steps. Individual bits of the A register are cleared to zero where there are ones in corresponding bits of the Q register. Then those same individual bits of the A register are replaced with corresponding bit values from the storage location specified by the execution address.

44 b m LOAD LOGICAL (LDL)  $L(Q)(M) \rightarrow A$

This instruction loads the A register with the bit-by-bit logical product of the Q register contents and the quantity in the storage location designated by the execution address.

45 b m ADD LOGICAL (ADL)

$$\left[ (A) + L(Q) (M) \right] \rightarrow A$$

This instruction adds to the A register contents the logical product of the Q register contents and the quantity in the storage location designated by the execution address. This is a normal addition of the selected portion of the operand with all other bits interpreted as zero. Occurrence of an overflow condition produces an interrupt (if so selected) and sets an indicator which may be sensed by an external function instruction.

46 b m SUBTRACT LOGICAL (SBL)

$$[(A) - L(Q) (M)] \rightarrow A$$

This instruction subtracts from the A register contents the logical product of the Q register contents and the quantity in the storage location designated by the execution address. This is a normal subtraction operation for the selected portion of the operand with all other bits interpreted as zero. Occurrence of an overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

47 b m STORE LOGICAL (STL)  $L(Q)(A) \rightarrow M$

This instruction stores the logical product of the A register and the Q register contents at the storage location specified by the execution address. Neither the A nor the Q register contents are modified by this instruction.

50 b y ENTER INDEX (ENI)  $y \rightarrow B^b$

This instruction replaces the contents of the designated index register with the operand y contained in the instruction itself. No storage reference is made in this instruction. If zero is used as the index designator, this instruction becomes the pass instruction.

| 51 b y | INCREASE INDEX | (INI) | $ y + (B^b)  \longrightarrow B^b$ |

|--------|----------------|-------|-----------------------------------|

|--------|----------------|-------|-----------------------------------|

This instruction adds the operand y to the contents of the designated index register. The addition is performed modulus  $2^{15}$  minus one. No storage reference is made in this instruction.

٦

52 b m<sub>u</sub> LOAD INDEX (upper) (LIU)  $(m_{UA}) \rightarrow B^b$

This instruction replaces the contents of the designated index register with the address from the upper instruction at the designated storage location.

53 b m<sub>1</sub> LOAD INDEX (lower) (LIL)  $(m_{LA}) \rightarrow B^b$

This instruction replaces the contents of the designated index register with the address from the lower instruction at the designated storage location.

54 b y INDEX SKIP (ISK)

$$(B^b) = y$$

: Exit, Clear  $B^b$

$(B^b) \neq y$ : Adv  $(B^b)$ , Half Exit

This instruction compares the quantity in the designated index register with the operand, y. If the two quantities are equal, then the designated index register is cleared to zero and an exit is performed. If the quantity in the index register is not equal to y, then the quantity in the index register is increased one count and a half exit is performed.

55 b m INDEX JUMP (IJP) (B<sup>b</sup>)  $\neq$  0: Reduce (B<sup>b</sup>), Jump to m (B<sup>b</sup>) = 0: Execute NI

This instruction examines the quantity in the designated index register. If this quantity is not zero, then the quantity is reduced one count and a jump is executed to the base

execution address. If this quantity is zero, then the present program sequence is continued.

56 b

$$m_u$$

STORE INDEX (Upper) (SIU) (B<sup>b</sup>)  $\rightarrow m_{UA}$

This instruction stores the quantity in the designated index register in the address portion of the upper instruction contained in the storage location specified by the base execution address. The remaining bits at the specified storage location are not modified in this operation. This instruction effectively inserts an address in the first instruction at the specified storage location.

57 b m<sub>1</sub> STORE INDEX (lower) (SIL)  $(B^b) \rightarrow m_{LA}$

This instruction stores the quantity in the designated index register in the address portion of the lower instruction contained in the storage location specified by the base execution address. The remaining bits at the specified storage location are not modified in this operation. This instruction effectively inserts an address in the second instruction at the specified storage location.

60 b m<sub>u</sub> SUBSTITUTE ADDRESS (upper) (SAU)  $(A_{00-14}) \rightarrow M_{IIA}$

This instruction replaces the address portion of the upper instruction word in the storage location designated by the execution address with the lowest order 15 bits of the A register contents. The remaining bits of the designated word in storage are not modified by this operation. This instruction effectively inserts an address in the first instruction at the designated storage location. The contents of A are not modified by this instruction.

61 b m<sub>1</sub> SUBSTITUTE ADDRESS (lower) (SAL)

$$(A_{00-14}) \rightarrow M_{LA}$$

This instruction replaces the address portion of the lower instruction word in the storage location designated by the execution address with the lowest order 15 bits of the A register contents. The remaining bits of the designated word in storage are not modified by this operation. This instruction effectively inserts an address in the second instruction at the designated storage location. The contents of A are not modified by this instruction.

62 b m INPUT TRANSFER (INT) Transfer (B<sup>b</sup>) words to memory, beginning at the last address

This instruction transfers a block of data from an external equipment into the central computer storage. The number of words to be transferred is specified by the contents of the designated index register, B<sup>b</sup>. These words are located in a consecutive list which begins at the location specified by the base execution address, m. The transfer begins by storing the first word in the last position in the list. The content of the designated index register is reduced by one for each word that is transferred. The transfer continues until the contents of the designated index register are reduced to zero.

63 b m OUTPUT TRANSFER (OUT) Transfer (B<sup>b</sup>) words from memory, beginning with the last address

This instruction transfers a block of data from computer storage to an external equipment. The number of words to be transferred is specified by the contents of the designated index register, B<sup>b</sup>. The words to be transferred are located in a consecutive list which begins at the location specified by the execution address, m. The transfer begins by obtaining the first word from the last position in the list. The content of the designated index register is reduced by one for each word that is transferred. The transfer continues until the contents of the designated index register are reduced to zero.

64 b m

Search  $(B^b)$  words, beginning with

the last word

This instruction searches a list of operands to find one that is equal to the content of the A register. The number of items in the list is specified by the content of the designated index register. These items are located in a consecutive list beginning at the location specified by the base execution address. The search begins with the last operand in the list. The content of the designated index register is reduced by one for each operand examined. The search continues until an operand is reached that is equal to the content of the A register or until the contents of the designated index register are reduced to zero. If the search is terminated by finding an operand equal to the value in A, an exit is performed. The address of the operand which satisfied the criterion is given by the sum of the base execution address and the final contents of the index register. If no operand in the list is equal to the value in A, then a half exit is performed. If b = 0, only the word at m is searched. In the equality comparison made here, plus zero (that is, all zeros) and minus zero (that is, all ones) are treated as equal.

65 b m THRESHOLD SEARCH (THS) Search (B<sup>b</sup>) words, beginning with the last word (M) > (A): Exit

This instruction searches a list of operands to find one that is greater than the contents of the A register. The number of items in the list is specified by the contents of the designated index register. These items are located in a consecutive list beginning at the location specified by the base execution address. The search begins with the last operand in the list. The content of the designated index register is reduced by one for each operand

examined. the search continues until an operand is reached that is greater than the content of the A register or until the contents of the designated index register are reduced to zero. If the search is terminated by finding an operand greater than the value in A, an exit is performed. The address of the operand which satisfied the criterion is given by the sum of the base execution address and the final contents of the index register. If no operand in the list is greater than the value in A, then a half exit is performed. If b = 0, only the word at m is searched. In the comparison made here plus zero is considered as greater than minus zero.

66 b m MASKED EQUALITY (MEQ) Search  $(B^b)$  words beginning with the last word L(Q) (M) = (A): Exit

This instruction searches a list of operands to find one such that the logical product of the operand and the contents of the Q register (that is, the masked operand) is equal to the contents of the A register. The number of items in the list is specified by the content of the designated index register. These items are located in a consecutive list beginning at the location specified by the base execution address. The search begins with the last operand in the list. The content of the designated index register is reduced by one for each operand examined. The search continues until an operand is reached that, when masked, is equal to the value in the A register, or until the contents of the designated index register are reduced to zero. If the search is terminated by finding a masked operand that is equal to the value in A, an exit is performed. The address of the operand which satisfied the criterion is given by the sum of the base execution address and the final contents of the index register. If no operand in the list satisfies the criterion then a half exit is performed. If b = 0, only the word at m is searched.

the last word L(Q)(M) > A: Exit

The instruction searches a list of operands to find one such that the logical product of the operand and the contents of the Q register (that is, the masked operand) is greater than the contents of the A register. The number of items in the list is specified by the contents of the designated index register. These items are located in a consecutive list beginning at the location specified by the base execution address. The search begins with the last operand in the list. The content of the designated index register is reduced by one for each operand examined. The search continues until an operand is reached that, when masked, is greater than the value in the A register or until the contents of the designated index register are reduced to zero. If the search is terminated by finding a masked operand that is greater than the value in A, an exit is performed. The address of the operand which satisfied the criterion is given by the sum of the base execution address and the final contents of the index register. If no operand in the list satisfied the criterion then a half exit is performed. If b = 0, only the next word at m is searched.

70 b m REPLACE ADD (RAD)  $\left[ (M) + (A) \right] \rightarrow M \& A$

This instruction replaces the quantity specified by the execution address with its original value plus the value in the A register. The resultant sum is left in the A register at the end of the operation. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

71 b m REPLACE SUBTRACT (RSB)

$$\left[ (M) - (A) \right] \rightarrow M \& A$$

This instruction replaces the quantity specified by the execution address with its original value minus the value in the A register. The resultant difference is left in the A register at the end of the operation. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

72 b m REPLACE ADD ONE (RAO)  $[(M) + 1] \rightarrow M \& A$

This instruction replaces the quantity specified by the execution address with its original value plus one. The resultant quantity is left in the A register at the end of the operation. The original A register contents are destroyed by this operation. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

73 b m REPLACE SUBTRACT ONE (RSO)  $[(M) - 1] \rightarrow M \& A$

This instruction replaces the quantity specified by the execution address with its original value minus one. The resultant quantity is left in the A register at the end of the operation. The original A register contents are destroyed by this operation. An overflow condition produces an interrupt (if selected) and sets an indicator which may be sensed by an external function instruction.

74 j y EXTERNAL FUNCTION (EXF)

$$j = 1-6$$

: activate channel j

$j = 0$ : select condition y

$j = 7$ : on condition y exit or

half exit

This instruction has eight sub-instructions which are used to control the transfer of

information between the computer and peripheral equipments. The index registers are not used for address modification in this instruction. The designator is used to specify one of eight external functions to be performed.

The sub-instructions and the operation performed for each are as follows:

74 0 y - Select external equipment or internal condition, y

74 1 y - Activate communication channel one

74 2 y - Activate communication channel two

74 3 y - Activate communication channel three

74 4 y - Activate communication channel four

74 5 y - Activate communication channel five

74 6 y - Activate communication channel six

74 7 y - Sense external or internal condition, y

Sub-instructions 74 1 y through 74 6 y are used to begin buffering a block of data between the computer and a previously selected peripheral equipment. The base execution address is used to designate the starting address in the computer central storage. This address is automatically recorded in the upper address position of the appropriate special storage location (00001-00006). The terminal address (plus one) of the block of data must have been previously recorded, by the program, in the lower address position of the appropriate special storage location prior to the execution of this external function instruction.

Sub-instructions 74 0 y and 74 7 y are used to provide the selection  $(74 \ 0 \ y)$  and sensing  $(74 \ 7 \ y)$  of a multiplicity of internal and external conditions or modes of operations. The 24 bit instruction is interpreted as follows:

| 6 bits  | 3 bits     | 3 bits        | 3 bits    | 9 bits       |

|---------|------------|---------------|-----------|--------------|

| OP Code | 0 = Select | 0 = Internal  | Equipment | Condition or |

| 74      | 7 = Sense  | 1-6 = Channel | 0-7       | Mode 000-777 |

Sub-instructions 74 0 y and 74 7 y may be used as either upper or lower instructions. The Select sub-instruction (74 0 y) will yield the same result in either case. However, the Sense sub-instruction (74 7 y) causes a skip or a wait depending upon its position in the 1604 Computer word.

When used in the upper position, a 74 7 y is a skip instruction. That is, the lower instruction is skipped if the condition given by the EF code is present, but the lower instruction is executed if the condition given by the EF code is not present. In the first case, the 74 7 y "exits" to the next pair of instructions. In the second case the 74 7 y "half exits" to the lower instruction.

When the 74 7 y is used in the lower position, it is not a skip instruction. Instead the sense is executed repeatedly until the condition given by the EF code occurs. At this time an exit is performed to the next pair of instructions. Until the condition given by the EF code is present, the instruction simply half exits to repeat itself. A 74 7 y in the lower position is therefore a means of awaiting the occurrence of a specified condition.

Throughout the list of sense codes below, the term "exit" and "half exit" applies as indicated above. An exit is performed if the stated condition is present; if not present, a half exit is performed.

#### Internal Condition

Internal Select

- 74 0 00010 Select interrupt on channel 1 inactive

- 74 0 00011 Remove selection

- 74 0 00020 Select interrupt on channel 2 inactive

- 74 0 00021 Remove selection

- 74 0 00030 Select interrupt on channel 3 inactive

Internal Select (cont.)

- 74 0 00031 Remove selection

- 74 0 00040 Select interrupt on channel 4 inactive

- 74 0 00041 Remove selection

- 74 0 00050 Select interrupt on channel 5 inactive

- 74 0 00051 Remove selection

- 74 0 00060 Select interrupt on channel 6 inactive

- 74 0 00061 Remove selection

- 74 0 00070 Clear arithmetic faults

- 74 0 00100 Select interrupt on arithmetic fault

- 74 0 00101 Remove selection

- 74 0 01000 Start clock

- 74 0 02000 Stop clock

## Internal Sense

- 74 7 00010 Exit on channel 1 active

- 74 7 00011 Exit on channel 1 inactive

- 74 7 00020 Exit on channel 2 active

- 74 7 00021 Exit on channel 2 inactive

- 74 7 00030 Exit on channel 3 active

- 74 7 00031 Exit on channel 3 inactive

- 74 7 00040 Exit on channel 4 active

- 74 7 00041 Exit on channel 4 inactive

- 74 7 00050 Exit on channel 5 active

- 74 7 00051 Exit on channel 5 inactive

- 74 7 00060 Exit on channel 6 active

- 74 7 00061 Exit on channel 6 inactive

- 74 7 00110 Exit on divide fault

- 74 7 00111 Exit on no divide fault

- 74 7 00120 Exit on shift fault

- 74 7 00121 Exit on no shift fault

- 74 7 00130 Exit on overflow fault

- 74 7 00131 Exit on no overflow fault

- 74 7 00140 Exit on exponent fault

- 74 7 00141 Exit on no exponent fault

## External Equipment

### External Clear

- 74 0 10000 Clear all channel 1 selections

- 74 0 20000 Clear all channel 2 selections

- 74 0 30000 Clear all channel 3 selections

- 74 0 40000 Clear all channel 4 selections

- 74 0 50000 Clear all channel 5 selections

- 74 0 60000 Clear all channel 6 selections

# **Console Select**

- 74 0 11100 Keyboard entry and no interrupt on carriage return

- 74 0 11140 Keyboard entry and interrupt on carriage return

- 74 0 11200 PT reader and no interrupt on end-of-tape

- 74 0 11210 PT reader and end-of-tape indicator

- 74 0 11220 PT reader and interrupt on end-of-tape

- 74 0 21100 Print assembly mode

- 74 0 21110 Print character mode

- 74 0 21200 Punch assembly mode

- 74 0 21210 Punch character mode

- 74 0 21240 Turn punch motor off

## Console Sense

- 74 7 11100 Exit on keyboard carriage return

- 74 7 11101 Exit on no keyboard carriage return

- 74 7 11140 Exit on keyboard lower case

- 74 7 11141 Exit on keyboard upper case

Console Sense (cont.)

74 7 11200 - Exit on PT reader, end-of-tape

74 7 11201 - Exit on PT reader, no end-of-tape

74 7 11210 - Exit on PT reader, assembly mode

74 7 11211 - Exit on PT reader, character mode

74 7 21200 - Exit on punch, end-of-tape

74 7 21201 - Exit on punch, no end-of-tape

1607 Magnetic Tape System - Select

Typically, the 1607 Magnetic Tape System is connected to channels 3 and 4. Thus the channel selection code is 3 or 4. The variable "n" is used to specify one of the four tape units by being assigned a value 1 through 4. The codes are so arranged that tape unit n is selected for an input or output channel operation on the initial selection only; subsequent selector sense operations on the unit do not require the n designator. The n designator is required when changing operations from one tape unit to another. Various conditions, including errors arising in the operation of the tape system, may be sensed by the external sense codes.

- 74 0 32001 Read selected tape, binary

- 74 0 32002 Read selected tape, coded

- 74 0 32004 Interrupt when selected tape ready

- 74 0 32005 Rewind selected tape

- 74 0 32006 Backspace selected tape

- 74 0 32007 Rewind selected tape with interlock

- 74 0 320n1 Select read tape n, binary

- 74 0 320n2 Select read tape n, coded

- 74 0 42001 Write selected tape, binary

- 74 0 42002 Write selected tape, coded

- 74 0 42003 Write end-of-file mark on selected tape

- 74 0 42004 Interrupt when selected tape ready

- 74 0 42005 Rewind selected tape

- 74 0 42006 Backspace selected tape

- 74 0 42007 Rewind selected tape with interlock

- 74 0 420n1 Select write tape n, binary

- 74 0 420n2 Select write tape n, coded

- 1607 Magnetic Tape System Sense

- 74 7 32000 Exit on ready to read

- 74 7 32001 Exit on not ready to read

- 74 7 32002 Exit on read parity error

- 74 7 32003 Exit on no read parity error

- 74 7 32004 Exit on read length error

- 74 7 32005 Exit on no read length error

- 74 7 32006 Exit on end of file mark

- 74 7 32007 Exit on no end of file mark

- 74 7 42000 Exit on ready to write

- 74 7 42001 Exit on not ready to write

- 74 7 42002 Exit on write reply parity error

- 74 7 42003 Exit on no write reply parity error

- 74 7 42004 Exit on write reply length error

- 74 7 42005 Exit on no write reply length error

1607 Magnetic Tape System - Sense (cont.)

74 7 42006 - Exit on end-of-tape marker

74 7 42007 - Exit on no end-of-tape marker

1605 Adaptor - Select

The condition interpretation codes used with the 1605 Adaptor, select and control the operation of the various IBM equipments connected to the Adaptor. The channel selection code is 5 or 6. The variable "n" is used to specify one of a number of similar units of a single class.

74 0 54000 - Begin cycle or read selected tape, binary

74 0 54001 - Read selected tape, coded

- 74 0 54002 Select read, binary, for read-while-write

- 74 0 54003 Select read, coded, for read-while-write

- 74 0 54005 Rewind selected tape

- 74 0 54006 Backspace selected tape

- 74 0 54007 Interrupt when selected unit ready

- 74 0 54100 Turn on indicator, selected unit

- 74 0 54101 Turn off indicator, selected unit

- 74 0 54200 Clear Interrupt Selection

- 74 0 544n0 Read tape n, binary

- 74 0 544n1 Read tape n, coded

- 74 0 544n2 Select read tape n, binary, for read-while-write

- 74 0 544n3 Select read tape n, coded, for read-while-write

- 74 0 54500 Begin cycle card reader, binary

- 74 0 54501 Begin cycle card reader, coded

- 74 0 64000 Begin cycle or write selected tape, binary

- 74 0 64001 Write selected tape, coded

1605 Adaptor - Select (cont.)

74 0 64004 - Write end-of-file, selected tape

74 0 64005 - Rewind selected tape

74 0 64006 - Backspace selected tape

74 0 64007 - Interrupt when selected unit ready

74 0 64200 - Clear interrupt selection

74 0 64100 - Turn on indicator, selected unit

74 0 64101 - Turn off indicator, selected unit

74 0 644n0 - Write tape n, binary

74 0 644n1 - Write tape n, coded

74 0 64600 - Begin cycle card punch, coded

- 74 0 64601 Begin cycle card punch, binary

- 74 0 64700 Begin cycle line printer

1605 Adaptor - Sense

The following sense codes are used with the 1605 Adaptor. The indicator is always received from the selected IBM unit. An indicator from the card reader indicates that the card feed is empty. From a magnetic tape unit, it indicates either end-of-tape (for a write operation) or end-of-file (for a read operation). An indicator from the line printer indicates the end-of-page. No indicator is received from the card punch.