# ·1607 MAGNETIC TAPE SYSTEM Volume 1: DESCRIPTION AND OPERATION

# **INSTRUCTION BOOK**

# **1607 MAGNETIC TAPE SYSTEM**

Volume 1: DESCRIPTION AND OPERATION

## **INSTRUCTION BOOK**

PUBLICATION 037B

rev. 10/15/61

## GENERAL TABLE OF CONTENTS

Volume 1 Description and Operation

Chapter 1 General Description

2 Operation

3 Principles of Operation

Volume 2 Maintenance

Chapter 1 Maintenance

2 File of Equations

3 Parts List

4 Equipment Diagrams

ii

## TABLE OF CONTENTS

#### Chapter 1 General Description

| Intro              | duction                                       | 1-1  |

|--------------------|-----------------------------------------------|------|

| Phys               | ical Description                              | 1-1  |

|                    | netic Tape Characteristics                    | 1-3  |

| Basi               | c Principles of Operation                     | 1-5  |

|                    | External Function Instruction                 | 1-6  |

| Tables Chapter One |                                               | 1-11 |

|                    | nary of Data and Control Line Characteristics | 1-15 |

| Chapter 2          | Operation                                     |      |

| Introduction                        | 2-1 |

|-------------------------------------|-----|

| General Operating Instructions      | 2-1 |

| Tape Load Procedure                 | 2-1 |

| Tape Unload Procedure               | 2-3 |

| Supplementary Operating Information | 2-3 |

| Application of Power                | 2-3 |

| Cabinet Selection Switch            | 2-4 |

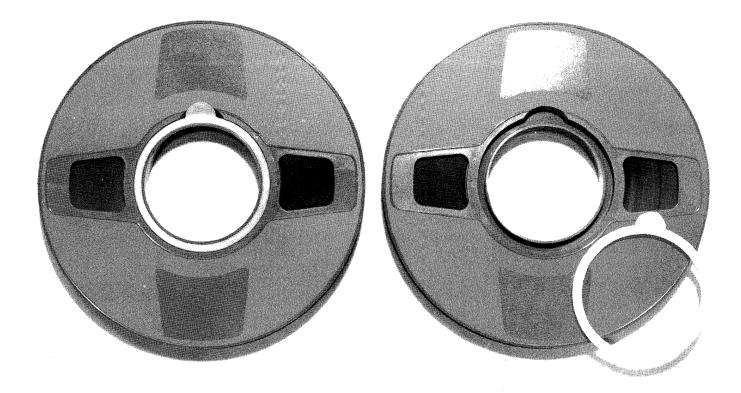

| File Protection Ring                | 2-4 |

| Attaching Reflective Spots          | 2-4 |

| Manual Operation                    | 2-6 |

| Manual Controls and Indicators      | 2-8 |

Chapter 3

Principles of Operation

| Intro     | oduction                        | 3-1  |

|-----------|---------------------------------|------|

|           | Presentation of Material        | 3-2  |

|           | Summaries of Reference Material | 3-2  |

| Desc      | cription of Logic Circuits      | 3-11 |

|           | Function Circuits               | 3-12 |

|           | Write Circuits                  | 3-27 |

|           | Read Circuits                   | 3-45 |

| Desc      | cription of Tape Operations     | 3-57 |

|           | Selection of a Tape Unit        | 3-57 |

|           | Select Operations               | 3-58 |

|           | Sense Operations                | 3-76 |

| Manu      | ual Controls                    | 3-78 |

| Powe      | er and Cooling Circuits         | 3-82 |

| Deta      | iled Circuit Descriptions       | 3-87 |

| Chapter 4 | Satellite System                |      |

| Gene      | eral Description                | 4-1  |

| General Description                  |  | 4-1 |

|--------------------------------------|--|-----|

| <b>Basic Principles of Operation</b> |  | 4-2 |

| Programming                          |  | 4-6 |

## FIGURES

| 1-1Magnetic Tape Systemvi1-2Rear View Magnetic Tape System Information Flow1-21-3Magnetic Tape System Information Flow1-51-5Over-all Magnetic Tape System1-19Chapter 2Operation2-22-1Tape at Change Tape Position2-22-2File Protection Ring2-52-3Physical Layout of Magnetic Tape2-7Chapter 3Principles of Operation3-13-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code(32011)3-9Tape Unit Control Signals3-213-11Sense Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disasembly Counter3-313-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-313-16Write Control, Tape Motion Circuit3-373-19Write Control, Tape Motion Circuit3-313-11Sensembly Counter3-313-12Interrupt Circuit3-243-13Simplified Block Diagram, Read Circuits3-443-14Di                                          | Chapter 1  | General Description                                            |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------|------------|

| 1-5Over-all Magnetic Tape System1-19Chapter 2Operation2-1Tape at Change Tape Position2-22-2File Protection Ring2-52-3Physical Layout of Magnetic Tape2-7Chapter 3Principles of Operation3-13-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code(32011)3-10Tape Unit Motion and Direction Control Circuit3-193-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-313-16Write Driver Circuit3-323-17Typical Unite Driver Circuit3-373-20Write Reply Parity Detector3-343-21Write Control, Tape Motion Circuit3-373-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-44 <trr>3-25Assembly Coun</trr>                      | 1-2<br>1-3 | Rear View Magnetic Tape System<br>Magnetic Tape Specifications | 1-2<br>1-4 |

| 2-1Tape at Change Tape Position2-22-2File Protection Ring2-52-3Physical Layout of Magnetic Tape2-7Chapter 3Principles of Operation3-13-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-133-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-123-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-393-18Write Generator3-393-21Write Reply Circuit3-443-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-35Storagement of Data on Tape3-433-31Write Reply Circuit3-473-23Simplifier Block Diagram3-633-34Read Control, Tap                                           | 1-5        |                                                                | 1-19       |

| 2-2File Protection Ring2-52-3Physical Layout of Magnetic Tape2-7Chapter 3Principles of Operation3-13-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Motion and Direction Control Circuit3-223-11Sense Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-313-16Write Ontrol, Tape Motion Circuit3-373-17Typical Write Driver Circuit3-313-18Write Generator3-393-21Write Reply Parity Detector3-443-22Arrangement of Data on Tape3-433-31Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-443-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Read Sequence Con       | Chapter 2  | Operation                                                      |            |

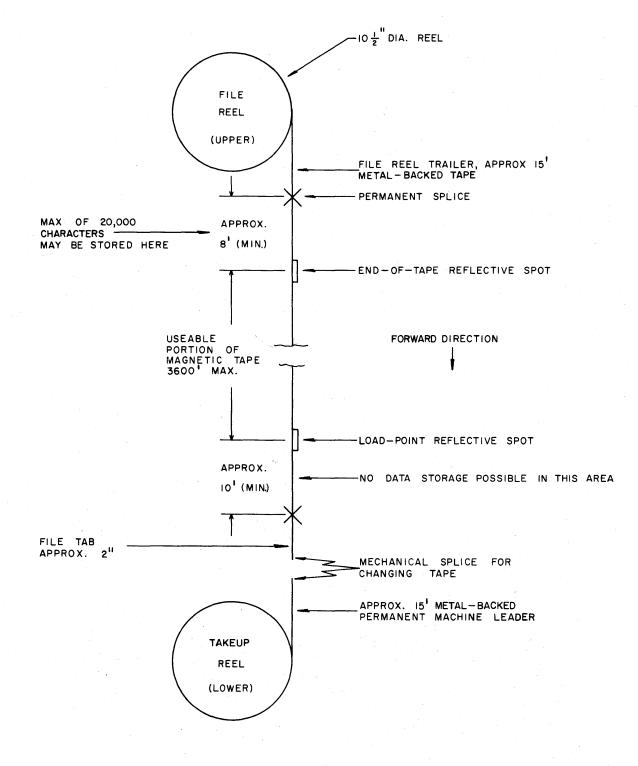

| 2-3Physical Layout of Magnetic Tape2-7Chapter 3Principles of Operation3-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code(32011)3-9Tape Unit Motion and Direction Control Circuit3-193-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-263-15Typical Line Translator Circuit and Bit Transfer to3-303-16Write Register3-303-17Typical Write Direver Circuit3-323-18Write Reply Parity Detector3-343-20Write Generator3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-443-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-443-25Assembly Counter and Translator3-493-26End-of-File Detector3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-443-23Simplified Block Diagram, Read Circuits3-44 <tr< td=""><td></td><td></td><td></td></tr<>         |            |                                                                |            |

| 3-1Simplified Block Diagram, Magnetic Tape System3-13-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-123-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-303-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-373-20Write Generator3-343-21Write Reply Parity Detector3-393-22Arangement of Data on Tape3-443-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-433-28Simplified Block Diagram, Read Circuits3-473-29Write Logic Diagram3-633-29Write Logic Diagram3-633-20 </td <td></td> <td></td> <td></td> |            |                                                                |            |

| 3-2Logic Diagram Symbols3-53-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-303-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-373-20Write Reply Parity Detector3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Tape Motion Circuit3-523-29Write Logic Diagram3-633-30Read Control, Read Sequence Control3-553-29<                                       | Chapter 3  | Principles of Operation                                        |            |

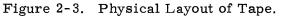

| 3-3Input and Output Conversions3-63-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-303-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-343-21Write Reply Parity Detector3-443-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Read Sequence Control3-553-28Read Control, Read Sequence Control3-513-29Write Logic Diagram3-633-30Read Logic Diagram3-613-31Unit Selection Switches3-793-32Manu                                           |            | Simplified Block Diagram,Magnetic Tape System                  |            |

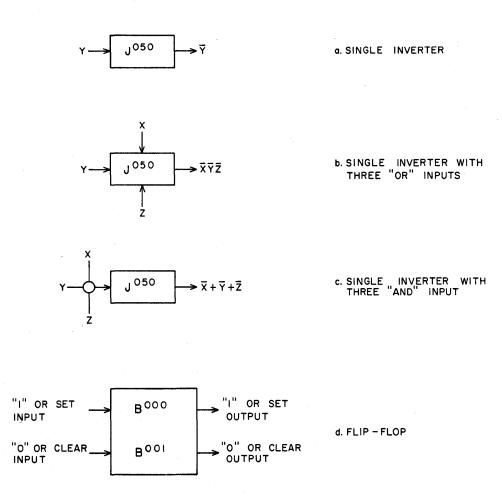

| 3-4Simplified Diagram, Computer Input/Output Section3-93-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-303-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Register3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-633-31Unit Selection Switches3-793-32Manual Controls3-78                                                                          | 3-2        | Logic Diagram Symbols                                          |            |

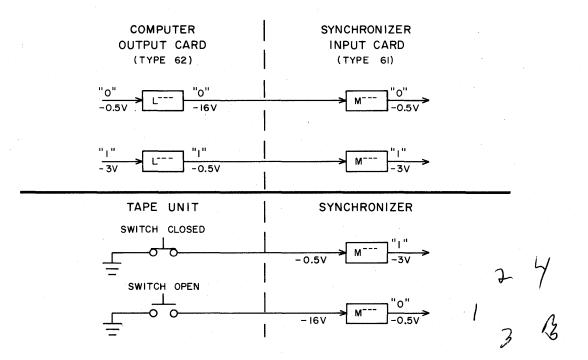

| 3-5Function Circuits3-103-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-373-20Write Reply Parity Detector3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-433-24Simplified Block Diagram, Read Circuits3-443-25Assembly Counter and Translator3-443-24Read Amplifier Circuits3-443-25Assembly Counter and Translator3-443-26Simplified Block Diagram, Read Circuits3-443-27Read Control, Tape Motion Circuit3-553-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-633-30Read Logic Diagram3-633-30Read Logic Diagram3-633-30Read Logic Diagram                                           | 3-3        | Input and Output Conversions                                   |            |

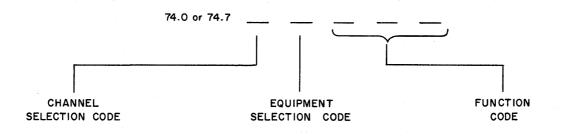

| 3-6Translation of Equipment Selection Code3-123-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-343-18Write Reply Parity Detector3-343-20Write Generator3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-443-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuit3-513-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Read Sequence Control3-553-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-633-30Read Logic Diagram3-633-31Juit Selection Switches3-793-32Manual Controls3-58                                                                                                                        | 3-4        | Simplified Diagram, Computer Input/Output Section              |            |

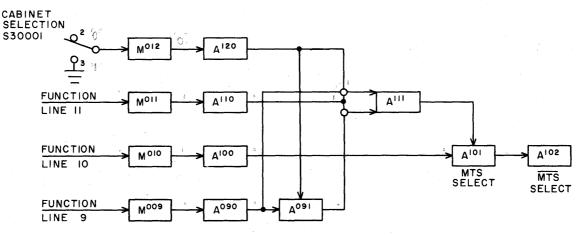

| 3-7Typical Select Code Translating Circuit3-133-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-78                                                                                                                                                                        | 3-5        | Function Circuits                                              |            |

| 3-8Storage of Select Read Tape Unit 1 in Binary EF Code<br>(32011)3-173-9Tape Unit Motion and Direction Control Circuit3-173-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Generator3-393-20Write Generator3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                               | 3-6        | Translation of Equipment Selection Code                        |            |

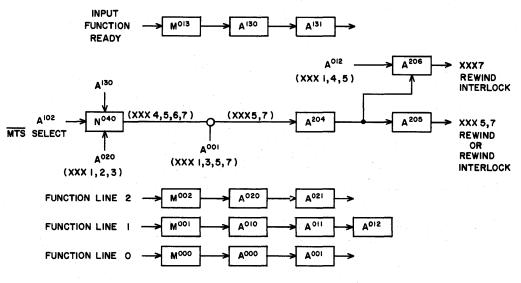

| (32011)3-173-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-633-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                 | 3-7        | Typical Select Code Translating Circuit                        | 3-13       |

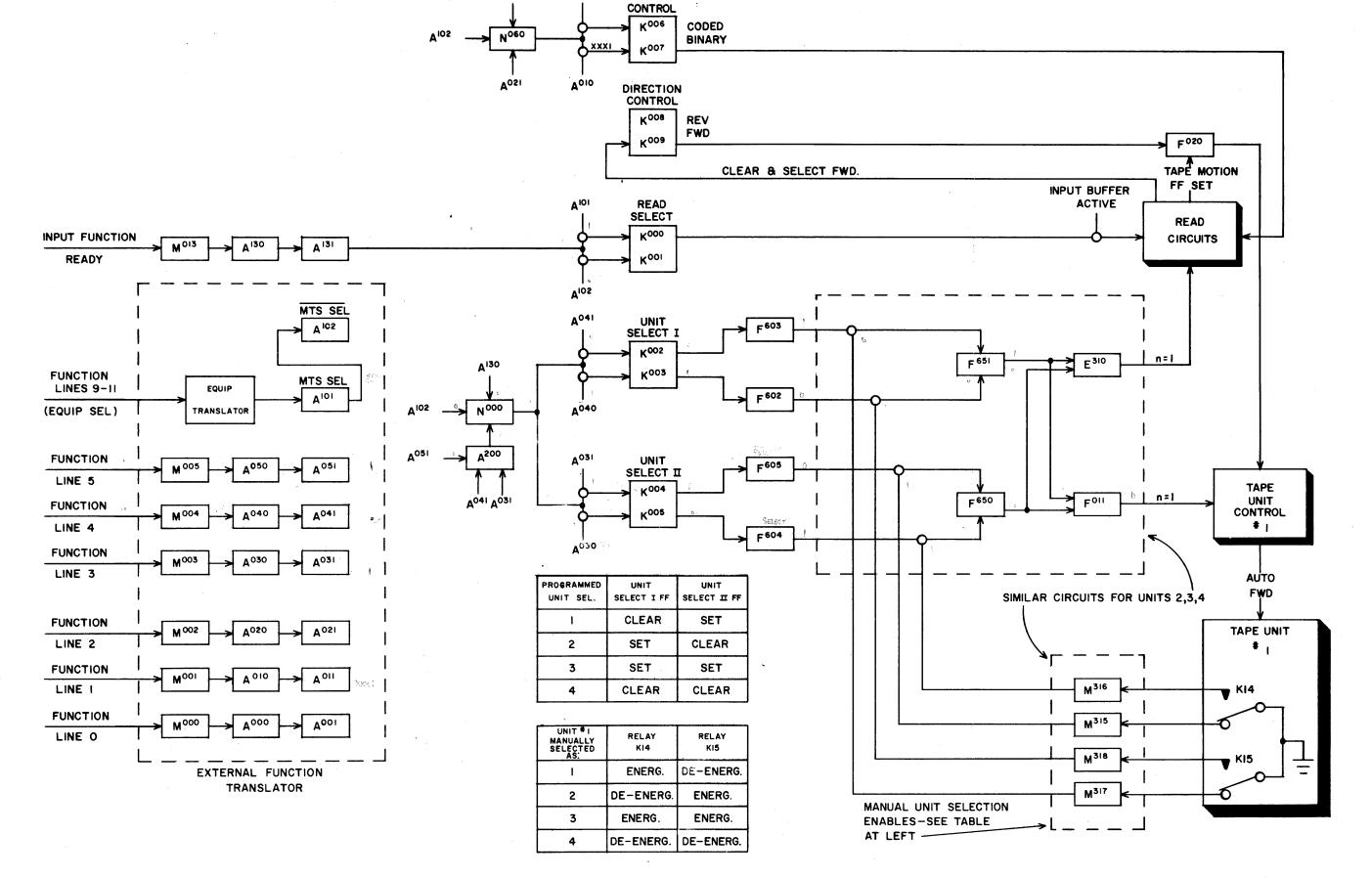

| 3-9Tape Unit Motion and Direction Control Circuit3-193-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-443-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-493-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Tape Motion Circuit3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                    | 3-8        | Storage of Select Read Tape Unit 1 in Binary EF Code           |            |

| 3-10Tape Unit Control Signals3-213-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                       |            | (32011)                                                        | 3-17       |

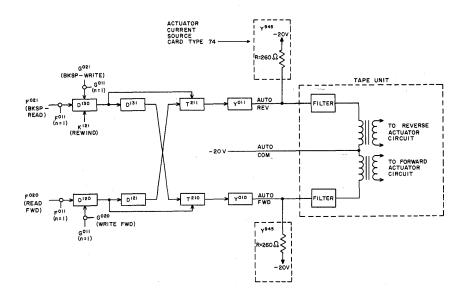

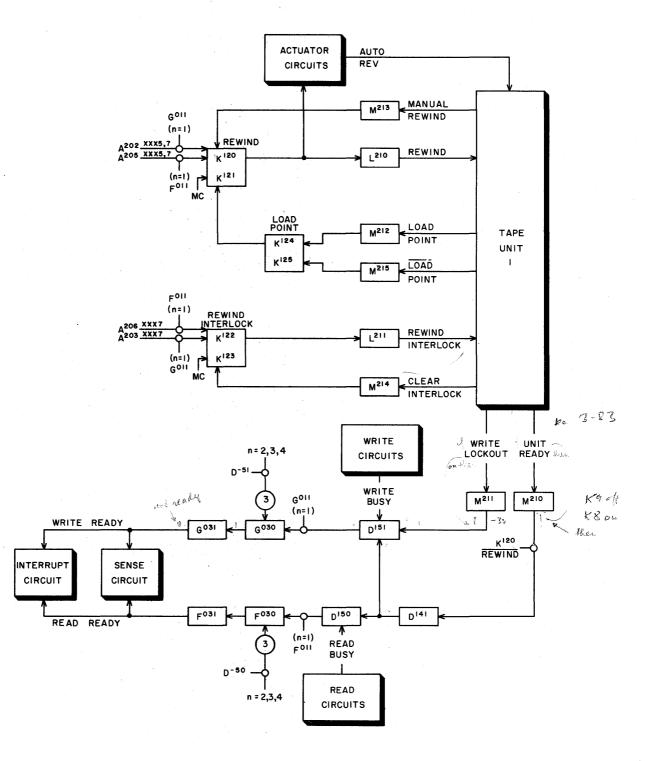

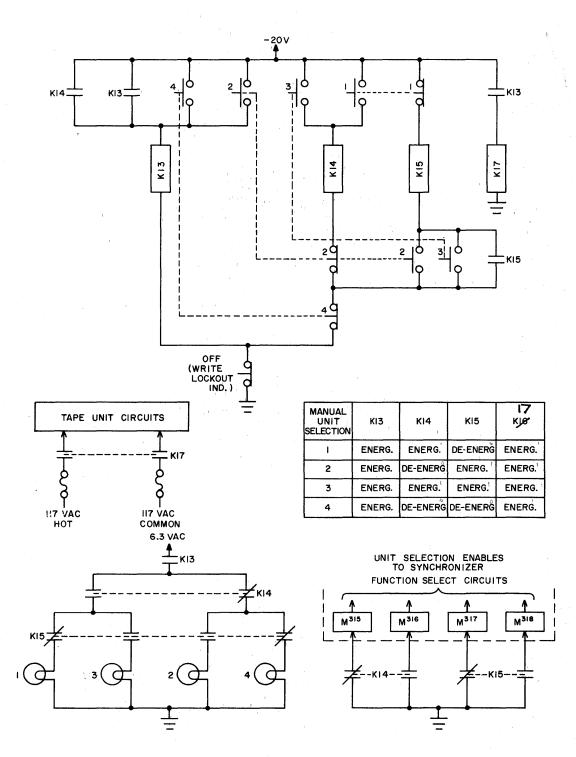

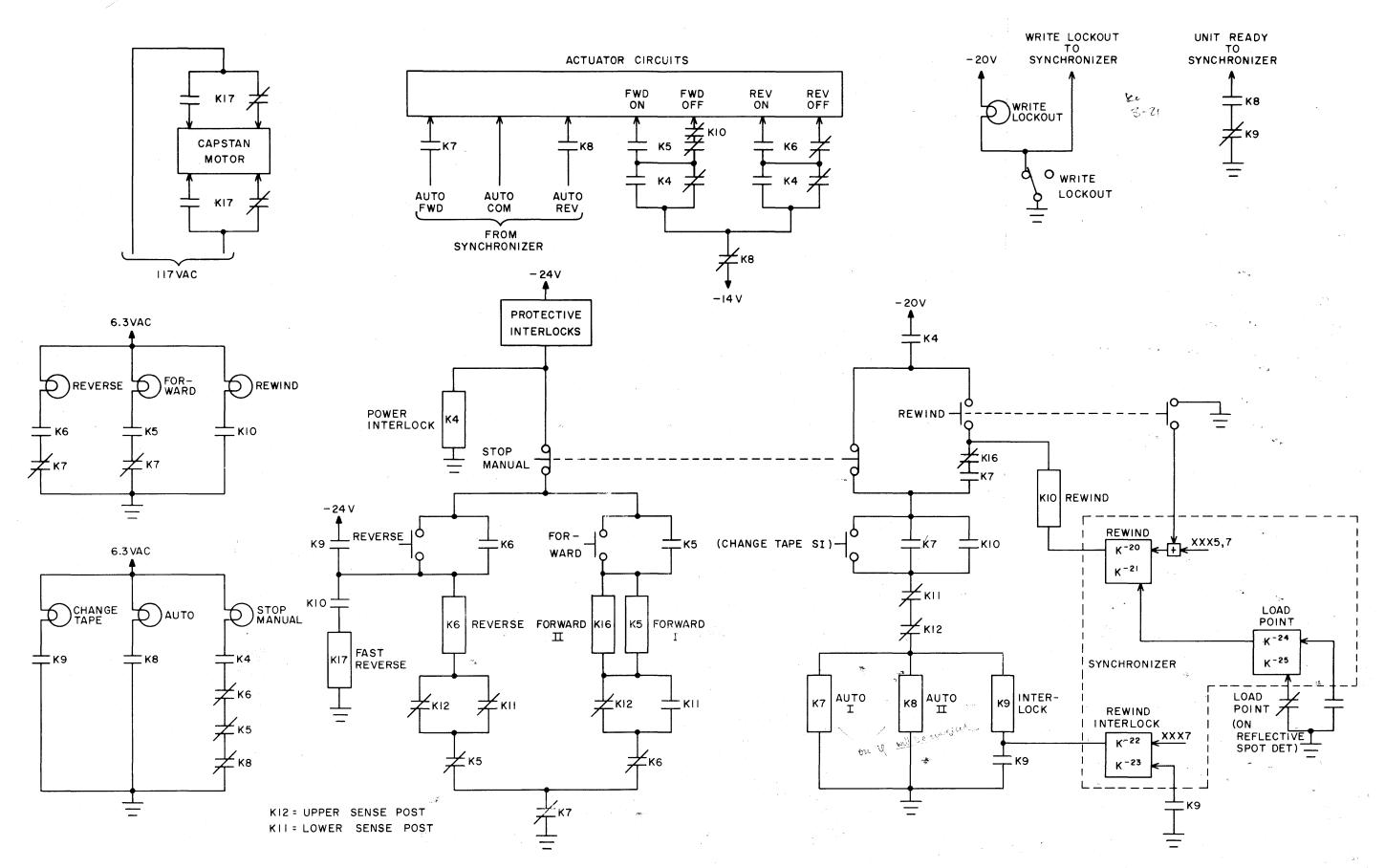

| 3-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Register3-303-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-433-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-633-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                | 3-9        | Tape Unit Motion and Direction Control Circuit                 | 3-19       |

| 3-11Sense Circuit3-223-12Interrupt Circuit3-243-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-633-31Unit Selection Switches3-793-32Manual Controls3-53                                                                                                                                                                                                                                                                                                                                        | 3-10       | Tape Unit Control Signals                                      | 3-21       |

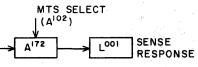

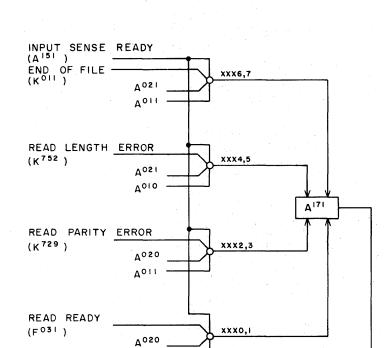

| 3-13Simplified Block Diagram, Write Circuits3-263-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                      | 3-11       |                                                                | 3-22       |

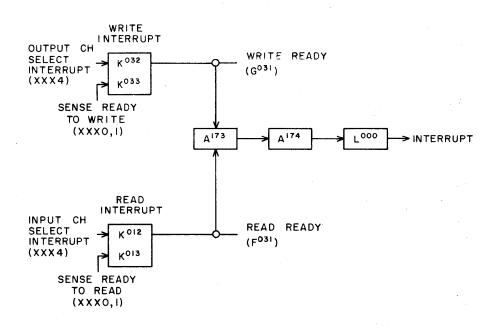

| 3-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-12       | Interrupt Circuit                                              | 3-24       |

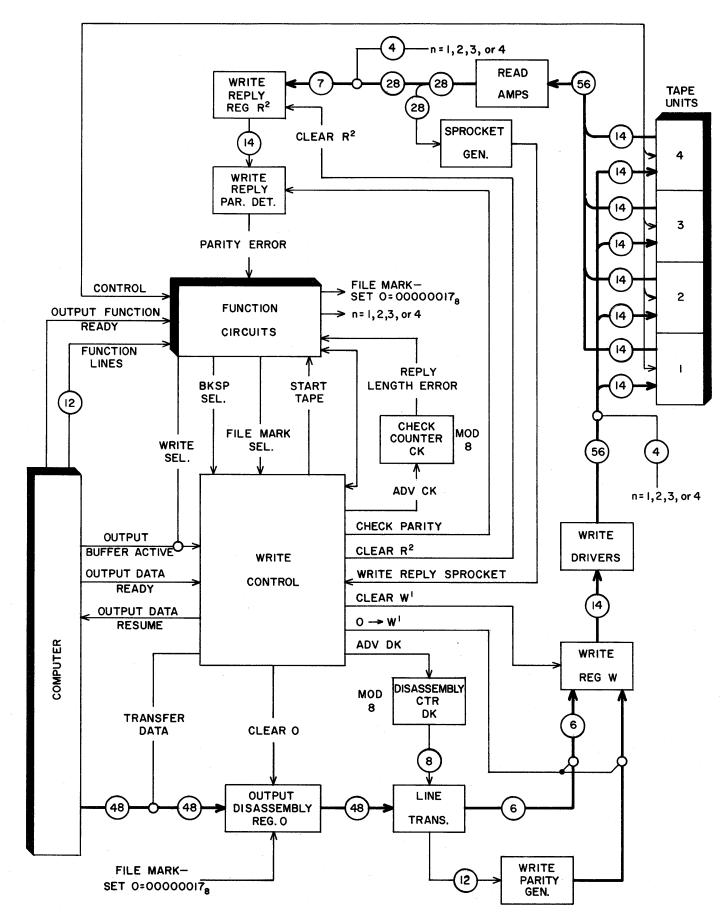

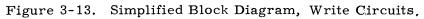

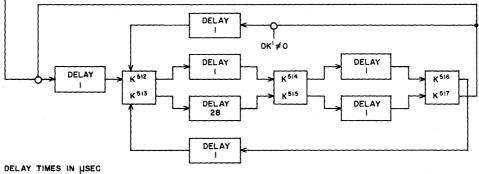

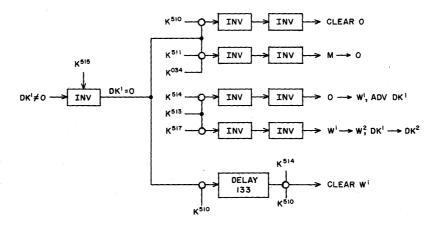

| 3-14Disassembly Counter3-283-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-523-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-53                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-13       | Simplified Block Diagram, Write Circuits                       | 3-26       |

| 3-15Typical Line Translator Circuit and Bit Transfer to<br>Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                                | 3-28       |

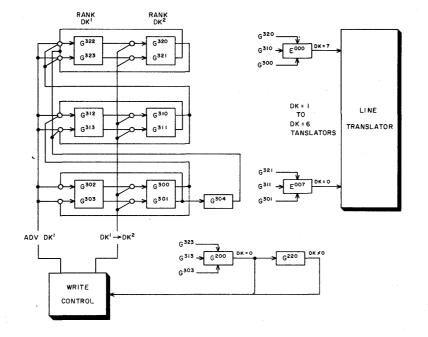

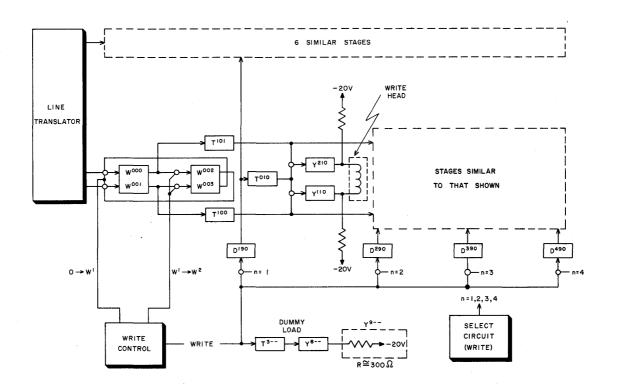

| Write Register3-303-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-15       |                                                                |            |

| 3-16Write Parity Generator3-313-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-473-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |                                                                | 3-30       |

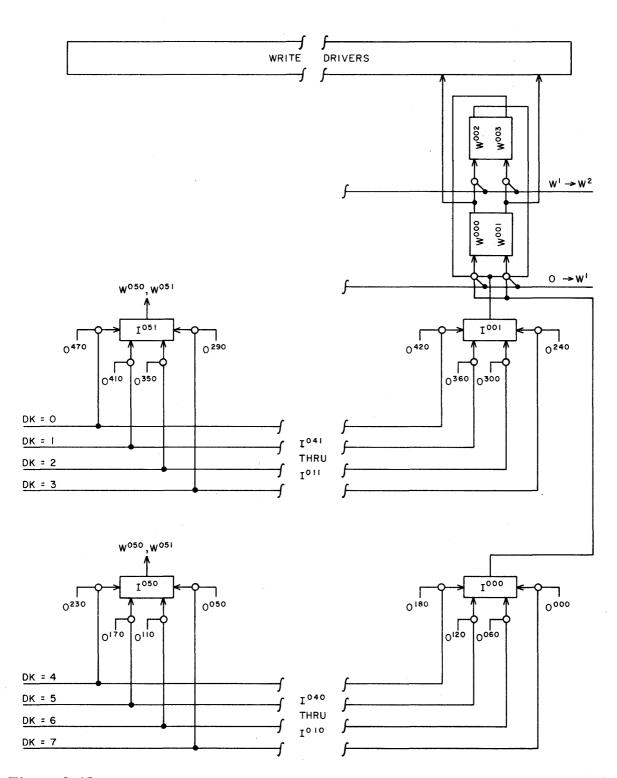

| 3-17Typical Write Driver Circuit3-323-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-16       |                                                                | 3-31       |

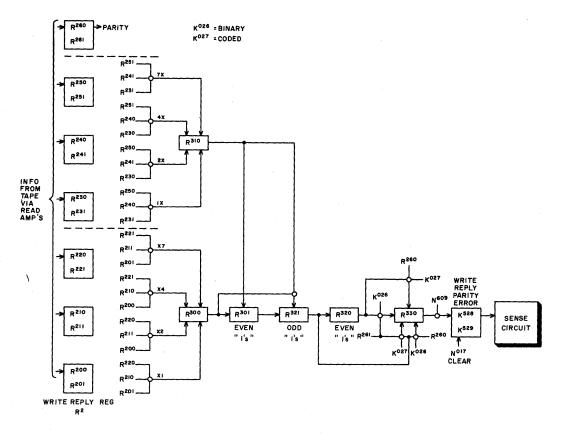

| 3-18Write Reply Parity Detector3-343-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-17       |                                                                | 3-32       |

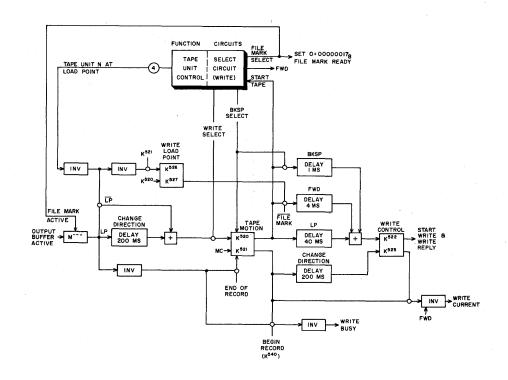

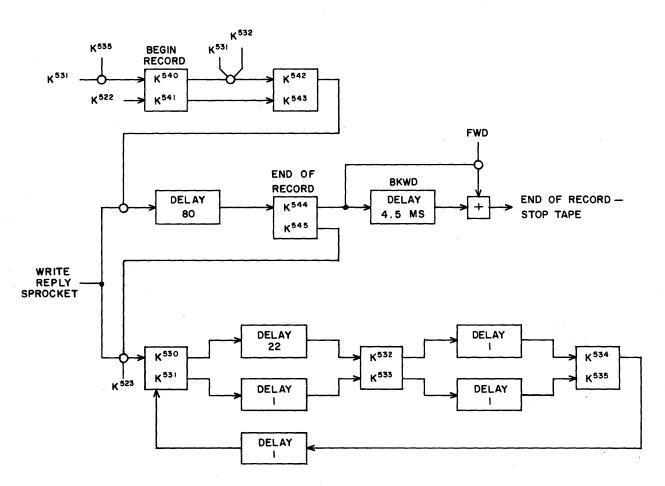

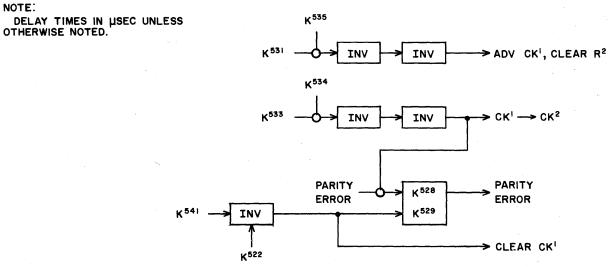

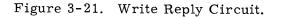

| 3-19Write Control, Tape Motion Circuit3-373-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-18       |                                                                | 3-34       |

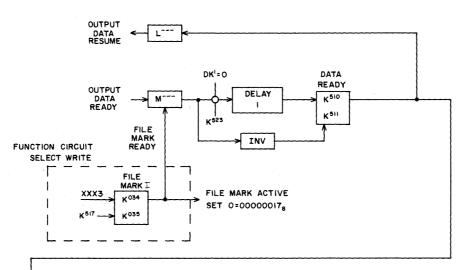

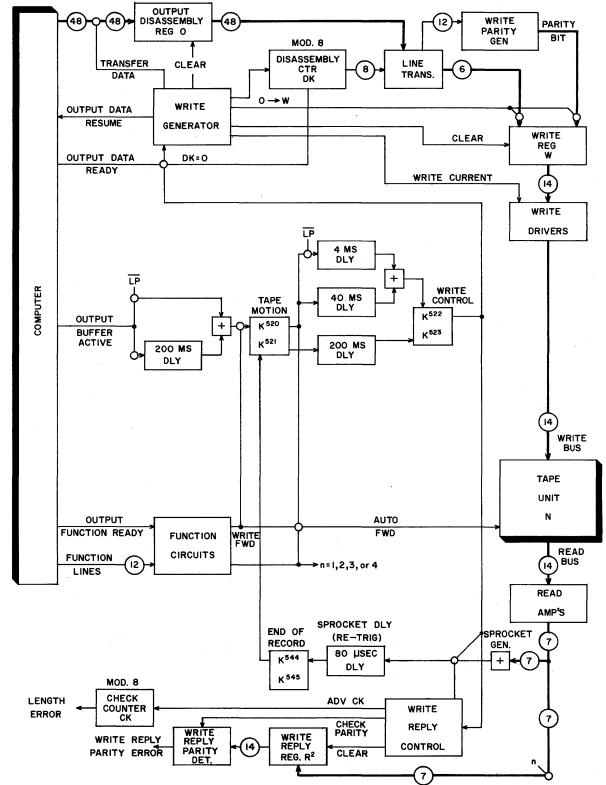

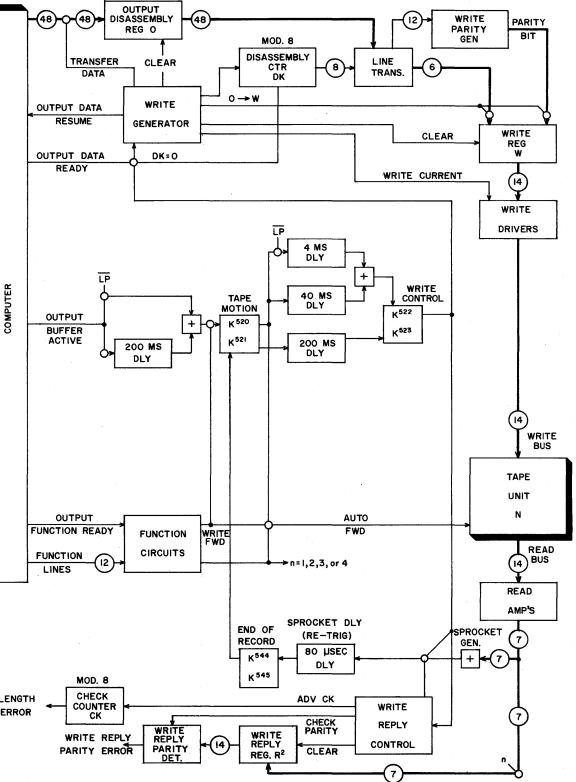

| 3-20Write Generator3-393-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-19       |                                                                | 3-37       |

| 3-21Write Reply Circuit3-413-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-20       |                                                                | 3-39       |

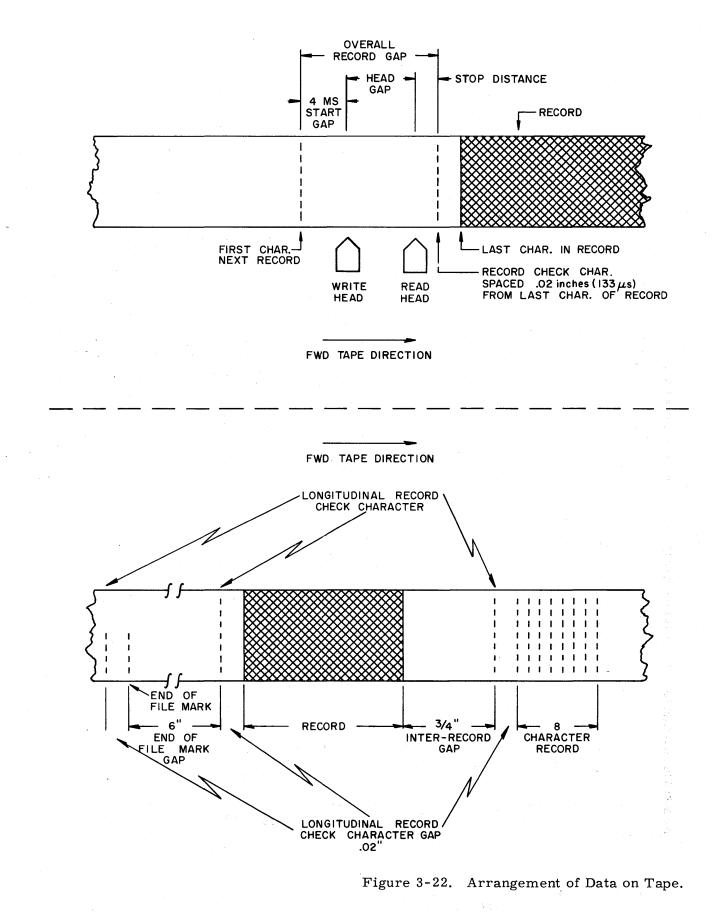

| 3-22Arrangement of Data on Tape3-433-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-21       |                                                                | 3-41       |

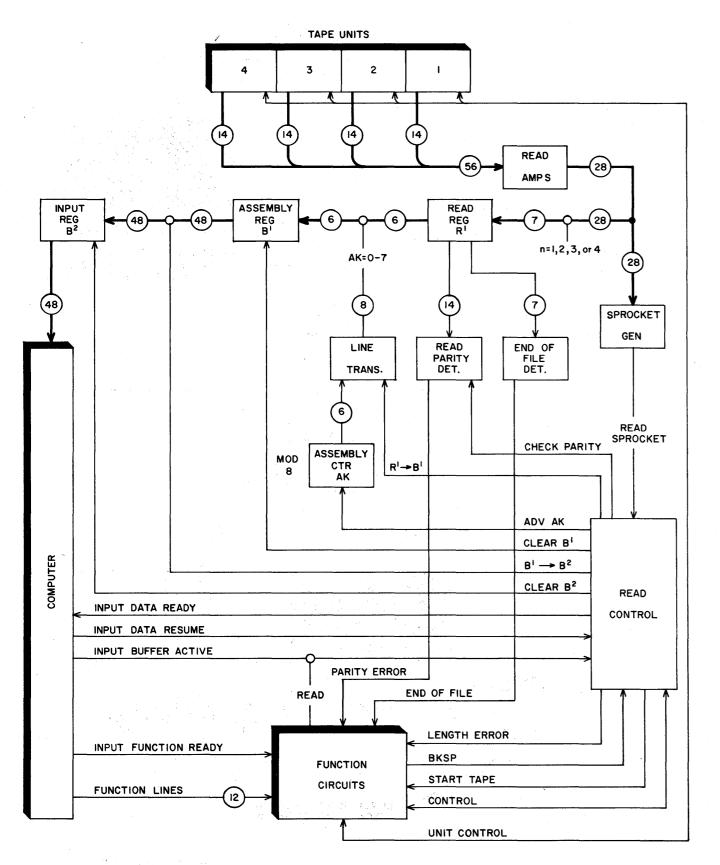

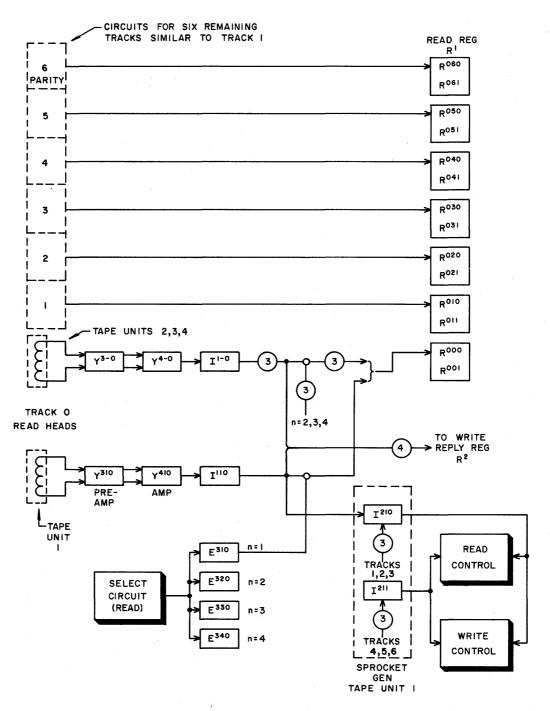

| 3-23Simplified Block Diagram, Read Circuits3-443-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                                                | 3-43       |

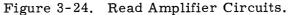

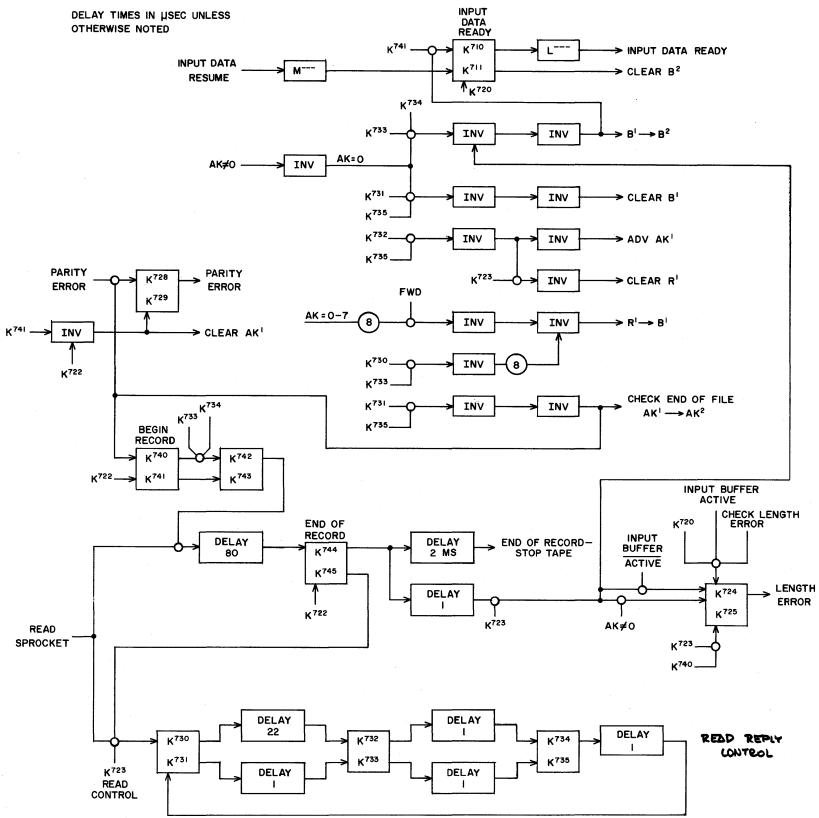

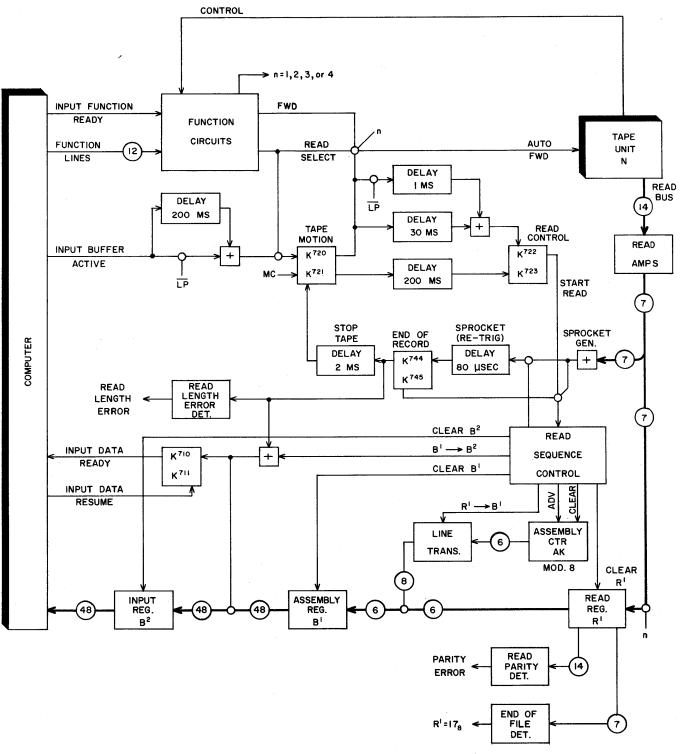

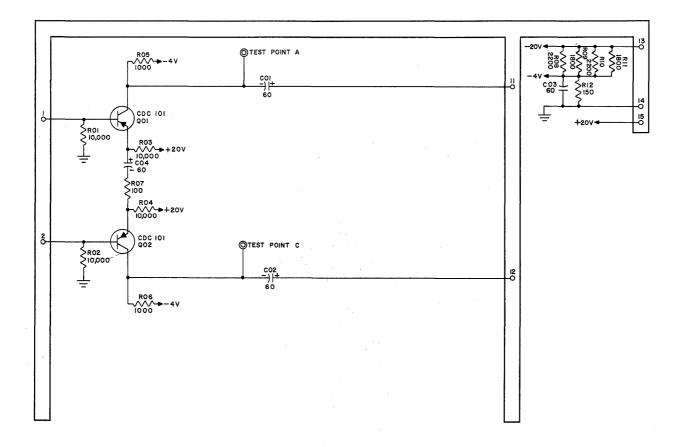

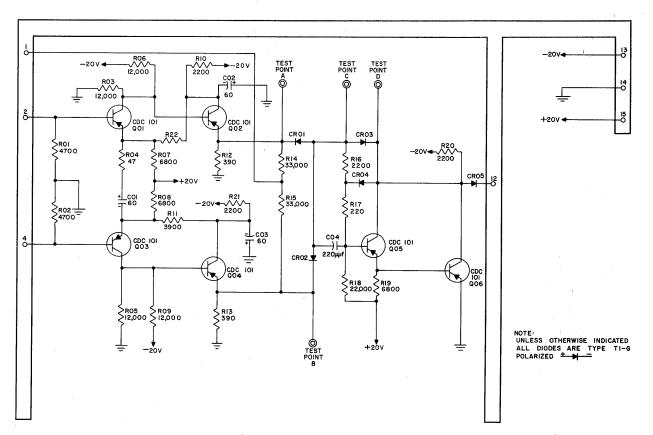

| 3-24Read Amplifier Circuits3-473-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                                |            |

| 3-25Assembly Counter and Translator3-493-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                                | 3-47       |

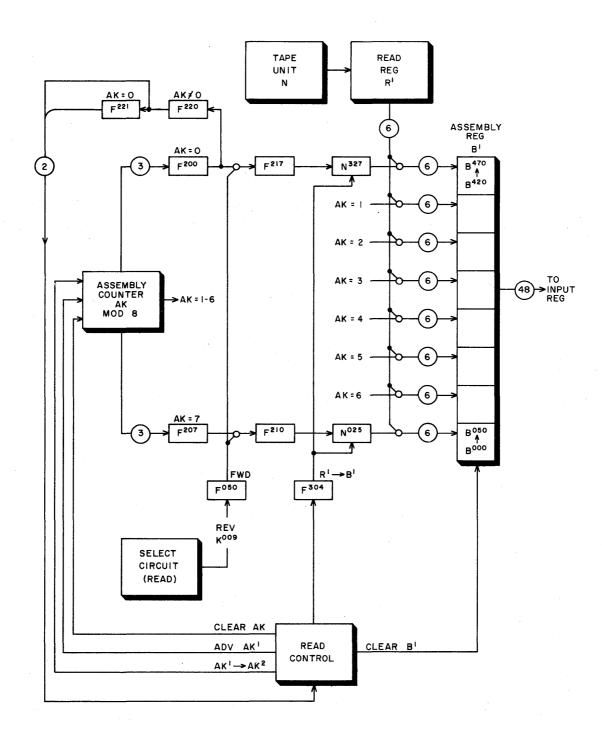

| 3-26End-of-File Detector3-513-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                                |            |

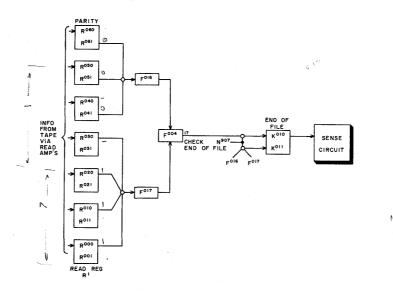

| 3-27Read Control, Tape Motion Circuit3-523-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                                |            |

| 3-28Read Control, Read Sequence Control3-553-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                                |            |

| 3-29Write Logic Diagram3-633-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                                                                |            |

| 3-30Read Logic Diagram3-713-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                                                |            |

| 3-31Unit Selection Switches3-793-32Manual Controls3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                                |            |

| 3-32 Manual Controls 3-83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                                |            |

## FIGURES

Chapter 3 - (Cont'd.)

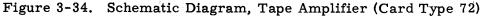

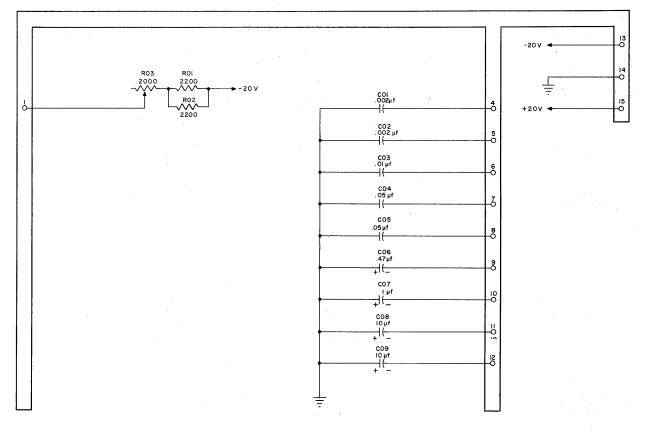

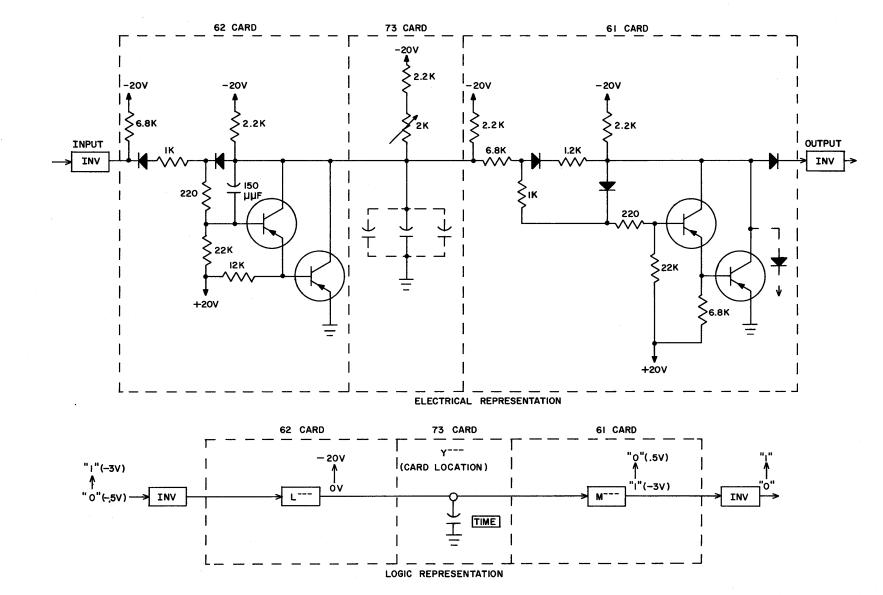

| 3-34 | Schematic Diagram, | Tape Amplifier (Card Type 72)      | 3-89 |

|------|--------------------|------------------------------------|------|

| 3-35 |                    | Delay (Card Type 73)               | 3-89 |

| 3-36 | Delay Circuit      |                                    | 3-90 |

| 3-37 | Schematic Diagram, | Tape Current Source (Card Type 74) | 3-91 |

## TABLES

| Chapter 1                       | General Description                                                                                                                                                |                                      |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5 | IBM Character Code<br>External Function Codes<br>Summary of Equipment Characteristics<br>Data and Control Line Characteristics<br>Connector Pin Number Assignments | 1-12<br>1-13<br>1-14<br>1-16<br>1-18 |

| Chapter 2                       | Operation                                                                                                                                                          |                                      |

| 2-1                             | Function of Manual Controls and Indicators                                                                                                                         | 2-8                                  |

| Chapter 3                       | Principles of Operation                                                                                                                                            |                                      |

| 3-1<br>3-2<br>3-3               | Equation Symbol Assignments<br>External Function Codes<br>Sense Operations                                                                                         | 3-7<br>3-14<br>3-77                  |

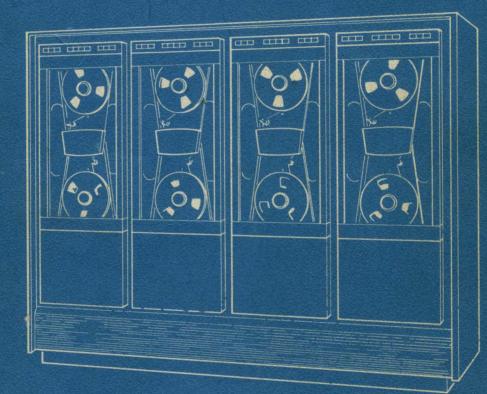

Figure 1-1. Magnetic Tape System.

#### CHAPTER 1. GENERAL DESCRIPTION

#### INTRODUCTION

The Control Data Corporation model 1607 Magnetic Tape System (MTS) (figure 1-1) is an optional input-output and auxiliary memory storage device for the Control Data Model 1604 Computer. A MTS is comprised of four Ampex FR307 digital tape handlers and a synchronizer control unit, all housed in a single cabinet. Each tape unit handles and processes plastic base tape on which data are stored as magnetized spots. The synchronizer buffers and controls the flow of data between the computer and the individual tape units. Transfer of data from the computer memory to the magnetic tapes, and vice versa, and exchange of control information is accomplished through coded programmed External Function (74) instructions.

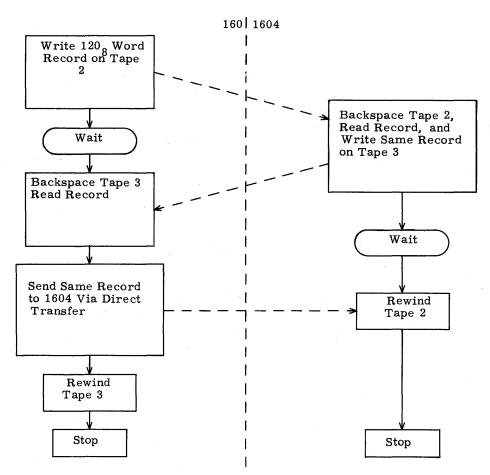

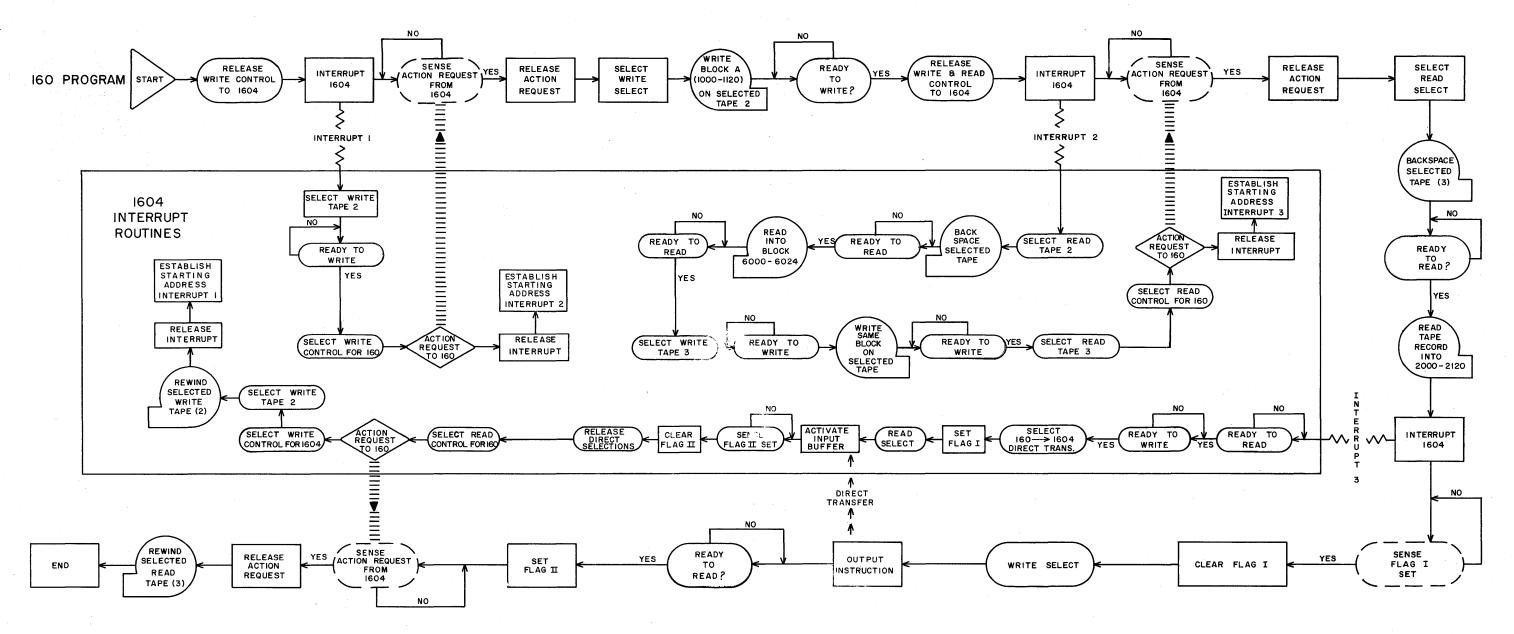

Chapter 1, 2, and 3 describe the 1607 MTS as designed for use with the 1604 Computer only. Additional design features now provide for the use of the 1607 MTS with either the 1604 Computer or the 160 Computer. These features are described in Chapter 4, "The Satellite Computer System".

Information contained in this instruction book is subject to correction and change.

## PHYSICAL DESCRIPTION

The MTS cabinet is 88 1/2 inches long, 67 3/4 inches in over-all height, and 27 1/2 inches wide. The approximate weight of the cabinet is 2500 pounds. Components within the cabinet are air cooled by blowers at the bottom of the cabinet which circulate air-conditioned room air. The equipment operates from a 208-vac, 3-phase, 400-cps supply at 5 amps and a 208-vac 3-phase 60-cps supply at 25 amps.

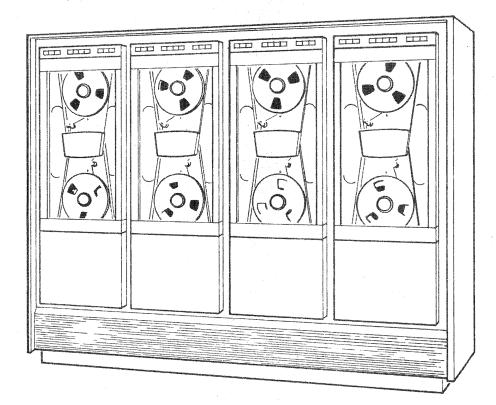

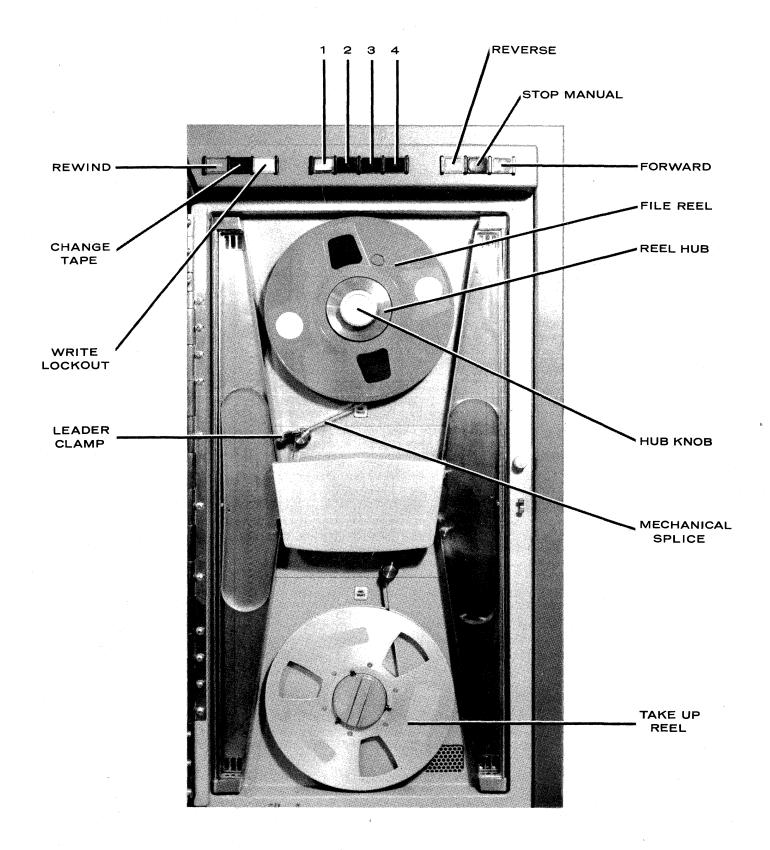

The cabinet is subdivided into four standard 19-inch relay rack sections, each of which holds the chassis associated with one tape unit (figure 1-2). The tape unit circuits use vacuum tubes and transistors in conjunction with printed circuit board wiring techniques. Each tape unit has self-contained d-c power supplies. The glass door at the front of each unit provides access to the tape handler for loading and unloading reels of tape.

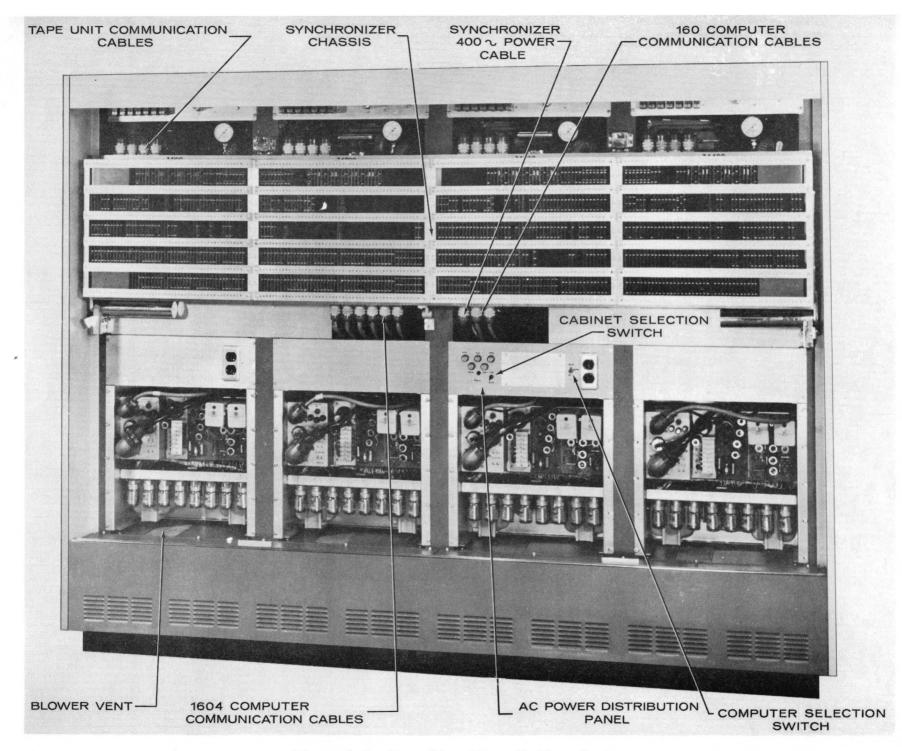

Figure 1-2. Rear View Magnetic Tape System.

1 - 2

Rev. 2/61

The switches and indicators above the front door allow the operator to monitor and manually control tape unit conditions.

The synchronizer chassis is mounted at the rear of the cabinet (figure 1-2). Springloaded hinges in the lower corners of the chassis and release catches and handles at the top allow horizontal positioning of the chassis (with the sliding doors removed) for maintenance purposes. The circuits of the synchronizer are composed of printed circuit cards identical in construction to those used in the computer. The majority of the cards contain the standard building-block circuit properly interconnected to form the logical networks necessary to communicate with the tape units and computer.

Data is transferred between the MTS and the computer via six cables which connect to the bottom of the synchronizer chassis (figure 1-2). Jumper wires from these six cable connectors to another set of six cable connectors allow other equipment to communicate with the computer on the same communication paths. Data is transferred between each tape unit and the synchronizer via separate cable groups of four cables each which connect at the top of the synchronizer chassis.

Separate cables carry 400-cps and 60-cps, 208-vac primary power to the MTS a-c power distribution panel (figure 1-2). From this panel 400-cps power is cabled to the bottom of the synchronizer chassis and distributed from this point to the d-c power supply circuits located in the four corners of the chassis. The 60-cps power is routed to the blowers and to the convenience outlet panels in each cabinet section. Power cables carry 110-vac, 60-cps power from the outlets to each tape unit.

## MAGNETIC TAPE CHARACTERISTICS

The MTS provides the computer with a high-speed non-volatile data storage system. Computer output data is recorded on the tape in a format compatible in all respects with the IBM 727 magnetic tape system. This facility enables communication with IBM 700 series computers as well as with a variety of IBM peripheral equipment.

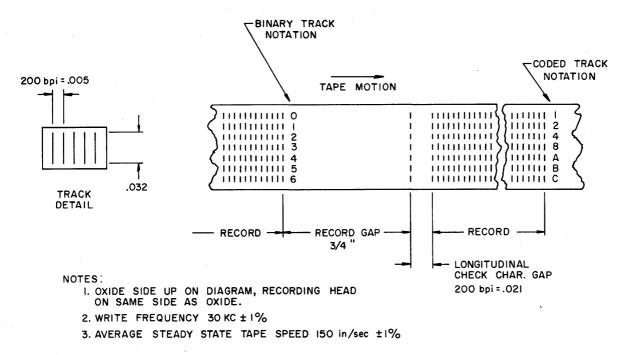

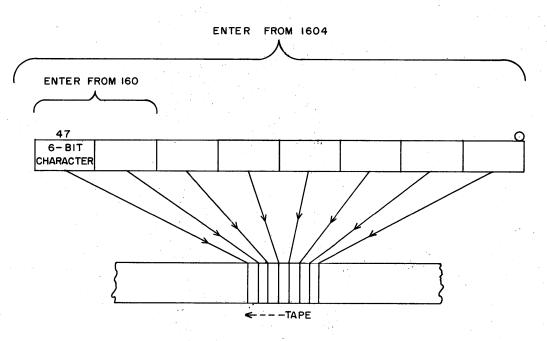

A seven track non-return to zero (change-on-ones) recording scheme is used. Six tracks are assigned to the data (termed a character) and one track contains a parity check bit for the character. A character and its parity bit comprise a line of tape data.

Data is recorded in two formats: binary and binary-coded-decimal (coded). The parity bit is chosen to make the total number of "1" bits in a line odd in binary format, even in coded format. The format is chosen by the EF instruction, and the synchronizer generates the appropriate parity bit for each character. Figure 1-3 shows the bit assignments on the tape for the two formats. Table 1-1 gives the IBM character code used when generating tapes for reproduction by IBM peripheral equipment. The parity bit is recorded in tracks 6 and C for binary and coded format, respectively; the least-significant bit position is in tracks 0 and 1, respectively.

Figure 1-3. Magnetic Tape Specifications

Data is recorded on the tape at a density of 200 lines per inch and in records of varying length. A 3/4-inch unrecorded area or blank space separates adjacent records. A number of records may be grouped into a file of information on the tape by recording of a special character (octal 17 code) spaced 6 inches from the last record in the file.

Tape speed during reading and writing operations is 150 inches per second; the character transfer rate is 30 KC. Standard tape is 1/2 inch wide and up to 3600 feet long. Small reflective spots attached to the tape mark the beginning and end of the useable portion of tape. These markers are referred to as load-point and end-of-tape and are detected by photo-sensing means.

## BASIC PRINCIPLES OF OPERATION

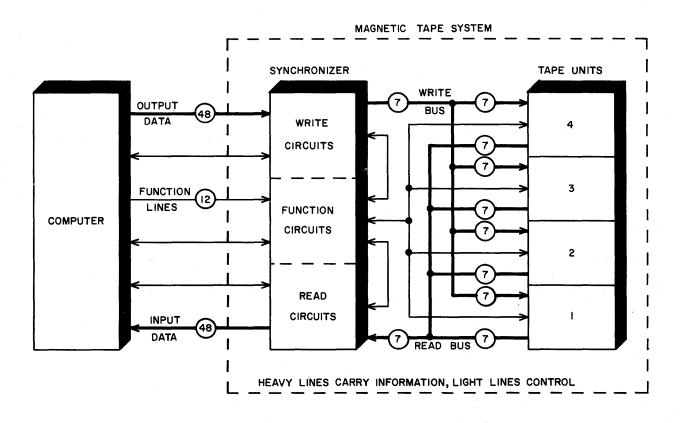

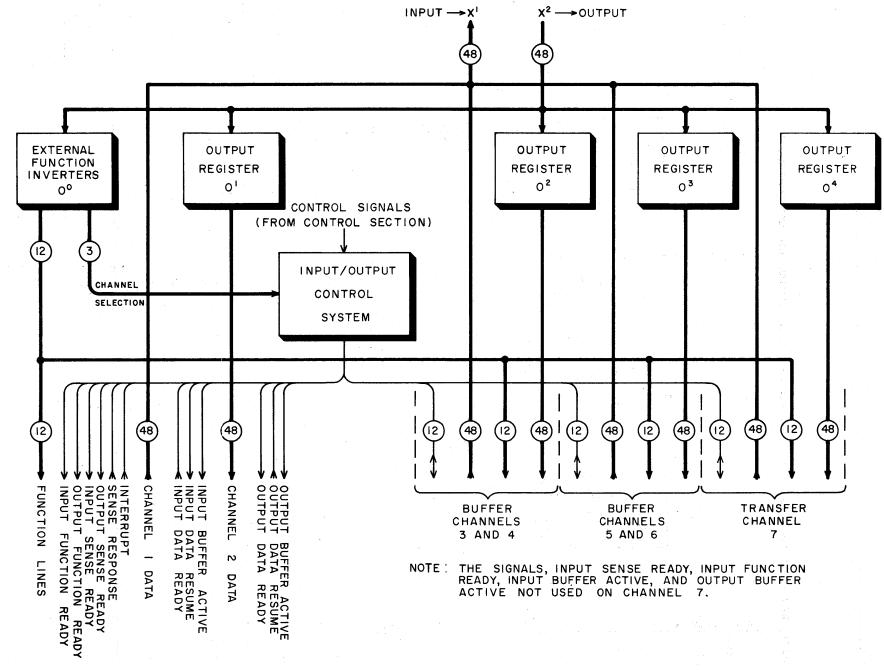

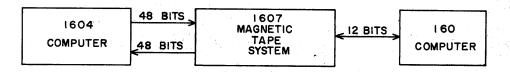

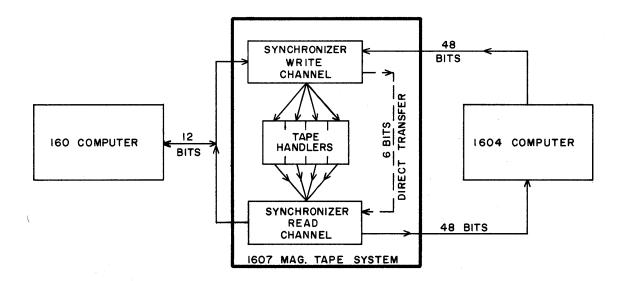

The MTS communicates through the synchronizer with the computer on a 12-bit function channel, a 48-bit input buffer channel, a 48-bit output buffer channel, and associated control signal lines (figure 1-4). The channels and control signals are activated by the External Function (EF 74) instruction.

Depending on the installation, a MTS can communicate with the computer on buffer channel pairs 1 and 2, 3 and 4, or 5 and 6 (even numbers denote computer output channels, odd numbers input channels). This instruction manual assumes a MTS connected to channels 3 and 4.

Each tape unit communicates with the synchronizer on a 7-bit read bus, a 7-bit write bus and associated control lines. The appropriate unit and its cable lines are activated in response to the EF instruction.

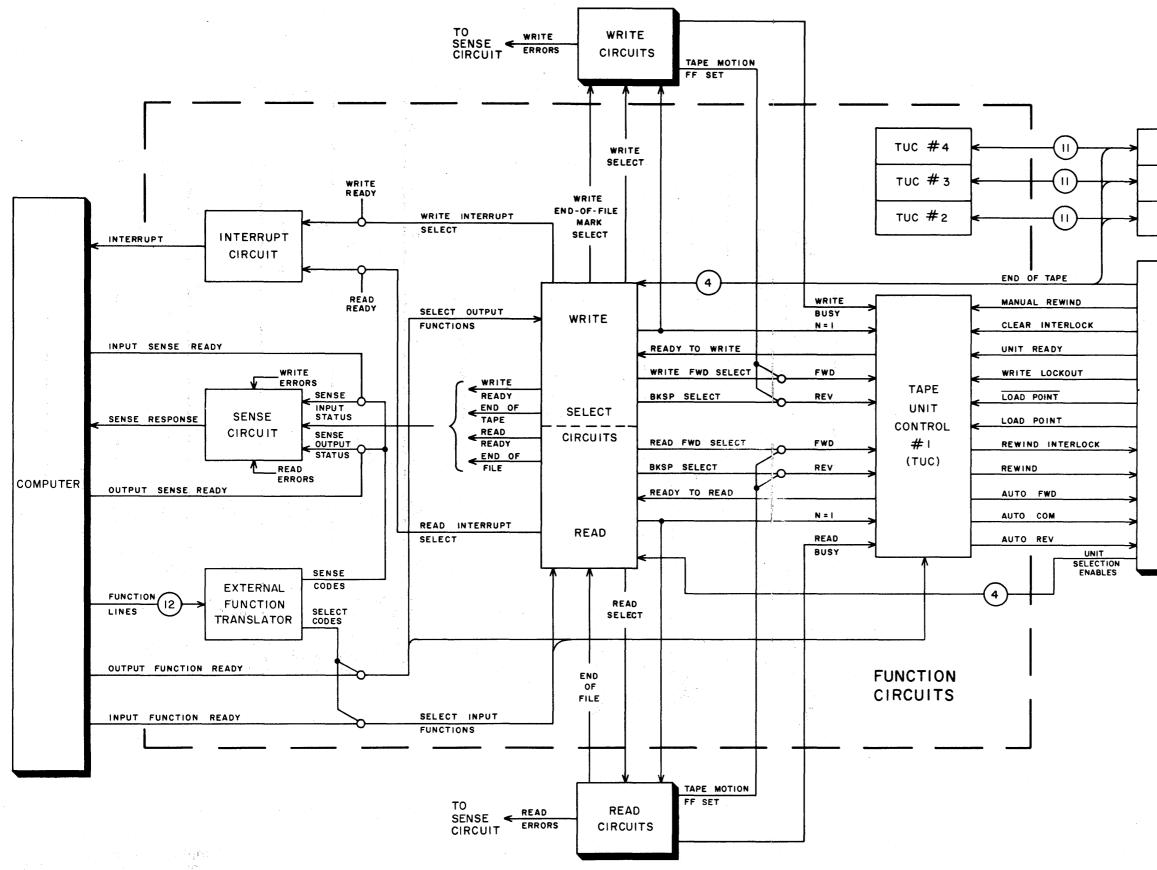

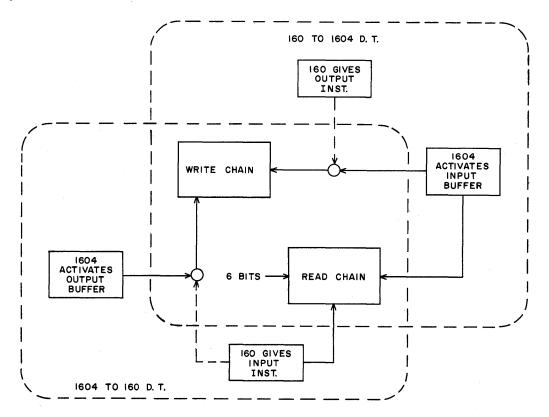

Figure 1-4. Magnetic Tape System, Information Flow.

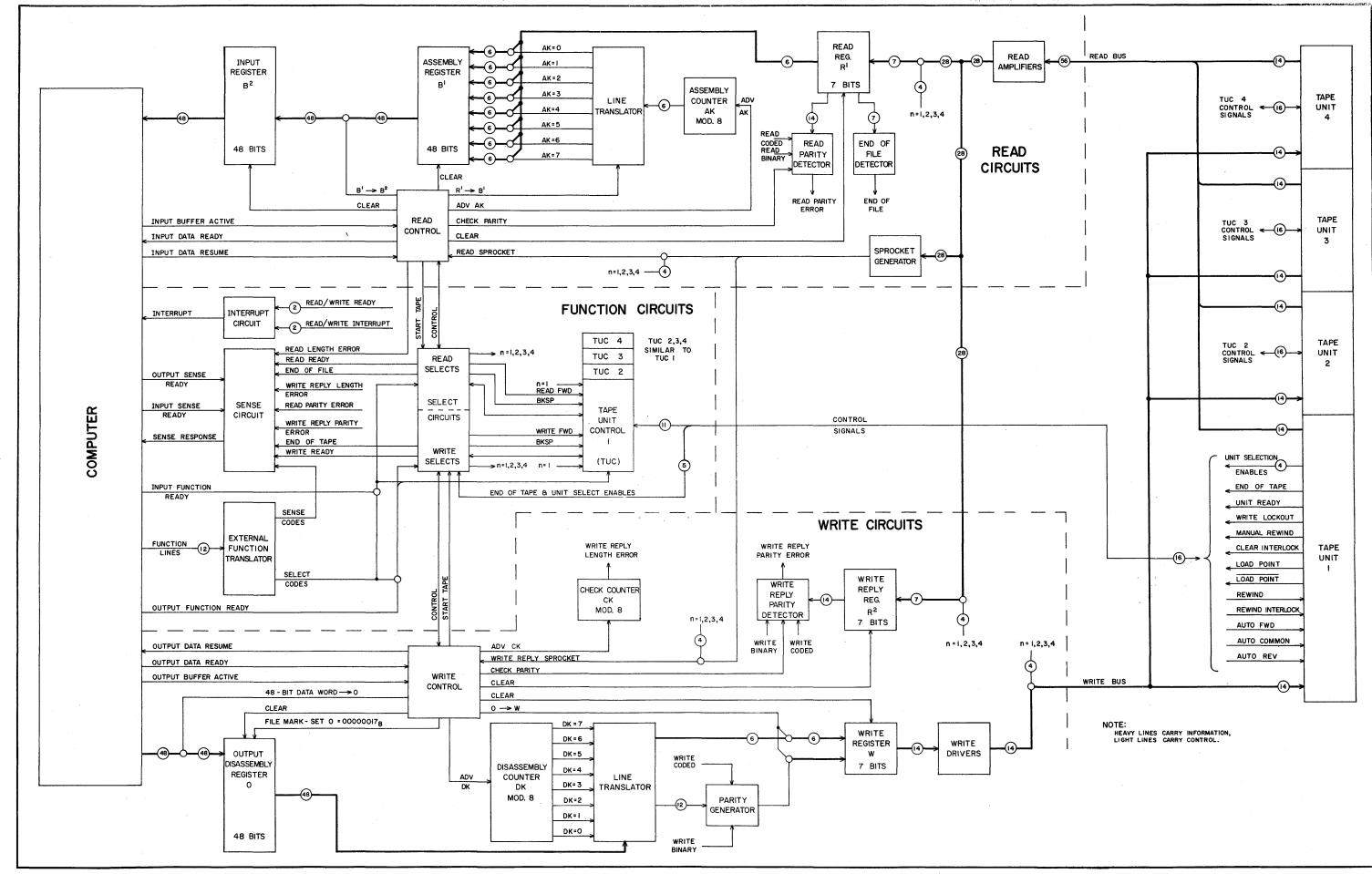

The circuits of the synchronizer portion of the MTS are organized into function, write, and read circuits. The function circuits store control information regarding the tape units that is received from the computer or the units themselves. The write and read circuits provide independent write and read channels ( to accommodate simultaneous read and write operations) and use information stored in the function circuits to direct writing and reading. The write and read circuits each have access to the four tape units; a tape unit must be assigned to operate with the read or write channel. This unit assignment and other functions are accomplished by the EF instruction.

## EXTERNAL FUNCTION INSTRUCTION

The various subinstructions of the EF instruction are used to initiate and control all MTS operations. Briefly, their function are as follows:

| (EF Select)<br>74.0X       | requests specific tape operations and assigns a tape unit to a read or write channel (X). |

|----------------------------|-------------------------------------------------------------------------------------------|

| (EF Sense)                 | enables computer to determine status or condition of particu-                             |

| 74.7X                      | lar tape unit. For example, determines if unit is ready to be                             |

|                            | operated, if error was detected in previous operation, and                                |

|                            | so forth.                                                                                 |

| (EF Output Buffer)<br>74.4 | initiates and controls buffering of 48-bit words from computer                            |

| 74.4                       | to MTS for recording on tape.                                                             |

| (EF Input Buffer)<br>74.3  | initiates and controls buffering of MTS data <u>to</u> computer.                          |

## Select Operations

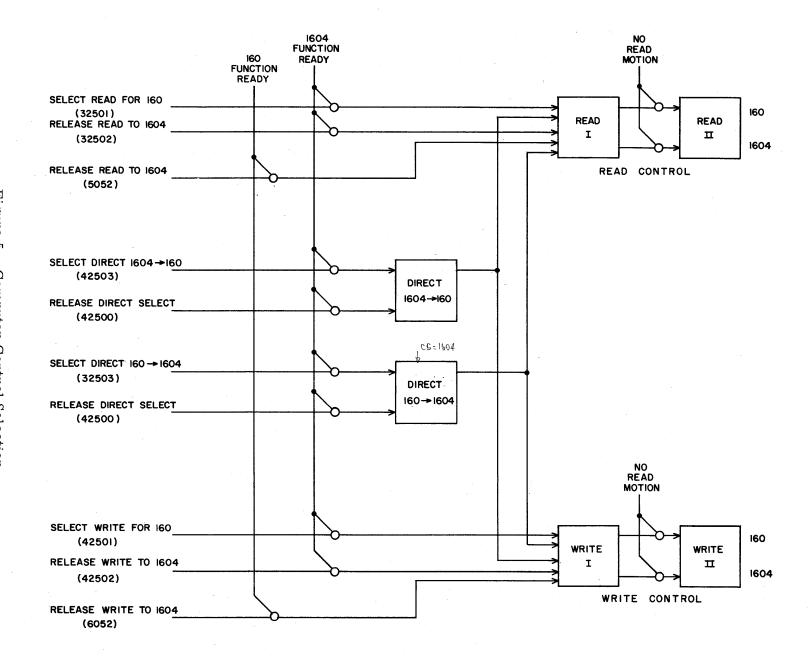

During select (74.0X----) instructions the lower-order 12 bits of the instruction are sent out on the function channel with a function ready signal to all equipment connected to channel X. The upper 3 bits of the code specify the equipment, the lower-order 9 bits the operation requested. The synchronizer function circuits interpret the EF code and store the information in control flip-flops. In general, input channel codes are stored in control FFs which communicate with the read circuits; output channel codes are stored in control FFs which communicate with the write circuits. Table 1-2 lists all MTS select codes.

As noted earlier the write and read circuits each have access to the four tape units and it is necessary to assign a unit (n=1, 2, 3, 4) to one channel or the other. In table 1-2 the first two instructions in the two select code groups assign a tape unit to a read or write channel. All other selections and sense operations (see below) in the same group are accomplished on the previously selected unit. By means of manual controls on each tape unit, any of the four tape units can be operated as the unit designated by the program.

<u>Write</u>. A write select (20n1, 2) instruction assigns unit n to the output channel specified and prepares the synchronizer for an impending output buffer operation (a 2001, 2 select instruction is used if unit was selected previously). Execution of a subsequent 74.4 output buffer instruction establishes the output buffer initial address and causes the computer to issue an output buffer active signal (buffer terminal address is generally established prior to write select).

The computer signal starts the selected tape moving and after a short delay the write circuits accept the initial 48-bit word indicated by an output data ready signal. The word is transferred to a disassembly register and an output data resume signal is returned to the computer after which the word is recorded. Each word is disassembled into 6-bit characters, a parity bit generated for each, and the 7 bits transmitted over the write bus to the tape unit for recording on the tape. One character is recorded every  $33 \ \mu$ secs.

The sequence continues with exchange of ready and resume signals until the end of the buffer is reached as indicated by turn-off of the active signal. This causes a record check character to be recorded .02 inch from the last character of the record. The check character provides for a longitudinal parity check for IBM compatibility.

During the sequence each recorded line (exclusive of the check character) is sensed by a read head (spaced .390 inch from the write head), returned to the write reply circuits for a parity check and any error condition stored for subsequent sensing by the computer. An additional check determines if the number of lines read was an integral multiple of eight; if not a write reply length error is stored for later sensing by the computer.

After the last character is read the tape is stopped with the heads positioned in the interrecord space ready to write the next record. If the end-of-tape reflective spot marker is sensed during the operation, the fact is stored for later sensing by the computer. <u>Read.</u> A read select (20n1, 2) instruction assigns unit n to the input channel specified and prepares the synchronizer for an impending input buffer operation. As in the write select case, establishment of the buffer initial address causes an input buffer active signal to be generated by the computer.

The computer signal starts the tape moving and, after a suitable delay to position the read head over the data, reading begins. The lower-order 6 bits of each line are assembled into 48-bit words in an assembly register and then transferred to an input register for transmission to the computer. An input data ready signal from the synchronizer initiates computer storage action for the assembled word. A computer input data resume signal acknowledges the word and clears the input register in preparation for the next word.

A parity check is performed on each line read (exclusive of the check character) and an error condition stored for later sensing by the computer.

A lack of tape information for a predetermined period indicates the end of the record and the tape is stopped with the read head positioned in the inter-record gap ready to read the next record.

The computer may call for more or less words than are available in a record. Under these conditions a read length error is detected and stored for later sensing by the computer. If the computer buffer is equal to or less than the tape record length the buffer active signal is terminated automatically; if the buffer length is greater than the tape record length the computer executes additional instructions to artifically terminate the buffer and turn off the active signal.

Reading of an end-of-file mark  $(17_g)$  is also stored for sensing by the computer.

<u>Write End-Of-File Mark</u>. An end-of-file mark is used to group a number of records into a file of information. An output channel select write end-of-file mark (2003) instruction causes the  $17_8$  code to be recorded on the tape 6 inches after the last record in the file. The mark is treated as a 1-character record and a longitudinal check character (also an octal 17) is also written. No computer buffer is established for this operation. Backspace. An input or output channel select backspace (2006) instruction moves the tape backwards past one record to the preceding inter-record gap. None of the information passed over is available to the computer and therefore no computer buffer is established.

<u>Rewind.</u> An input or output channel select rewind (2005) instruction rewinds the tape from its current position to the load point.

<u>Rewind Interlock</u>. An input or output channel select rewind interlock (2007) instruction rewinds the tape from its current position to the load point and provides an interlock at that point so that the tape is not again available to the computer. Tape speed is 225 inches per second in this operation.

<u>Interrupt</u>. An input or output channel interrupt select (2004) instruction may be executed after any of the select instructions (except rewind interlock) to automatically interrupt the main computer program upon completion of the previously selected tape operation. For read or write select instructions, the interrupt select is executed after the read or write operation is selected and after the buffer initial address has been established.

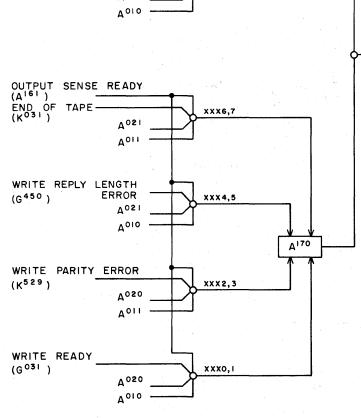

## Sense Operations

During sense (74.7X----) instructions the lower-order 12 bits of the instruction are sent out on the function channel with an appropriate sense ready signal to all equipment connected to channel X. As in select instructions the upper 3 bits specify the equipment, the lower-order 9 bits, however, request an indication of the status or condition of a tape unit (unit selected previously). If the condition being sensed is present, the synchronizer returns (immediately) a positive sense response to the computer; if the condition is not present a negative response is generated. The computer interprets the response internally. Table 1-2 lists the sense codes for determining MTS conditions. A brief description of the conditions follows.

<u>Ready to Read.</u> A tape unit must be ready to accept new input channel (or output channel; see below) select instructions. This sense instruction (2000,1) enables the computer to determine a unit's readiness. A unit is ready if:

- Unit has power on and all protective interlocks are closed (front door closed, etc).

- 2) No current input channel select operation is in process.

3) Unit is not rewound with interlock.

<u>Read Parity Error</u>. This input channel sense instruction (2002, 3) enables the computer to determine a parity error (vertical). A positive response indicates:

- 1) A previous read binary operation detected one or more lines with an even number of "1" bits.

- 2) A previous read coded operation detected one or more lines with an odd number of "1" bits.

<u>Read Length Error</u>. This input channel sense instruction (2004,5) enables the computer to determine if, in a previous read operation, the word length of the tape record was in agreement with the computer buffer length. A negative response indicates nonagreement and it is necessary for the computer to insure that its input buffer is terminated. Tape motion will be prevented if a previous input buffer was not completed and the input buffer active signal turned off.

<u>End-of-File Mark</u>. This input channel sense instruction (2006,7) enables the computer to determine if an end-of-file mark (octal 17) was read in a previous read operation.

<u>Ready to Write</u>. This output channel sense instruction (2000,1) enables the computer to determine a unit's readiness to perform an output channel select operation. Ready conditions are the same as described for the Ready to Read sense instruction.

Write Reply Parity Error. This output channel sense instruction (2002,3) enables the computer to determine if a parity error (vertical) was detected in the write reply sequence of a previous write operation. Error conditions are as described for the Read Parity Error sense instruction.

Write Reply Length Error. This output channel sense instruction (2004,5) enables the computer to determine, for a previous write operation, if the number of lines read in the write reply sequence was an integral multiple of eight.

End-of-Tape Marker. This output channel sense instruction (2006,7) enables the computer to determine when no more tape is available for writing. The end of the useable portion of the tape is indicated by a reflective marker on the tape. Enough useable tape is available between the marker and the physical end of the tape to store approximately 20,000 characters.

## TABLES CHAPTER ONE

| Character | Code<br>(Octal) | Character          | Code<br>(Octal) |

|-----------|-----------------|--------------------|-----------------|

| Α         | 61              | 2                  | 02              |

| В         | 62              | 3                  | 03              |

| С         | 63              | 4                  | 04              |

| D         | 64              | 5                  | 05              |

| Е         | 65              | 6                  | 06              |

| F         | 66              | 7                  | 07              |

| G         | 67              | 8                  | 10              |

| н         | 70              | 9                  | 11              |

| I         | 71              | &                  | 60              |

| J         | 41              | -                  | 40              |

| K .       | 42              | (blank)            | 20              |

| L         | 43              | 1                  | 21              |

| M         | 44              | . (period)         | 73              |

| N         | 45              | \$                 | 53              |

| 0         | 46              | *                  | 54              |

| Р         | 47              | , (comma)          | 33              |

| Q         | 50              | %                  | 34              |

| R         | 51              | #                  | 13              |

| S         | 22              | @                  | 14              |

| Т         | 23              | Д                  | 74              |

| U         | 24              | 0 (numerical zero) | 12              |

| v         | 25              | record mark        | 32              |

| W         | 26              | 0 (minus zero)     | 52              |

| x         | 27              | 0 (plus zero)      | 72              |

| Y         | 30              | group mark         | 77              |

| Z         | 31              | tape mark          | 17              |

| 0         | 00              |                    |                 |

| 1         | 01              |                    |                 |

TABLE 1-1. IBM CHARACTER CODE

## TABLE 1-2. EXTERNAL FUNCTION CODES

| Channel        |                                                        | Select Codes                                                                                                                                                                                                                         |

|----------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Channel  | 20n1<br>20n2                                           | Select read tape n, binary<br>Select read tape n, coded                                                                                                                                                                              |

| 74.03          | 2001<br>2002<br>2004<br>2005<br>2006<br>2007           | Read selected tape, binary<br>Read selected tape, coded<br>Interrupt when selected tape ready<br>Rewind selected tape<br>Backspace selected tape<br>Rewind selected tape with interlock                                              |

| Output Channel | 20n1<br>20n2                                           | Select write tape n, binary<br>Select write tape n, coded                                                                                                                                                                            |

| 74.04          | $2001 \\ 2002 \\ 2003 \\ 2004 \\ 2005 \\ 2006 \\ 2007$ | Write selected tape, binary<br>Write selected tape, coded<br>Write end-of-file mark on selected tape<br>Interrupt when selected tape ready<br>Rewind selected tape<br>Backspace selected tape<br>Rewind selected tape with interlock |