# Field Engineering Maintenance Manual

System/360 Model 40 2040 Processing Unit

# **Preface**

This manual contains information for servicing the IBM 2040 Processing Unit.

The section on Diagnostic Techniques gives general information concerning the maintenance concepts for System/360, and also procedures and guides for trouble-shooting. A useful description of the Diagnose instruction is given in this section. The Maintenance Features section contains a description of console displays, information on use of the console, detailed explanation for internal diagnostics, and log-out charts (with an example of a SEREP print-out). Preventive Maintenance describes and tabulates preventive maintenance action and frequency. There is a section on Checks, Adjustments, and Removals (which includes both the High Frequency and Mid-Pac power supplies). The section on Locations uses charts, diagrams, and pictures to give quick, visual reference to CPU locations.

We recommend placing this manual in a binder with the staples removed. The first page of major sections, and charts or examples could be tabbed for quick reference. Information in this manual supplements that in the following publications:

System/360 Model 40, 2040 Processing Unit Diagrams Manual, Order No. SY22-2842

System/360 Model 40 Comprehensive Introduction, FETOM, Order No. SY22-2840

System/360 Model 40 Functional Units, FEMI, Order No. SY22-2843

System/360 Model 40 Theory of Operation, FEMI, Order No. SY22-2844

System/360 Model 40 Power Supplies and Appendices, FEMI, Order No. S223-2845

#### SLT manuals:

Solid Logic Technology, Packaging, Tools, and Wiring Change, FETOM, Order No. SY22-2800

Solid Logic Technology, Power Supplies, FETOM, Order No. SY22-2799

This manual is written to engineering change level 254814 for ALD's and CLD level 255263. Subsequent engineering changes may alter the contents of this manual.

All three-digit figure references are to System/360 Model 40, 2040 Processing Unit, Field Engineering Diagrams Manual, Order No. SY22-2842.

Fifth Edition (November 1975)

This is a reprint of SY22-2841-2 incorporating changes released in FE supplement SY22-6826, dated June 1, 1970.

Changes are periodically made to the specifications herein; any such change will be reported in subsequent revisions or Technical Newsletters.

This manual has been prepared by the IBM System Products Division, Product Publications, Dept. B96, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address. Comments become the property of IBM.

| Diagnostic Techniques                                                | 7   | Mpx Data Service                                 |           |

|----------------------------------------------------------------------|-----|--------------------------------------------------|-----------|

| Maintenance Concepts                                                 | 7   | Mpx Status In                                    | <b>26</b> |

| Fault Location                                                       | 7   | I/O Interrupt Caused by Channel End, Device End, |           |

| Deferred Maintenance                                                 | 7   | Stacked in CPU (UCW)                             | 26        |

| Maintenance Compatibility Among System/360 Models                    | 7   | 1401/1460 Compatibility Feature                  |           |

| Fault Location Philosophy                                            | 7   | 1401/1440/1460 DOS Compatibility Feature         |           |

|                                                                      | •   | 1410/7010 Compatibility Feature                  |           |

|                                                                      |     | Main Storage Address Check (MS ADR)              |           |

| Documentation                                                        | 7   | ROS Address Bus Parity Check (ROS ADR)           |           |

| Maintenance Diagram Manual                                           | 7   | ROS Data Parity Check (ROS DATA)                 |           |

| Other Support Documentation                                          | 8   | Selector Channel Data Check                      |           |

| Diagnostic Monitors                                                  | 9   | Diagnostic Programs                              |           |

| Diagnostic Sections                                                  | 10  | Aids in Programming                              |           |

| System Failure Detection                                             |     | Exclusive OR Instruction for SIO Routine         |           |

| Error Detection by Logic Circuit                                     | 10  | Supervisory Call (Monitor Call) Instruction      |           |

| Error Detection by Microprogram                                      | 10  | Looping of Small Routines                        | 27        |

| Error Detection by Internal Diagnostics                              | 11  | Ensurable of Description Aids                    | 21        |

| Error Detection by External Diagnostics                              | 11  | Examples of Programming Aids                     |           |

|                                                                      |     | General Diagnostic Hints                         |           |

| System Handling of Errors                                            | 11  | Device End                                       | 29        |

| Error Stat                                                           | 11  | IBM 1442 Card Reader-Punch                       |           |

| Error Resetting                                                      |     | Instruction Counter Display                      | 30        |

| Other Error Conditions                                               |     | Interrupt Buffer                                 |           |

| Diagnose Instruction                                                 |     | Power On-Off                                     |           |

| Utilization                                                          |     | Single-Cycling                                   |           |

| Operating Instructions                                               | 14  | Small I/O Loops-Instruction Stepping             | 30        |

| Start any ROS Address                                                |     | System Reset                                     | <b>30</b> |

| Undump and Process                                                   | 16  | Miscellaneous Hints                              |           |

| Undump and Execute                                                   | 16  | Log Out Retrieval Programs                       |           |

| Transfer LS to LS, Compressing                                       | 16  | System Environment Recording (SER)               | 31        |

| Transfer LS to LS, Expanding                                         | 16  | Environment Record Edit and Print (EREP)         |           |

| Clear a Local Storage Location                                       | 16  | System Environment Record Edit and Print (SEREP  | ) 31      |

| Transfer a Data Halfword from Local Storage to                       |     | •                                                | •         |

| Multiplex Storage                                                    | 16  | Maintenance Features                             | 32        |

| Transfer a Data Halfword from Multiplex Storage                      |     |                                                  |           |

| to Local Storage                                                     | 16  | Console Regal A                                  |           |

| Cycle a Multiplex Storage Word under Worst Case                      |     | Console Panel A                                  | 32        |

| Noise Conditions                                                     | 17  | Check Indicators                                 |           |

| Cycle a Storage Protect Local Storage Word Under                     |     | Machine Condition Indicators                     |           |

| Worst Case Noise Conditions                                          | 17  | Console Panel B                                  |           |

| Read Only Storage (ROS)                                              |     | Emergency Pull                                   |           |

| ROS Display                                                          | 17  | Console Panel C                                  |           |

| ROS Diagnostic Aids                                                  |     | Diagnostic Control Switch                        |           |

|                                                                      | 18  | Channel Test Switch                              |           |

| Determining Next ROS Address                                         | 10  | Channel Select Switch                            |           |

| Machine Stops on ROBAR address (Junction Point                       | 10  | LSA Bus Display and Store Switch                 |           |

| of Several Microprogram Routines)                                    | 18  | Manual Interface — Mask and Test Tag Keys        |           |

| Stopping on PSA or ISA Condition                                     |     | Miscellaneous Toggle Switches                    |           |

| ROS Data Checks                                                      |     | Console Panel D                                  | 41        |

| Main Storage                                                         | 21  | Conditions Indicators                            | 41        |

| Clearing Main Storage to Zeros                                       | 21  | YA Stats                                         | 41        |

| Determining Incorrect Parity Words in Main Storage                   | 21  | YB Stats                                         | 41        |

| Main Storage External Worst Case Diagnostics                         | 21  | YD Stats                                         | 42        |

| Results of Main Storage Parity Error                                 | 21  | YE Stats                                         |           |

| Local Storage                                                        | 21  | ALU Control Indicators                           | 42        |

| Channel Diagnostic Techniques                                        |     | Skew Select Register Indicators                  |           |

| Abbreviations for Channel                                            |     | ALU Binary Output Indicators                     |           |

| Multiplex Channel Errors                                             |     | LSAR – H – J Indicators                          |           |

|                                                                      |     | ROBAR – ROSAB – ROAR – ROSCAR Indicators         |           |

| Selector Channel Errors Channel Control Chack Multipley and Selector | 44  | Store Toggle Switch (Stats/LSA)                  |           |

| Channel Control Check, Multiplex and Selector                        | 0.4 |                                                  |           |

| Channels                                                             |     | ROBAR Display Switch                             |           |

| Interface Control Check                                              |     | Channel Display Switch                           |           |

| Faults Detected by Microprogram                                      |     | Roller Toggle Switch                             |           |

| I/O Program Checks                                                   |     | Store/Display Roller Switch                      |           |

| Common Interface Responses                                           | 25  | Roll Chart — Upper                               | 46        |

| Initial Sel with No Interrupts Stacked (Multiplex or                 |     | Display Roller Switch                            |           |

| Selector Channel)                                                    | 26  | Roll Chart — Lower                               | <b>49</b> |

| Console Panel F                                        | 50         | Voltage Adjustment                                |     |  |

|--------------------------------------------------------|------------|---------------------------------------------------|-----|--|

| Address Keys                                           |            | Local Storage Delay Line Tap                      |     |  |

| Data Keys                                              |            | Array Changing                                    |     |  |

| Instruction Counter and Storage Address Indicators     | 50         | Diode Changing                                    |     |  |

| Storage Data Indicators                                |            | Storage Protect                                   |     |  |

| Console Panel G                                        |            | Marginal Check                                    |     |  |

| Pushbuttons and Switches for Generating MSS1, MSS2     |            | Operating Point Voltage Adjustment                |     |  |

| Stop Pushbutton                                        |            | Array Changing                                    |     |  |

| Start Pushbutton                                       |            | Diode Changing                                    |     |  |

| Check Reset Pushbutton                                 |            | Main Storage                                      |     |  |

| Store Pushbutton                                       |            | Marginal Check                                    |     |  |

| Display Pushbutton                                     |            | Operating Point Voltage Adjustment ("Shmoo" Graph |     |  |

| Log Out Pushbutton                                     |            | Strobe Checking                                   |     |  |

| CE Lock                                                |            | Delay Line Tap Changing                           |     |  |

| System Reset Pushbutton                                |            | Service Hints                                     |     |  |

| PSW Restart Pushbutton                                 |            | Array Changing                                    |     |  |

| Storage Select Rotary Switch                           |            | Main Frame                                        |     |  |

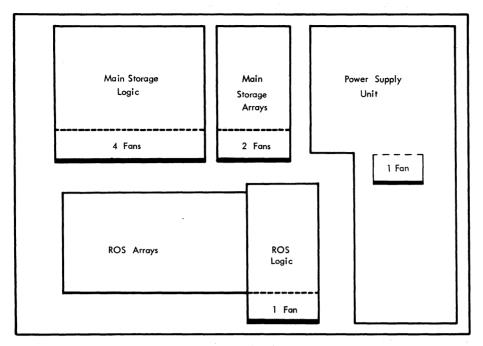

| Address Compare Switch                                 |            | Fan Changing                                      |     |  |

| Rate Switch                                            |            | Logic                                             |     |  |

| Check Control Switch                                   |            | Board Changing                                    |     |  |

| Console Panel H                                        |            | Board Pin Changing                                |     |  |

| Power-On Pushbutton                                    |            | SLT Card Changing (Card Puller P/N 452542)        |     |  |

| Power-Off Pushbutton                                   | 72         | Tape Cable Changing                               |     |  |

| Load Unit Switches                                     |            | Power Cable Changing                              |     |  |

| Interrupt Pushbutton                                   |            | Wire Wrap Changing                                |     |  |

| Load Pushbutton                                        |            | Console                                           |     |  |

| System Status Indicators                               |            | Internal Panel Meter Changing                     |     |  |

| Console Operations (Storing and Displaying Procedures) |            | Customer/CE Usage Meter                           |     |  |

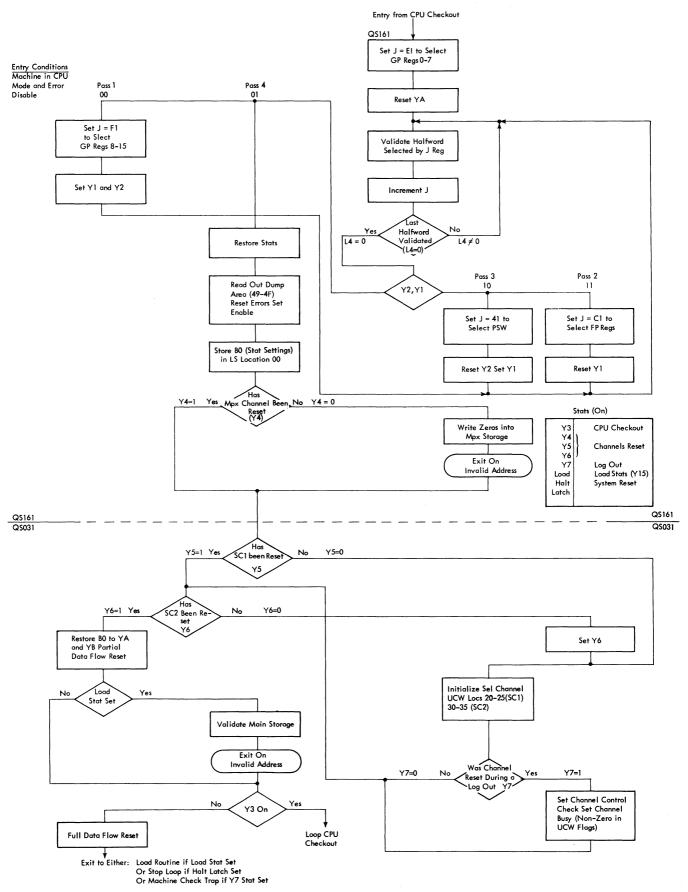

| Checkout Programs                                      |            | Lamp Changing                                     |     |  |

| CPU and Selector Channel                               | <b>7</b> 3 | Silicon Controlled Rectifier (SCR) Changing       |     |  |

| Local Storage Pattern Diagnostic                       |            | Switch Removal Procedures                         |     |  |

| Local Storage Address Diagnostic                       | 79         | CPU Timing Clock                                  |     |  |

| Main Storage Pattern Diagnostic                        | 82         | Dual/Multi-System Emergency Power Off (EPO)       |     |  |

| Main Storage Address Diagnostic                        |            | Dual System CPU Isolation                         | 126 |  |

| MS Validate                                            |            | Multi-System CPU Isolation                        |     |  |

| DUMP/UNDUMP                                            |            | Hold-Out Singleshot                               | 126 |  |

| Log Out                                                |            | Power Supplies                                    | 126 |  |

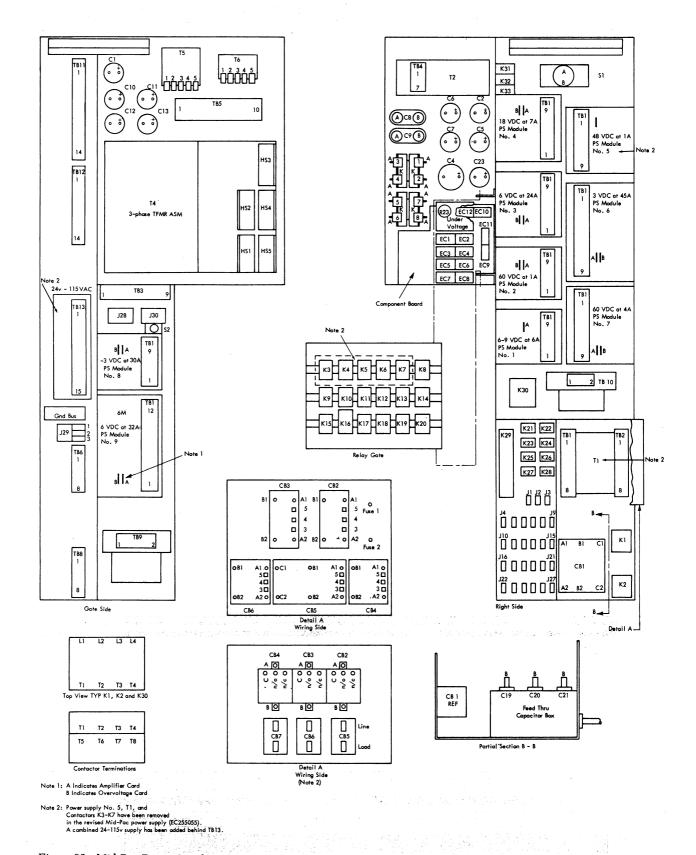

| Cause of Log Out                                       |            | Checks                                            |     |  |

| Log Out Validity                                       | 87         | Mid-Pac Power Supply Adjustments                  |     |  |

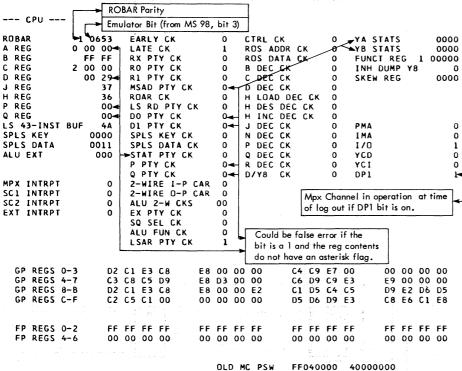

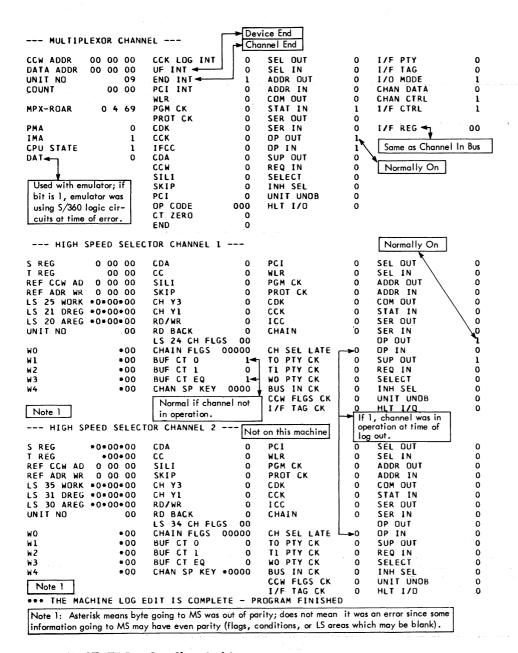

| Formatting and Editing                                 | 90         | Wall Frame Mid-Pac Power Supply Adjustments       |     |  |

| Systems Environment Recording, Editing, and Printing   | 64         | HF Power Supply Adjustments                       | 129 |  |

| (SEREP)                                                |            | Removals and Replacement                          | 134 |  |

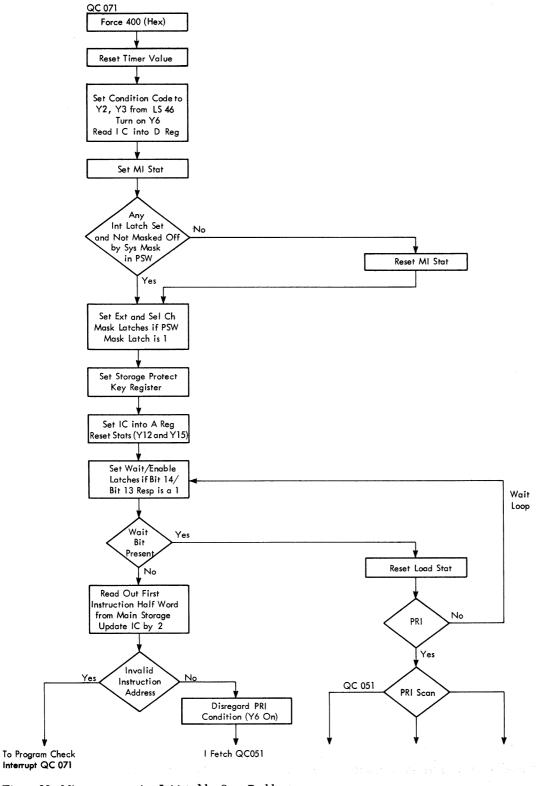

| Initial Program Load                                   | 96         | Fault Finding                                     | 136 |  |

| Possible Causes of Microprogram Hang-up for Errors     | 00         |                                                   |     |  |

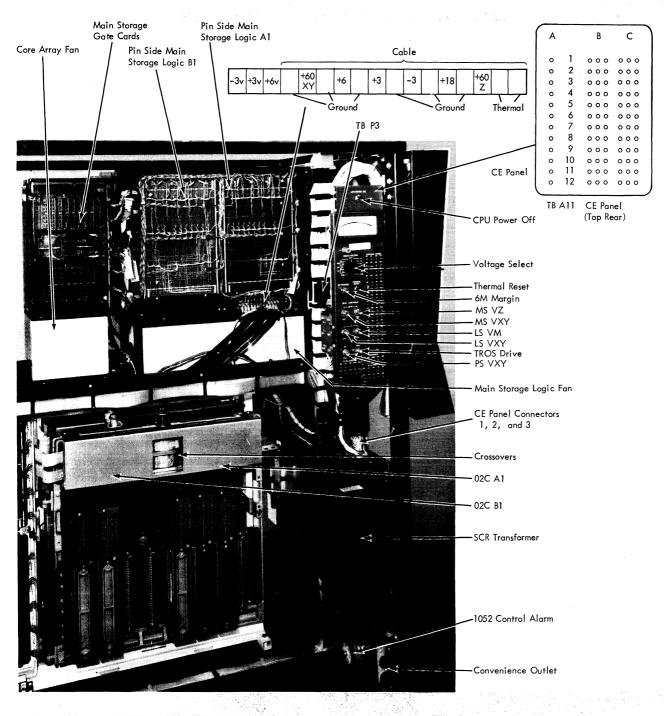

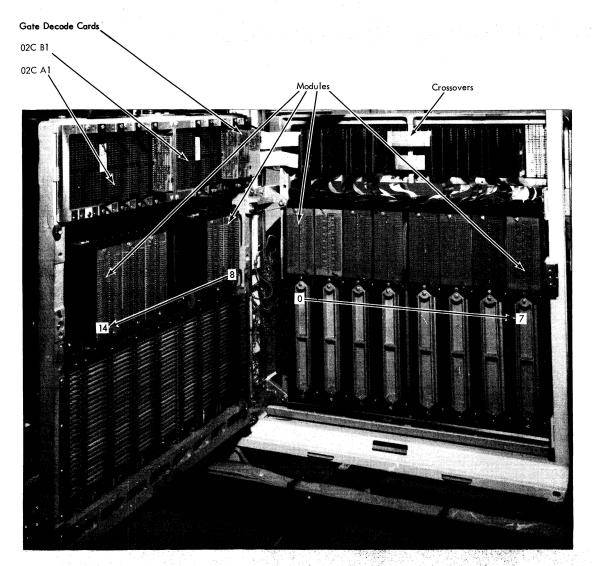

| Occurring During IPL                                   | 98         | Locations                                         | 137 |  |

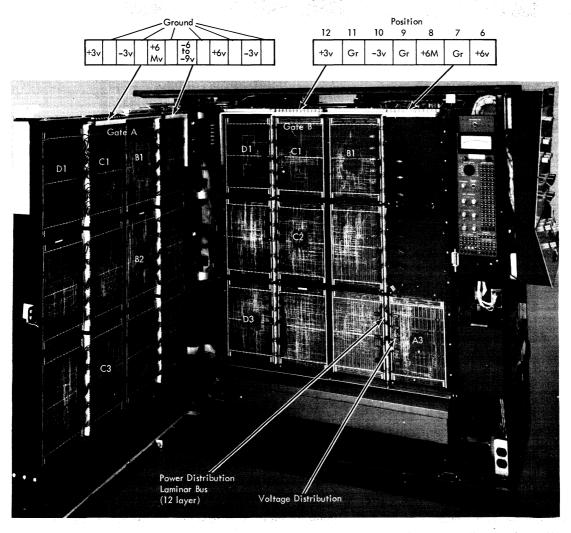

| IPL Machine Status Chart for Multiplex Channel         | 98         | Main Frame                                        | 137 |  |

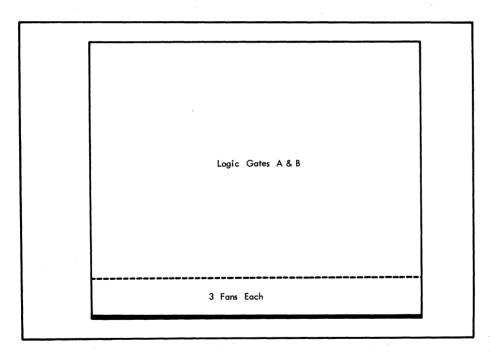

| 1401/1460 Compatibility Feature                        | 101        | CPU Logic Gates                                   |     |  |

| Console Facilities                                     | 101        | Connectors                                        |     |  |

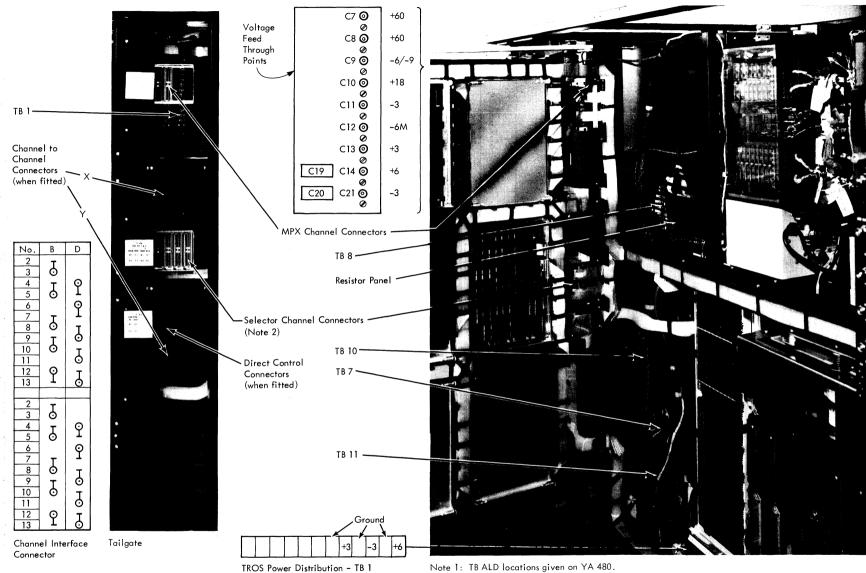

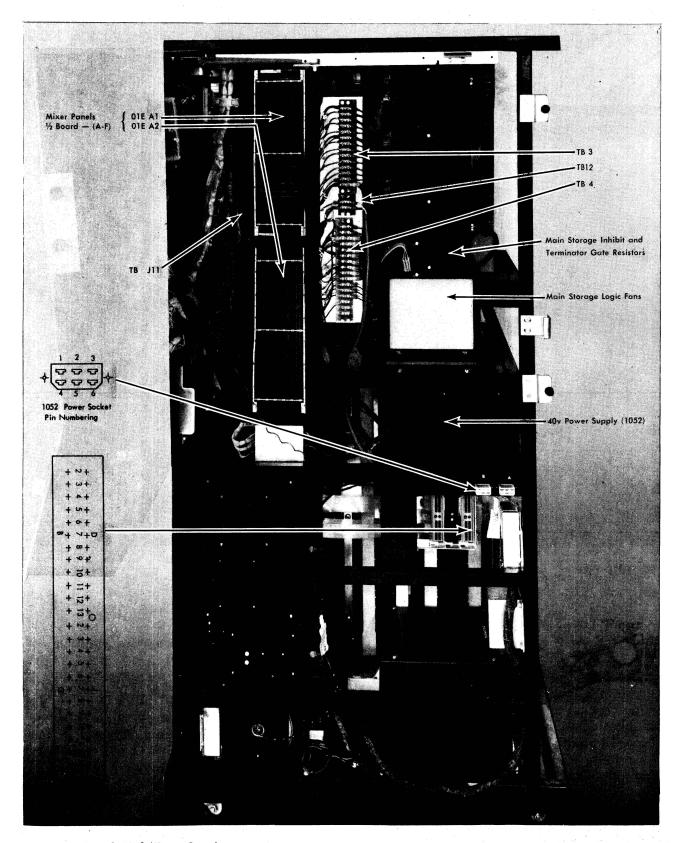

| 1410/7010 Compatibility Feature                        |            | Tailgate Connectors                               | 141 |  |

| Console Facilities                                     | 101        | Mixer Panel Connections                           |     |  |

|                                                        |            | IBM 1052 Connections                              | 141 |  |

| Preventive Maintenance                                 | 102        | CE Panel Connectors                               |     |  |

|                                                        |            | Console                                           | 150 |  |

| Charles Adiustmants and Danie                          | 100        | System Control Panel                              | 150 |  |

| Checks, Adjustments, and Removals                      | 103        | CE Panel                                          |     |  |

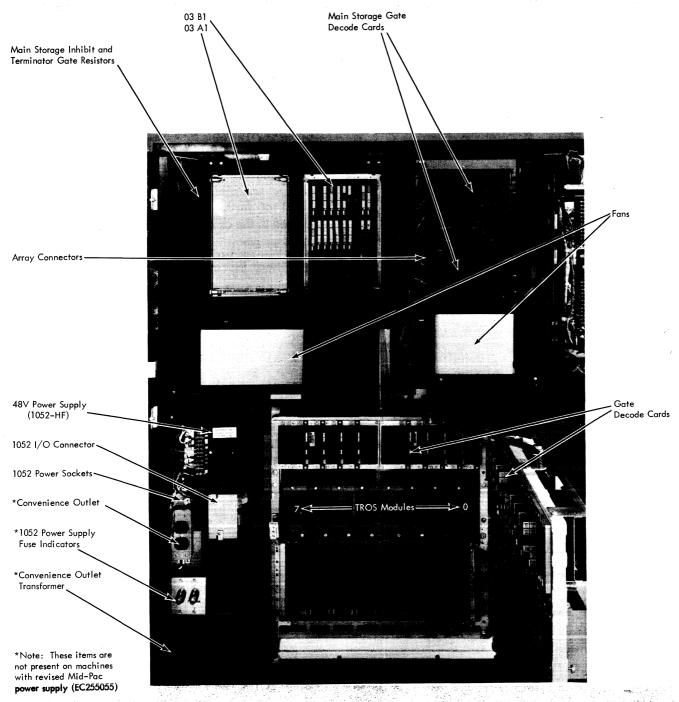

| Check Points for Voltage and Timing                    |            | TROS                                              |     |  |

| rros                                                   |            | Main Storage                                      |     |  |

| Current Adjustment                                     |            | Local Storage                                     |     |  |

| TROS Timing                                            |            | Storage Protect                                   |     |  |

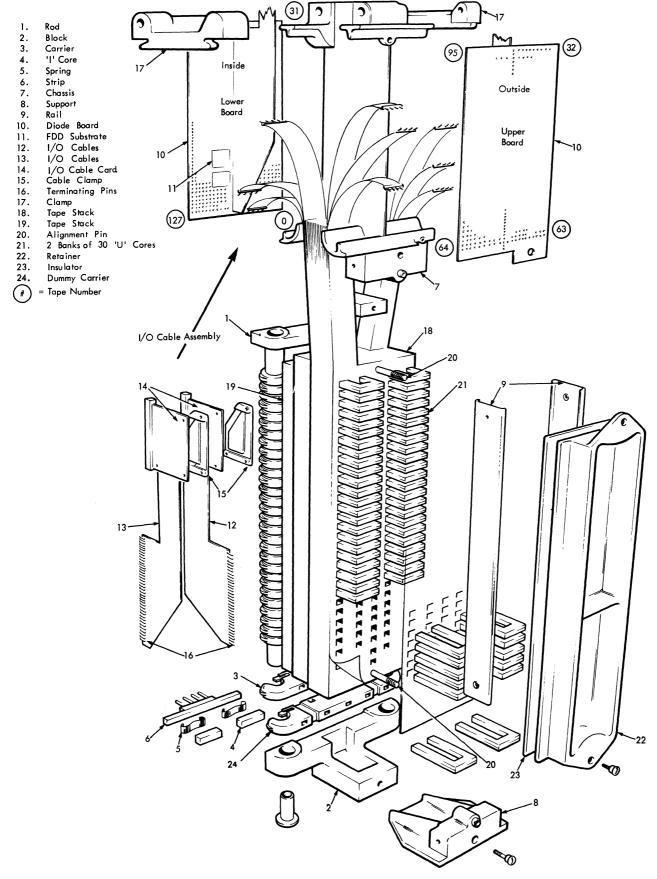

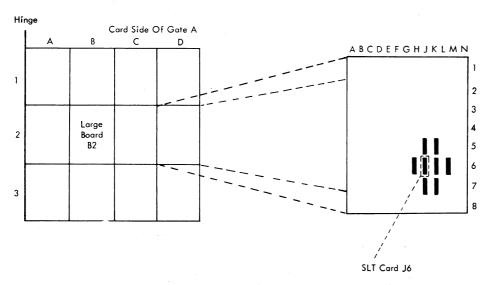

| Tape Deck Assembly Changing                            |            | Boards and SLT Cards                              | 150 |  |

| Sense Winding and I Core Assembly Changing             |            | Fuses                                             |     |  |

| Tape Changing                                          |            | Miscellaneous Components                          |     |  |

| Diode Changing                                         |            |                                                   |     |  |

| Locating an Open Diode or Open Tape                    |            | 1. Jan                                            | 150 |  |

| Local Storage                                          | 108        | Index                                             | 153 |  |

# Illustrations

| FIGURE   | TITLE                                          | PAGE       | FIGURE       | TITLE                                        | PAGE  |

|----------|------------------------------------------------|------------|--------------|----------------------------------------------|-------|

| Diagno   | stic Techniques                                |            | 51           | Formatted Log Out                            | 96    |

| 1        | System Handling of Errors                      | 12         | 52           | SEREP Log Out (2 Sheets)                     | 96    |

| 2        | Console Entry for Diagnose Instruction         | 13         | <b>-</b> 1 1 |                                              |       |

| 3        | Determine Next ROS Address                     | 19         |              | Adjustments, and Removals                    | 104   |

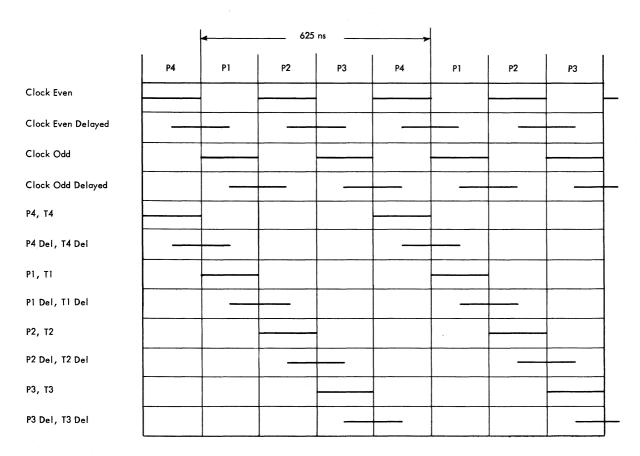

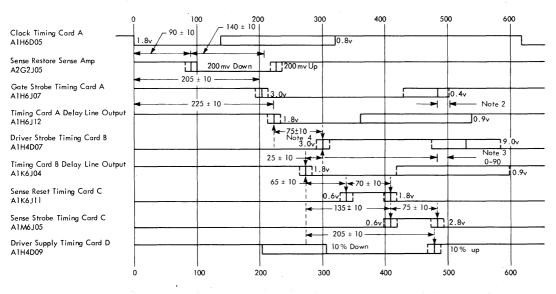

| 3.1      | Microinstruction Status on Hardstop            | 19         | 53           | Clock Timing                                 | 104   |

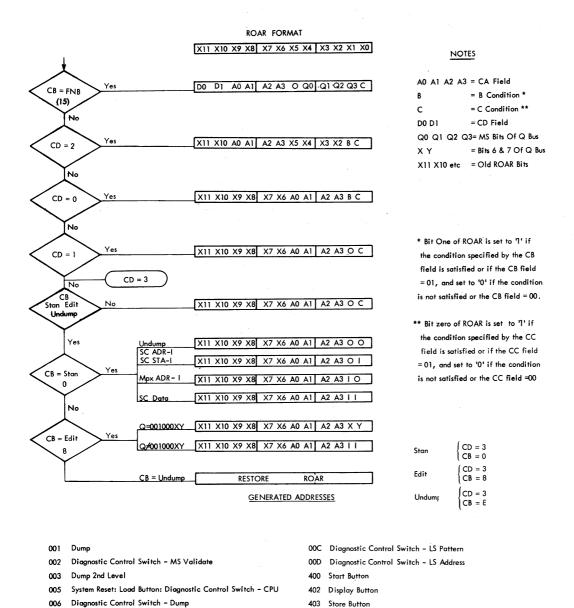

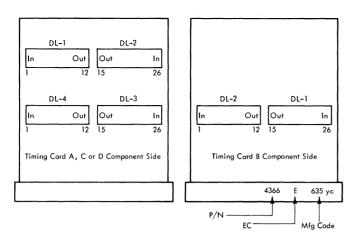

| 4        | ROS Control Word and Basic Functions           | 20         | 54           | Circuits Conditioned by "T" Clock            | 104   |

| 5        | Main Storage Check                             | 21         | 54.1         | Quick Timing Check                           | 104.1 |

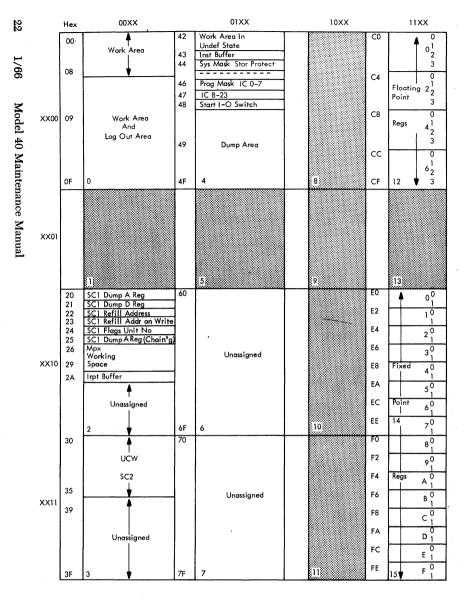

| 6        | Local Storage Contents and Address             | 22         | 55           | TROS Timing – Locations and Sequence of      | 104.9 |

| 7        | Error Check Combination for Multiplex Channel  |            | Ee.          | Adjustments TROS Internal Timing             |       |

|          | Operations                                     | <b>2</b> 3 | 56<br>57     |                                              |       |

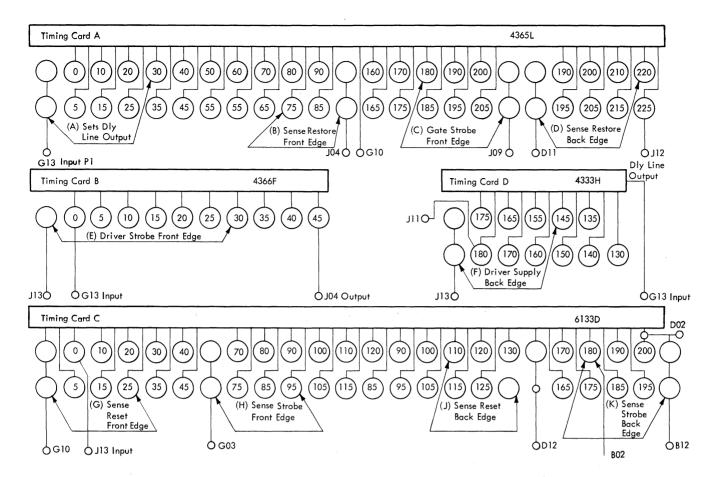

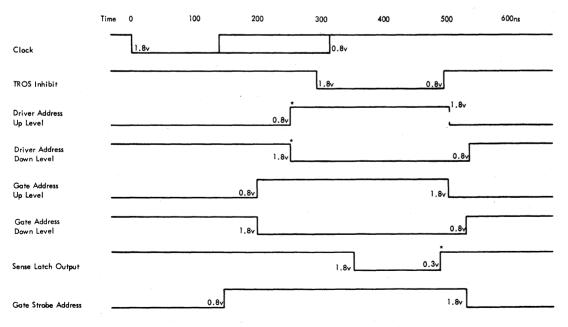

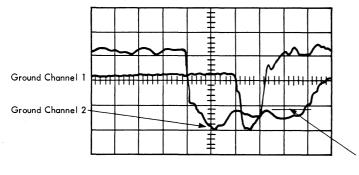

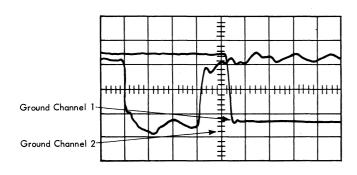

| 8        | Channel Check Indicators                       |            | 57.1         | Timing Cards — Early Type                    | 100   |

| 9        | Programs Available for System/360 Model 40     | 31         | 37.1         | Example for Plugging Early Type Timing Cards | 105   |

|          |                                                |            | 57.2         | Present Timing Cards                         |       |

| AA!      | Fantana                                        |            | 57.2<br>58   | Input/Output Timing                          |       |

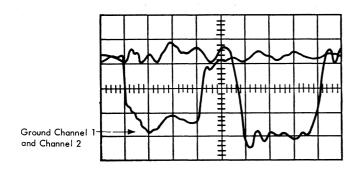

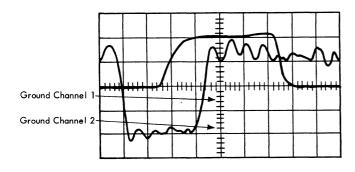

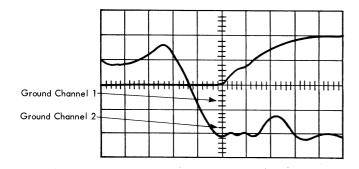

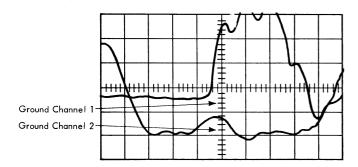

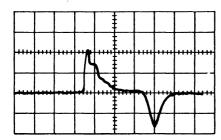

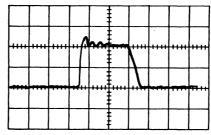

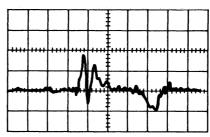

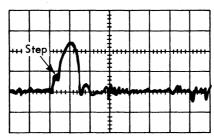

|          | nance Features                                 | 35         | 58.1         | TROS Timing — Scope Traces (2 Sheets)        |       |

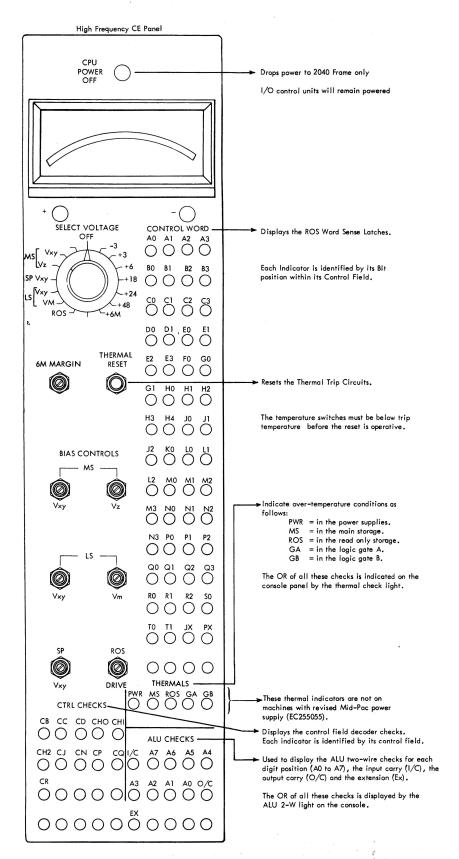

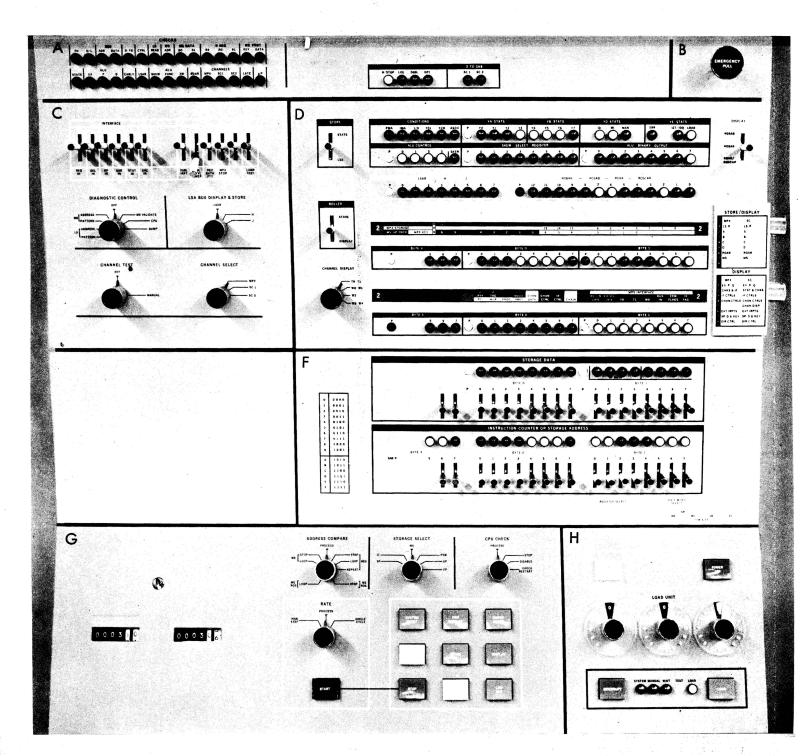

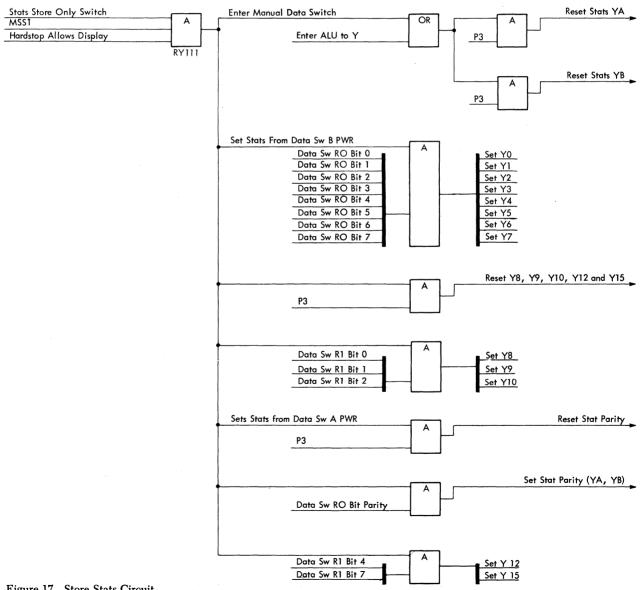

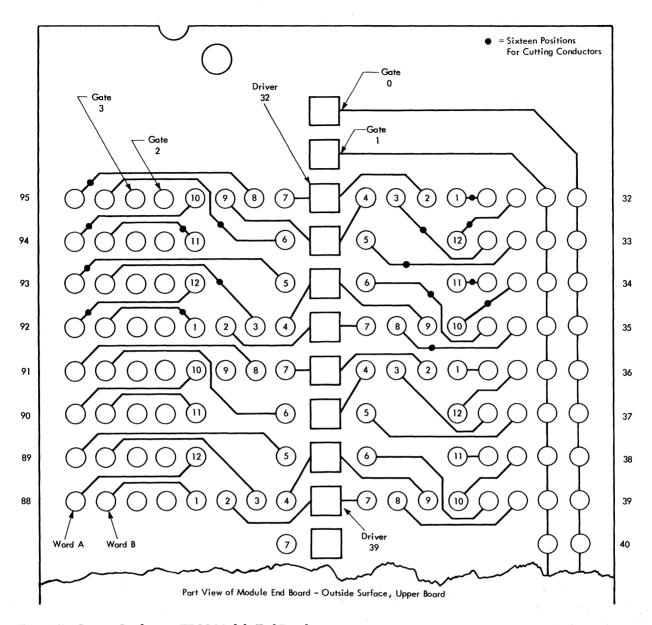

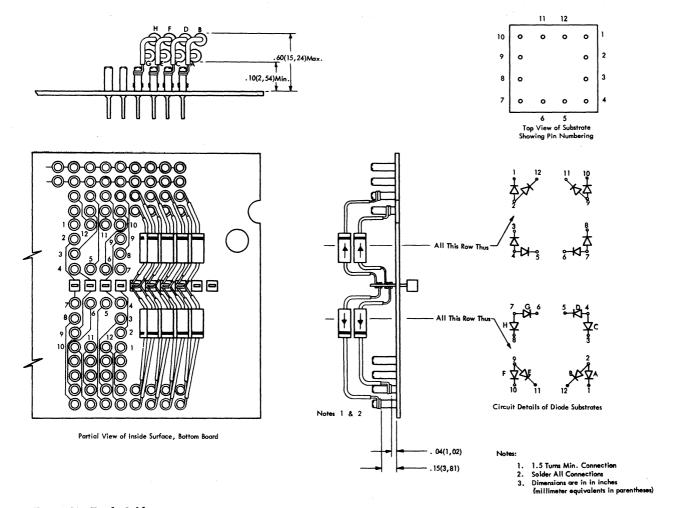

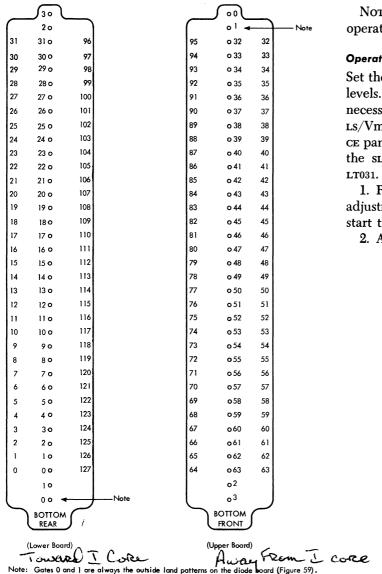

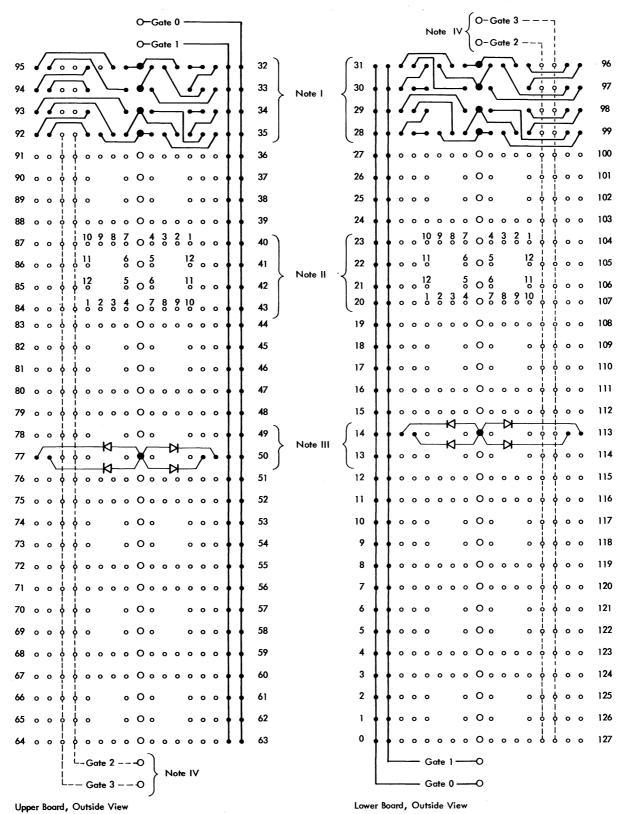

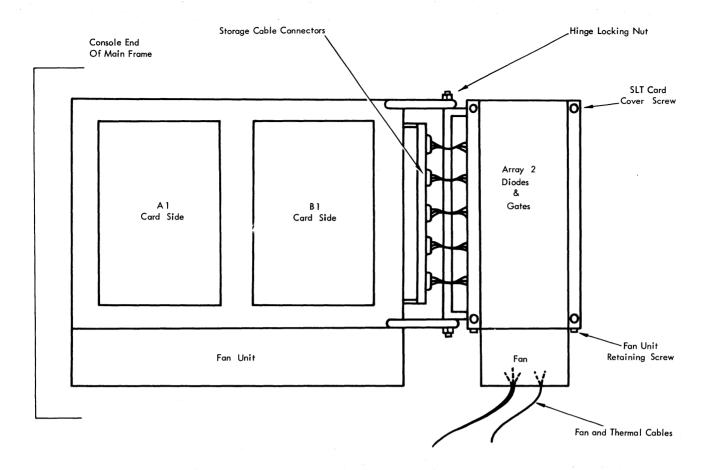

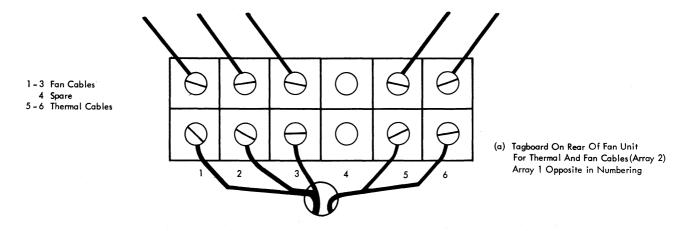

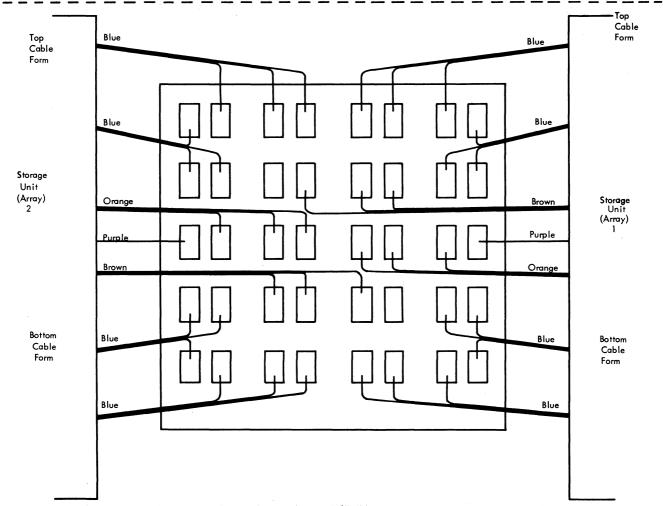

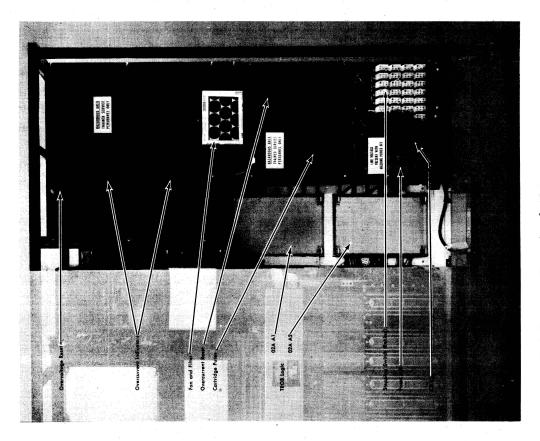

| 10       | High Frequency Internal CE Panel Controls      | 37         | 59           | Cutting Conductors, TROS Module End Board    | 107   |

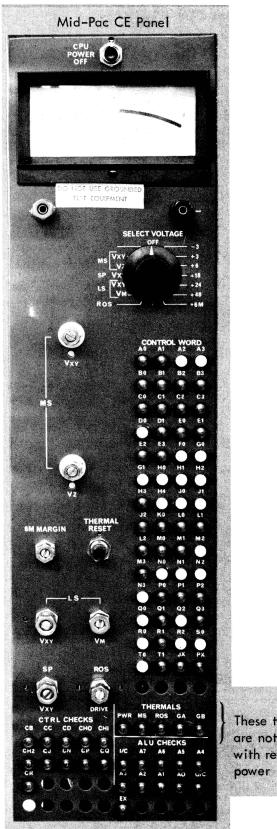

| 11       | Model 40 Internal Console Panel (Mid-Pac PS)   | 37         | 60           | Diode Soldering                              |       |

| 12<br>13 | Model 40 Internal Console Panel (HF)           | 38         | 60.1         | TROS Tape Location Template                  |       |

| 13<br>14 | Console – IBM 2040 Processing Unit             | 38         | 61           | Module End Boards                            | 109   |

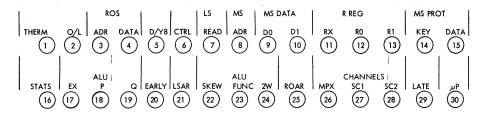

| 14<br>15 | Roll Chart — Upper                             |            | 62           | TROS Module (Exploded View)                  | 110   |

| 16       | Roll Chart — Copper Roll Chart — Lower         |            | 63           | Tape Numbering and Arrangement               | 111   |

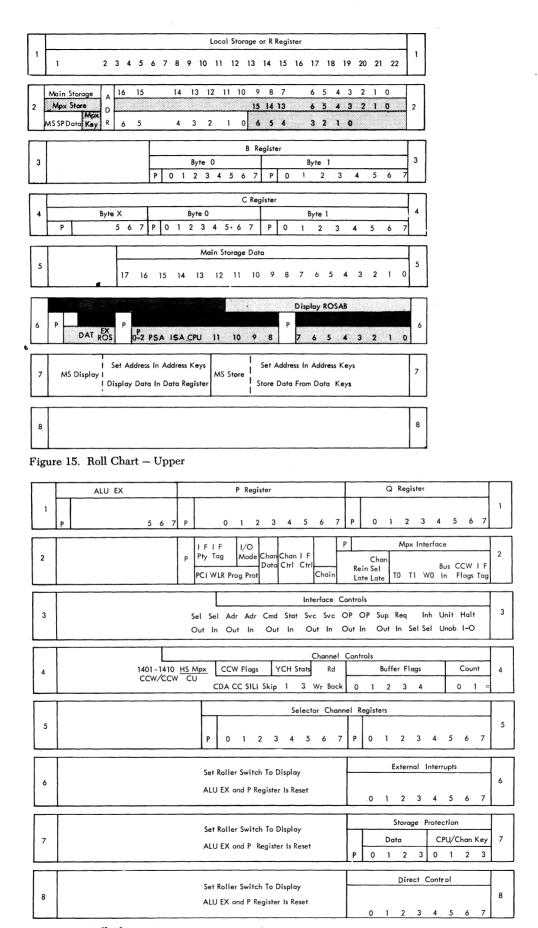

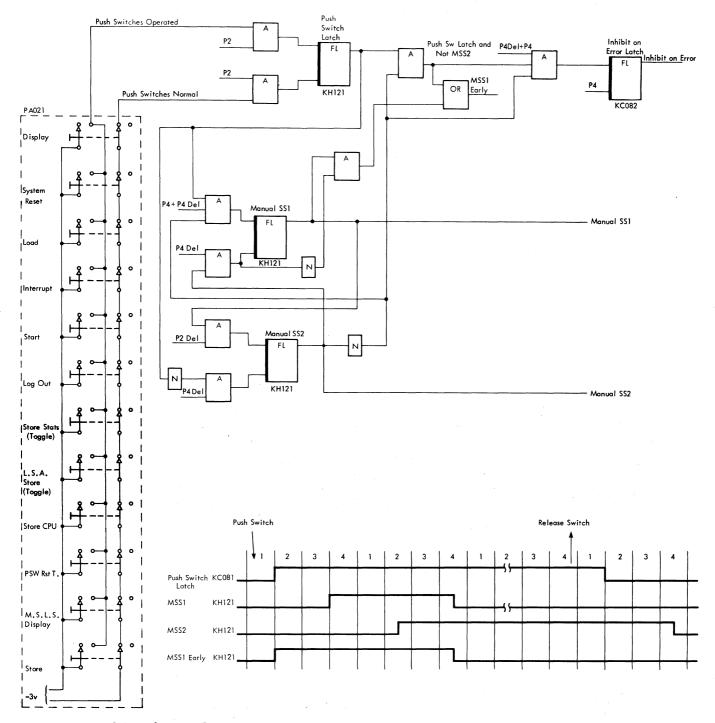

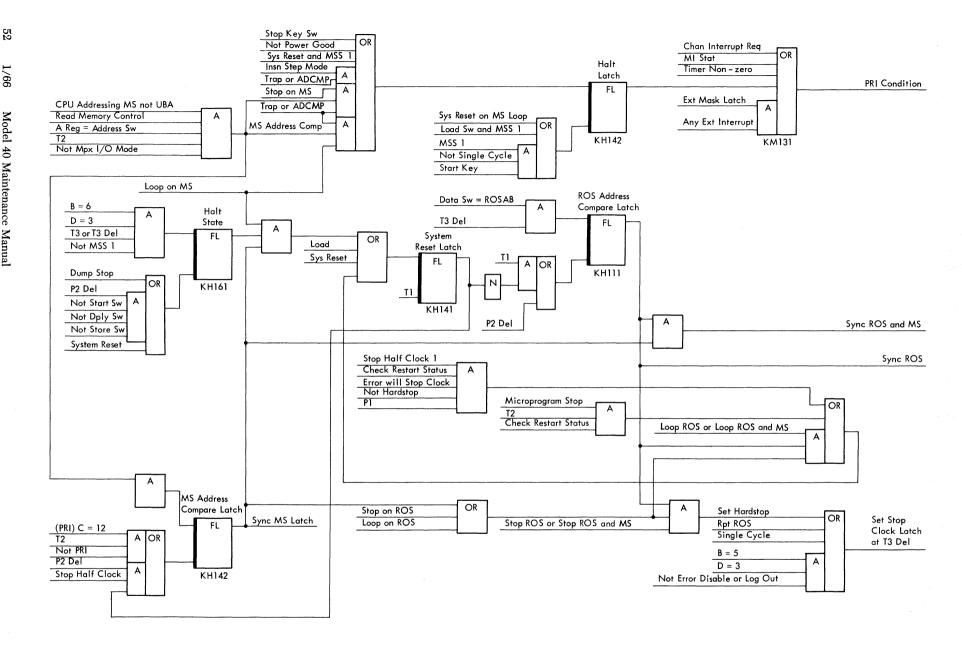

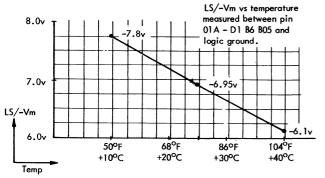

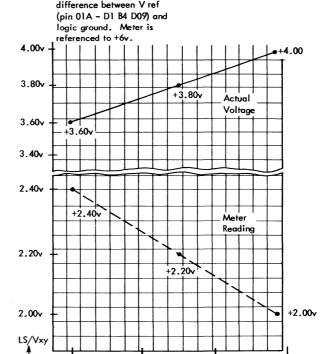

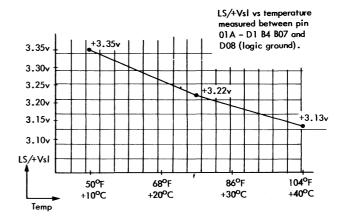

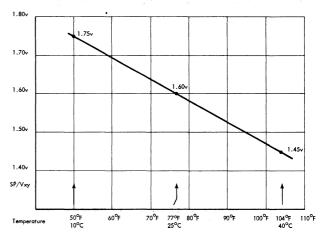

| 17       | Store Stats Circuit                            |            | 64           | Local Storage Tracking (LS/Vm)               |       |

| 18       | Manual Control Timing Ring                     | 44         | 65           | Local Storage Tracking (LS/Vxy)              |       |

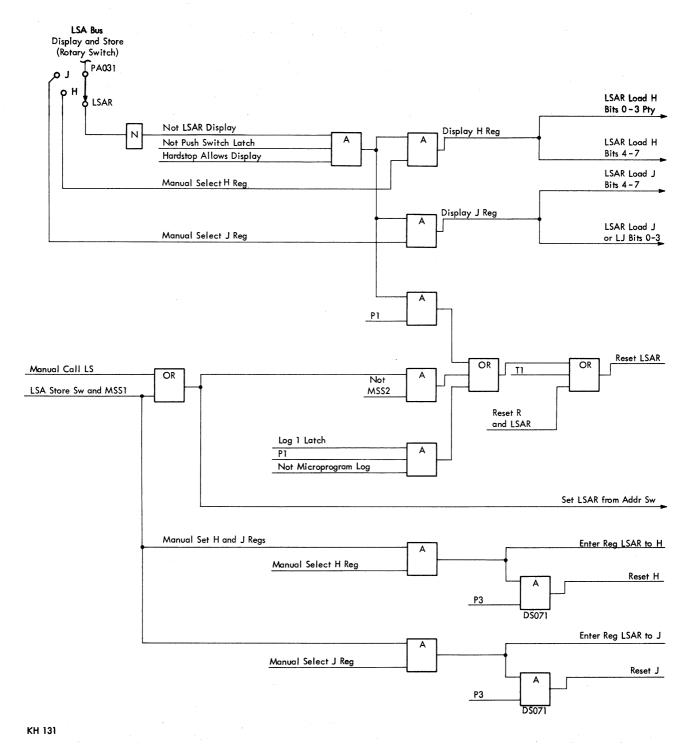

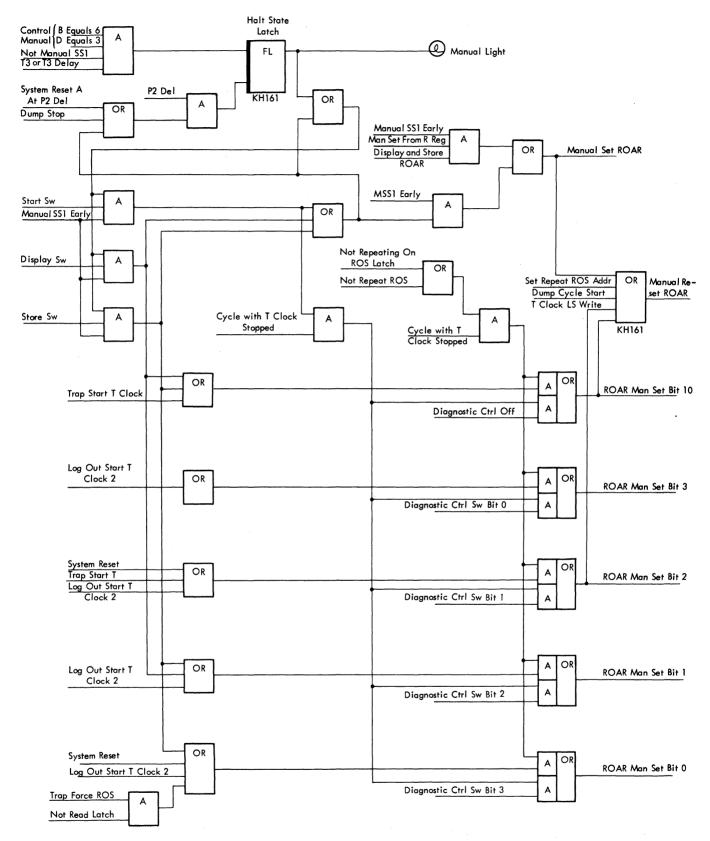

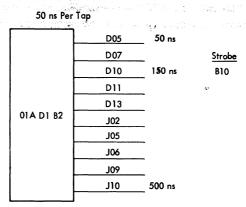

| 19       | LSA Store-Display                              |            | 66           | Local Storage Tracking (LS/Vsl)              | 112   |

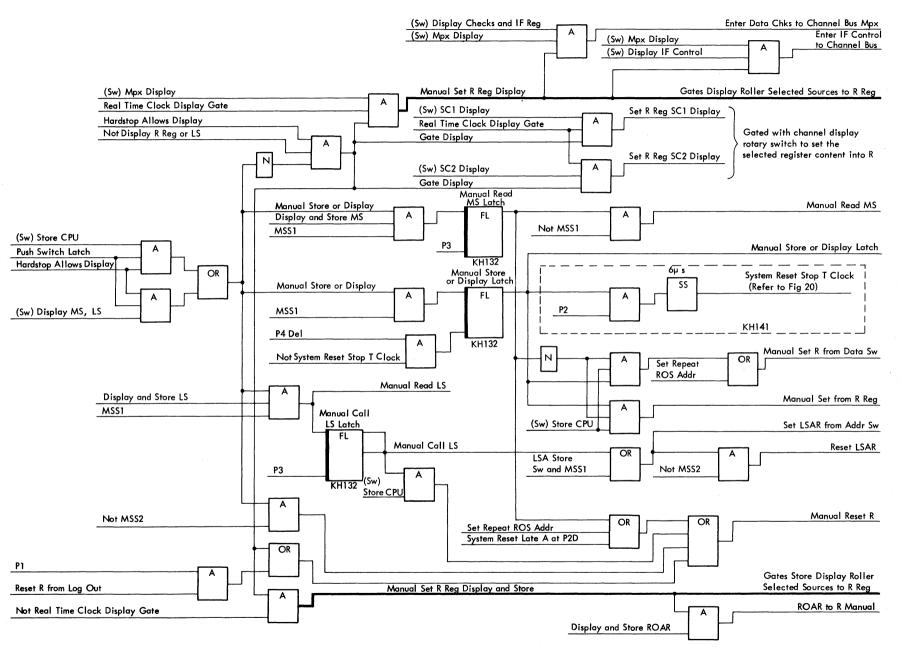

| 20       | Display and Store Display Roller Switches      |            | 67           | Local Storage Delay Lines (01AD1B2)          |       |

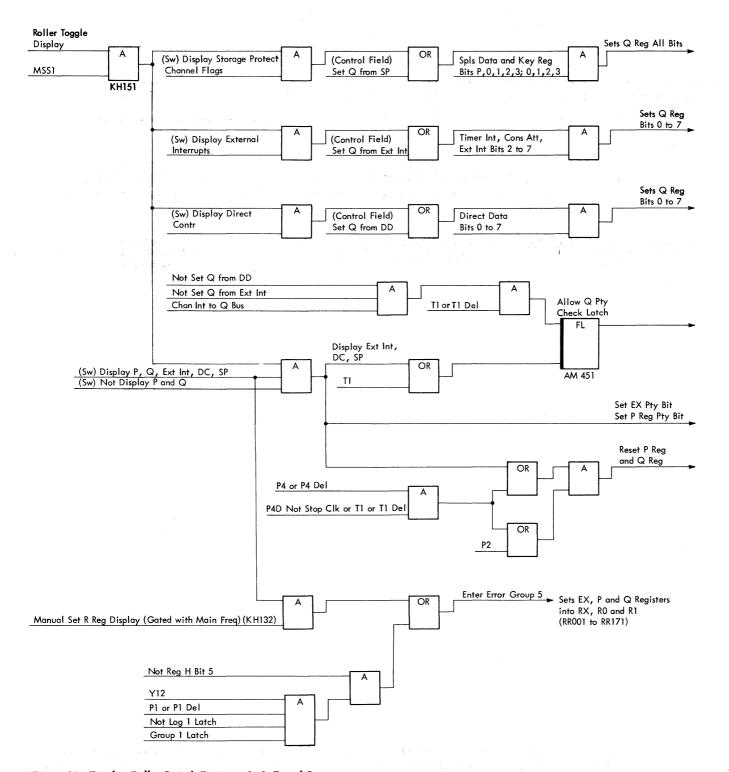

| 20<br>21 | Display Roller Switch Positions 1,6,7, and 8   |            | 67.1         | Local Storage Control Lines                  |       |

| 22       | Address Compare Switch                         |            | 68           | Voltage vs Temperature Tracking (Storage     |       |

| 23       | ROAR Forced Address                            |            |              | Protect)                                     | 113   |

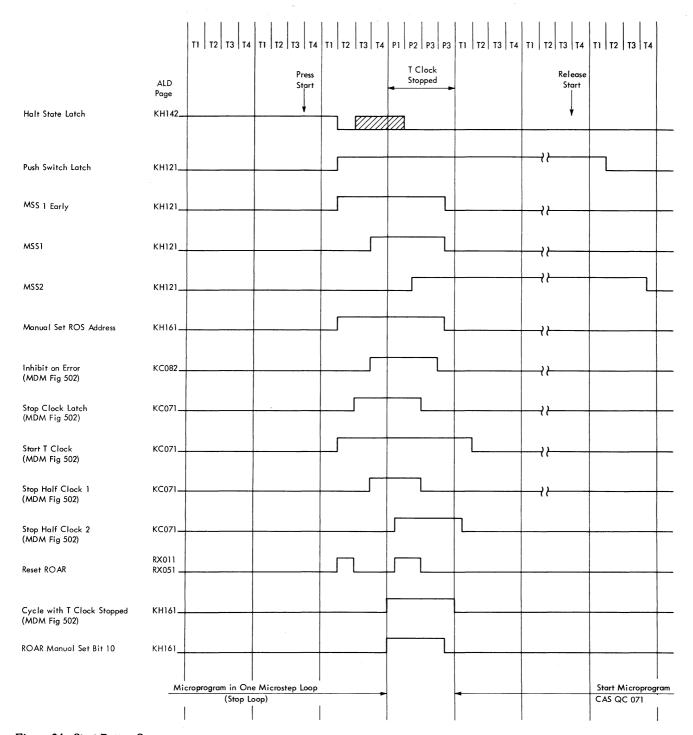

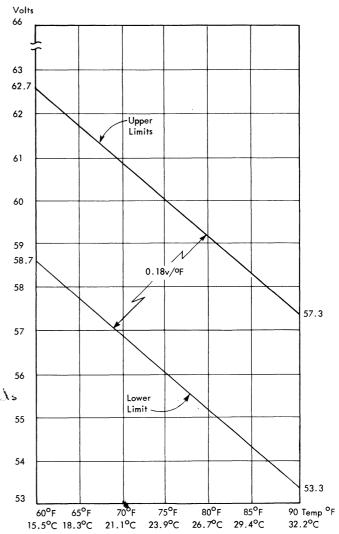

| 24       | Start Button Sequence                          |            | 69           | Main Storage Vxy Versus T (128K,64K)         | 114   |

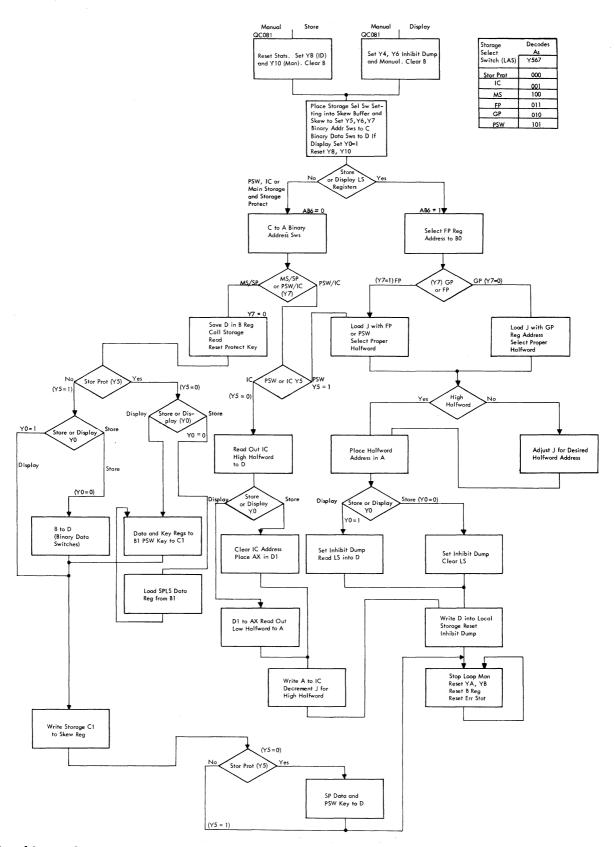

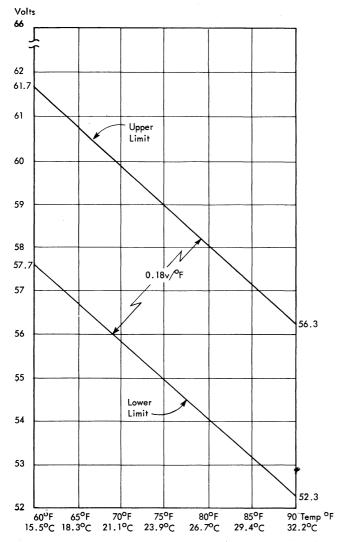

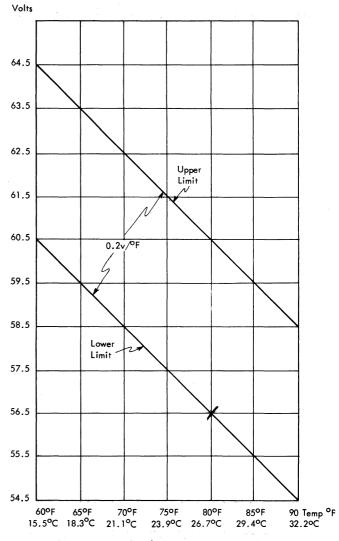

| 25       | Manual Store and Display                       | 56         | 70           | Main Storage Vxy Versus T (32K)              | 115   |

| 26       | Microprogramming Initiated by Start            | •          | 71           | Main Storage Vz Versus T (128K,64K,32K)      | 115   |

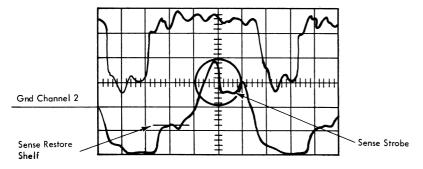

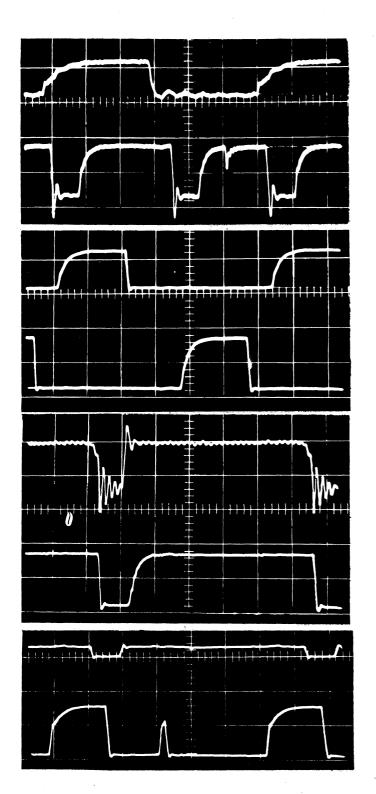

|          | Pushbutton                                     | 57         | 71.1         | Main Storage Scope Traces (2 Sheets)         | 116.2 |

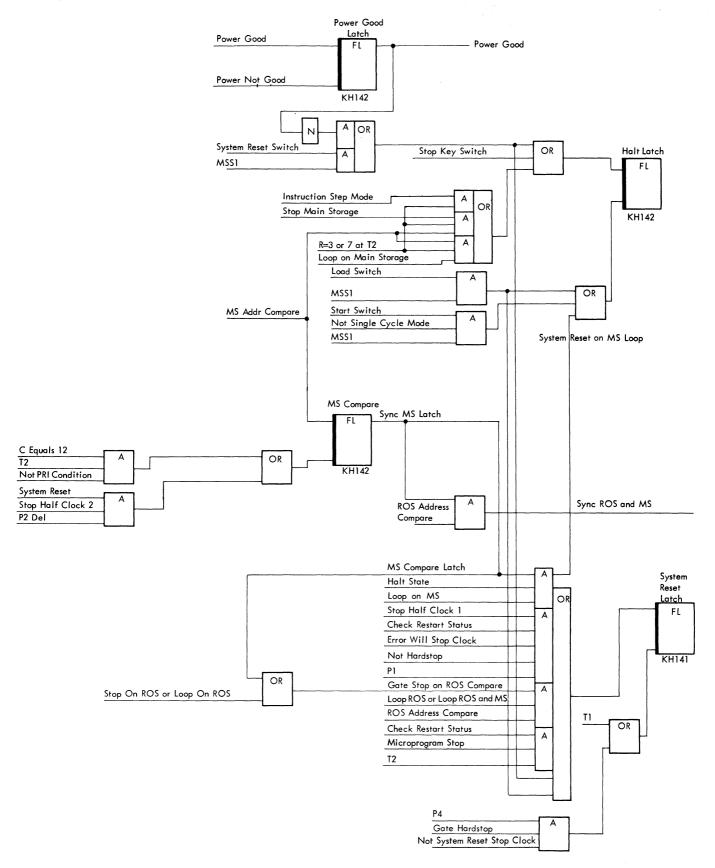

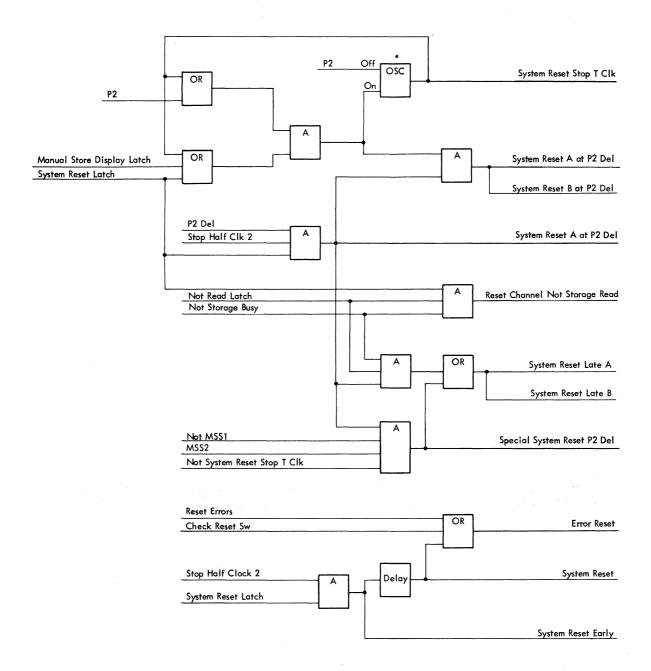

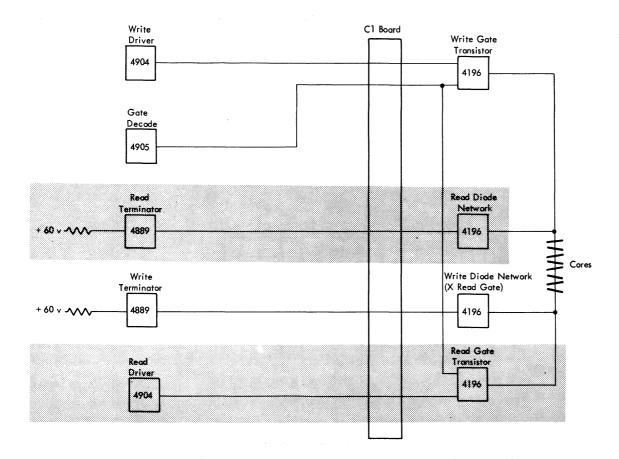

| 27       | System Reset Microprogram                      |            | 71.2         | Simplified Drive Circuit                     |       |

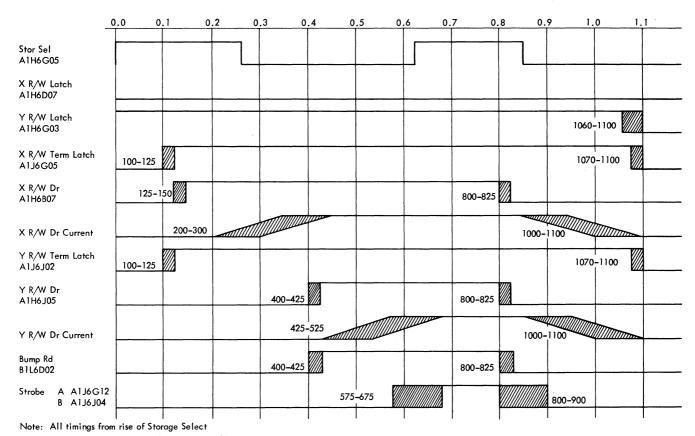

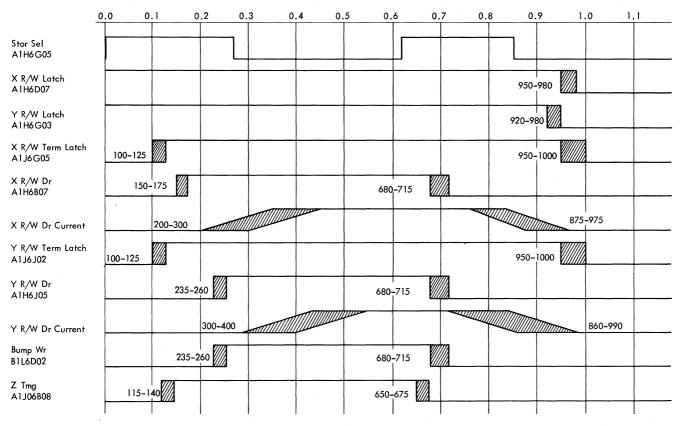

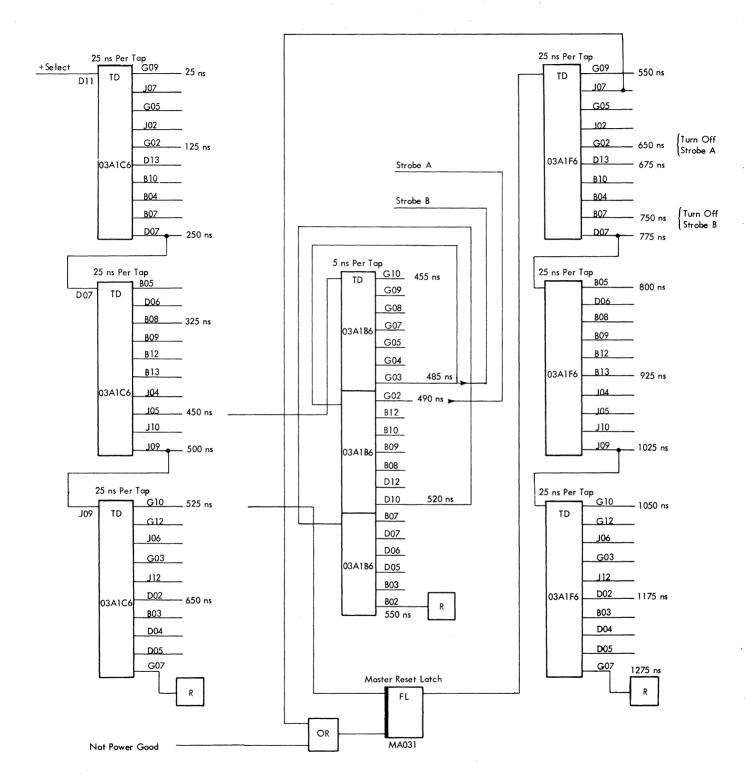

| 28       | System Reset Latch                             |            | 71.3         | Main Storage Timing Chart                    |       |

| 29       | System Resets                                  |            | 72           | M-7 Storage Read Timings                     | 116.6 |

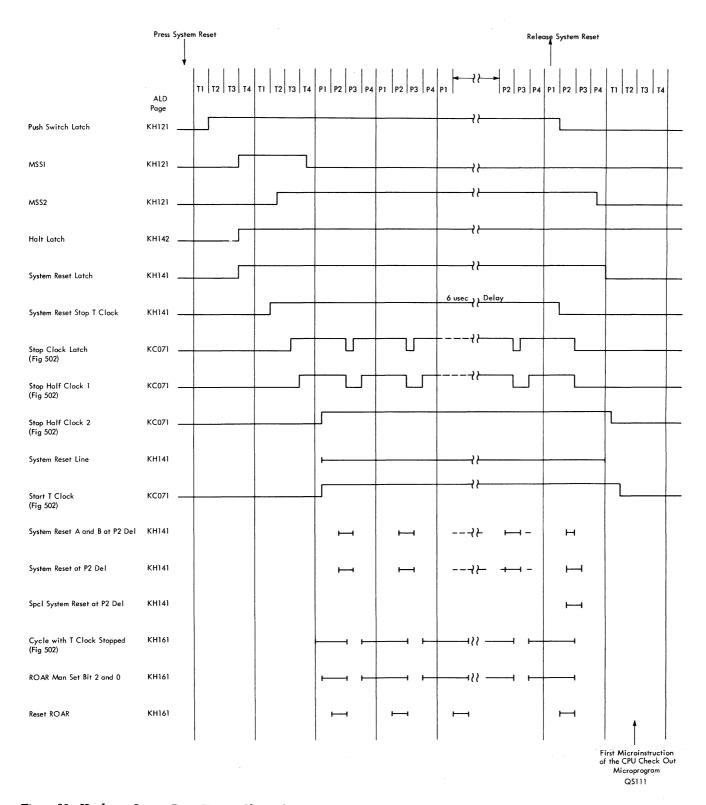

| 30       | Hardware System Reset Timing Chart             |            | 72.1         | M-7 Storage Write Timings                    | 116.6 |

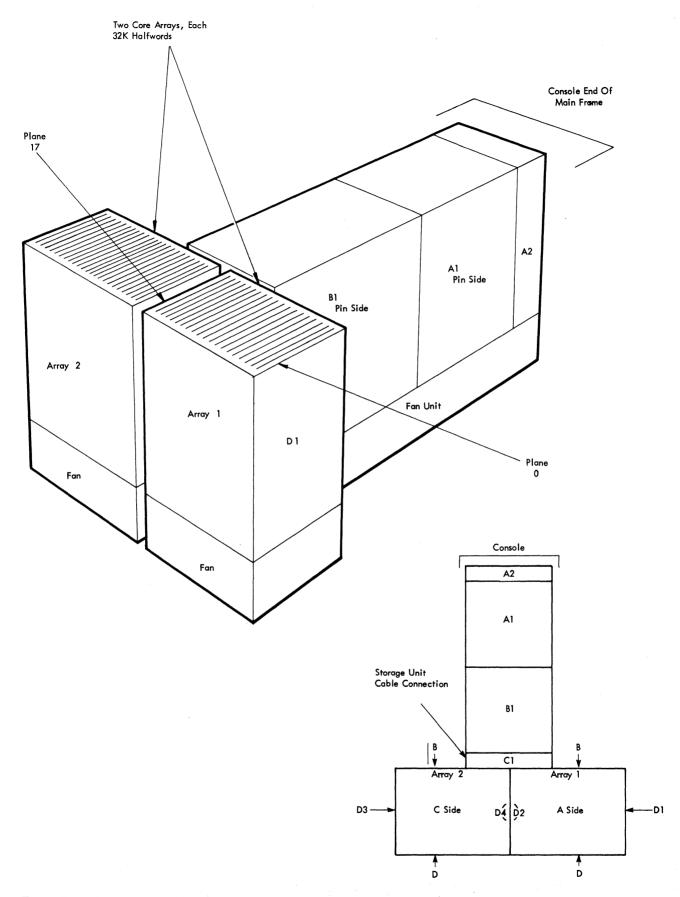

|          | (2 Sheets)                                     | 62         | <b>7</b> 3   | 64K Main Storage (Layout Within Main         |       |

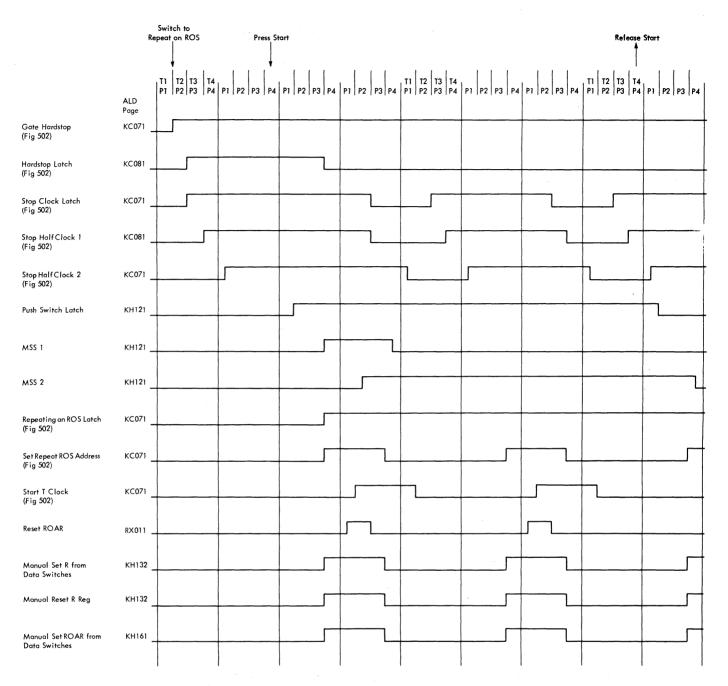

| 31       | Stop on ROS Timing Chart                       | 66         |              | Frame)                                       |       |

| 32       | Repeat on ROS Timing Chart                     | 67         | 74           | Changing a Storage Unit                      | 118   |

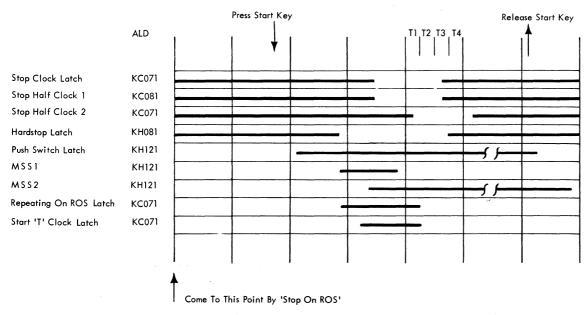

| 33       | Start in Single Cycle Mode Timing Chart        | 70         | 75           | Storage Unit Cable Connection                | 119   |

| 34       | Loop on Main Storage                           | 71         | 76           | Delay Line Circuits with Locations and       |       |

| 35       | Displaying and Storing Procedure When in       |            |              | Pin Numbers                                  | 120   |

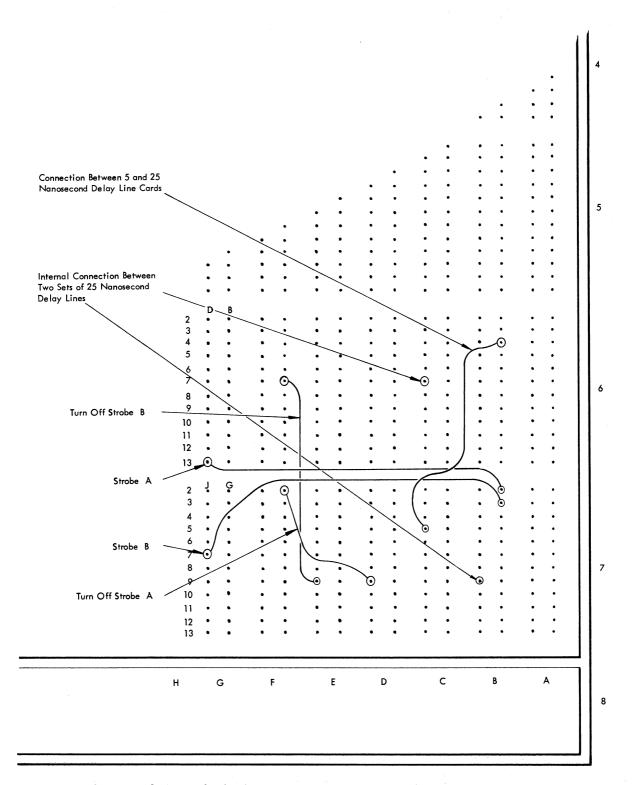

|          | Manual Stop Loop                               | <b>7</b> 3 | 77           | Panel A1 Pin Side (Example of Delay Line     |       |

| 36       | Storing Procedure When in Hardstop Condition   | <b>74</b>  |              | Wiring)                                      |       |

| 37       | Displaying Procedure When in Hardstop          |            | 78           | Allocation of Fans and Filters               | 123   |

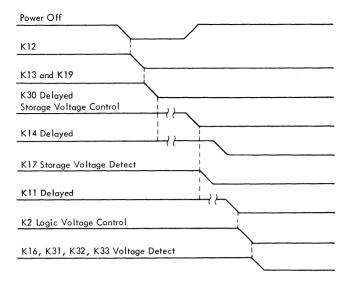

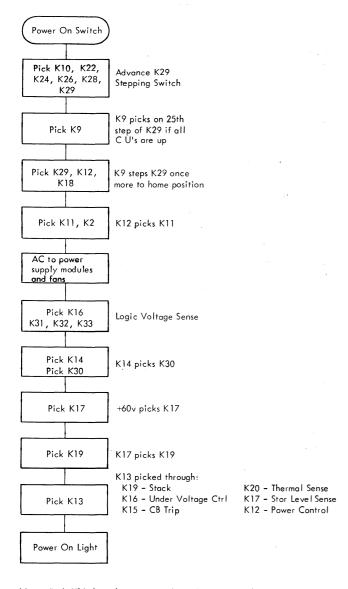

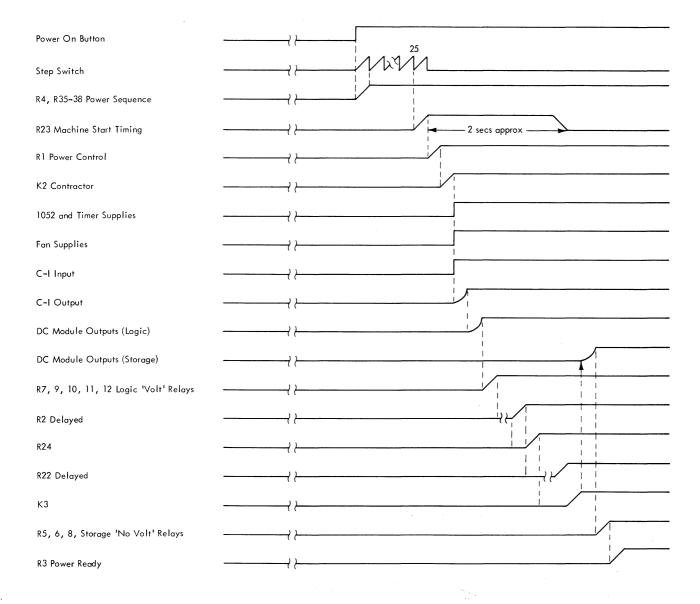

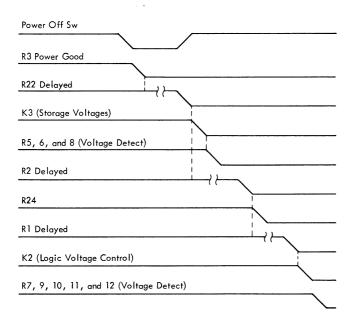

|          | Condition                                      | 75         | <b>7</b> 9   | Mid-Pac Power On Sequence and Timing         |       |

| 38       | Entries to and Exits from the CPU Checkout     |            | <b>-</b>     | Chart                                        | 126.2 |

|          | Microprogram                                   | 76         | 79.1         | Mid-Pac Power Off Sequence and Timing        |       |

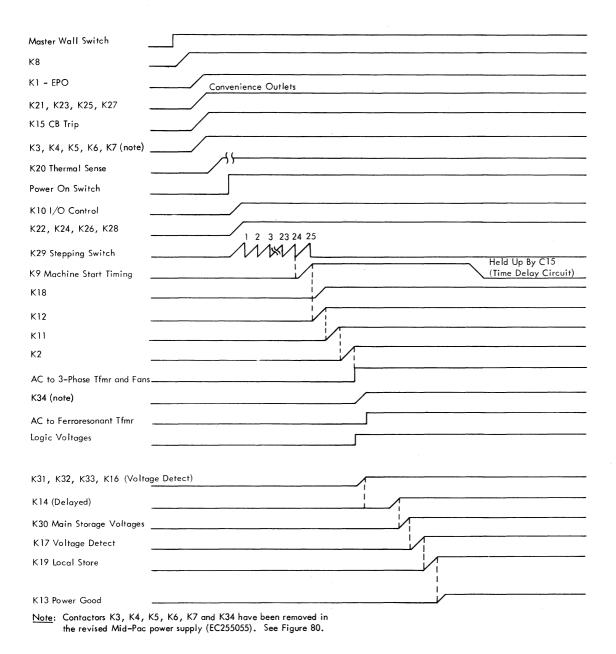

| 39       | Local Store Areas and Patterns Used in         |            |              | Chart                                        |       |

|          | First Routine                                  |            | 80           | Mid-Pac Power On Sequence                    | 128   |

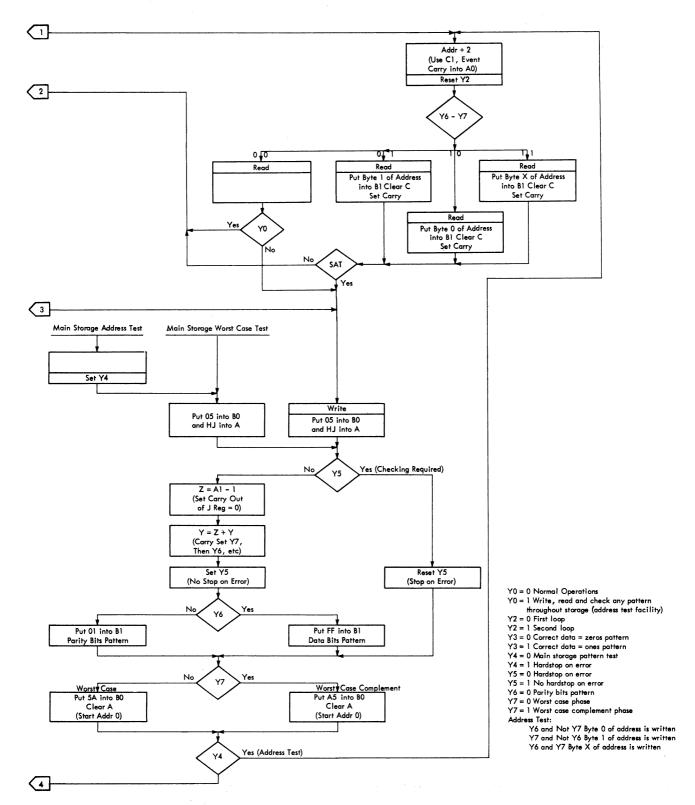

| 40       | Local Store Diagnostic (2 Sheets)              | 80         | 81           | Mid-Pac Power Supply Reference Data          | 129   |

| 41       | Main Storage Pattern and Address Test          |            | 82           | High Frequency Power On Sequence and         |       |

|          | (2 Sheets)                                     |            | 90.1         | Timing Chart                                 | 130   |

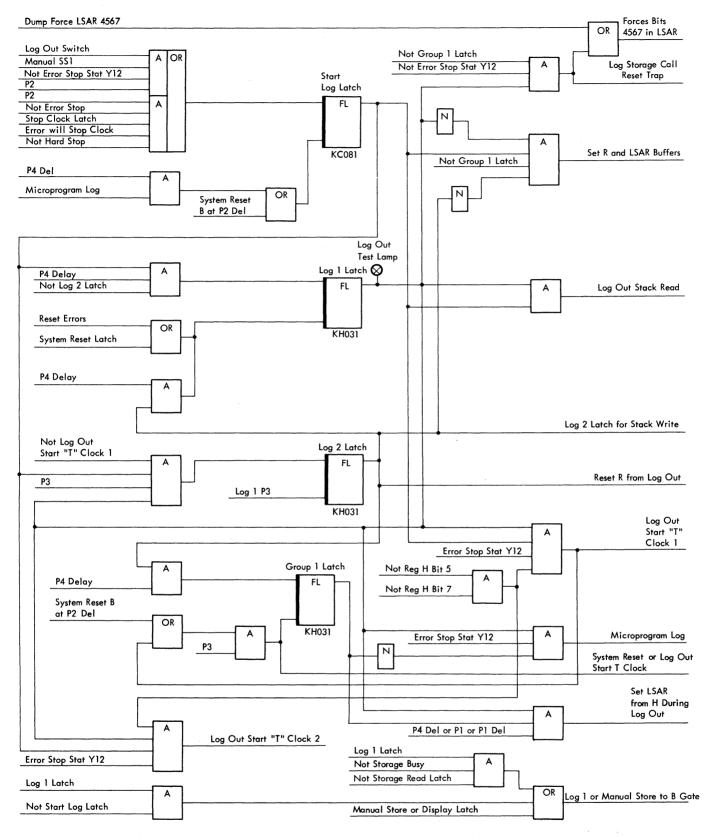

| 42       | General Outline of Log Out                     |            | 82.1         | High Frequency Power Off Sequence and        | 100 1 |

| 43       | Log Out Latches and Controls                   |            | 62           | Timing Chart                                 | 130.1 |

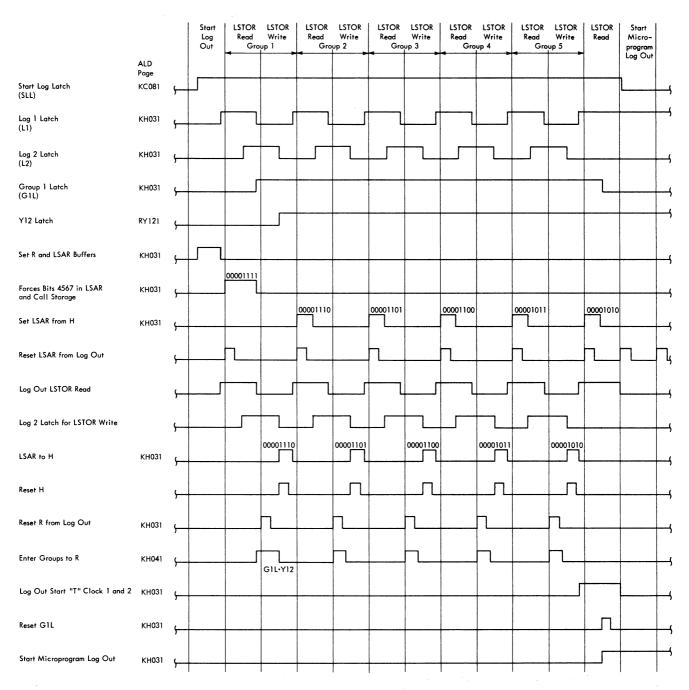

| 44       | Hardware Log Out Timing Chart                  |            | 83           | High Frequency (2.5 kc) Power Supply         | 101   |

| 45       | Format of Hardware Log Out in Local Storage    |            | 84           | Reference Data                               |       |

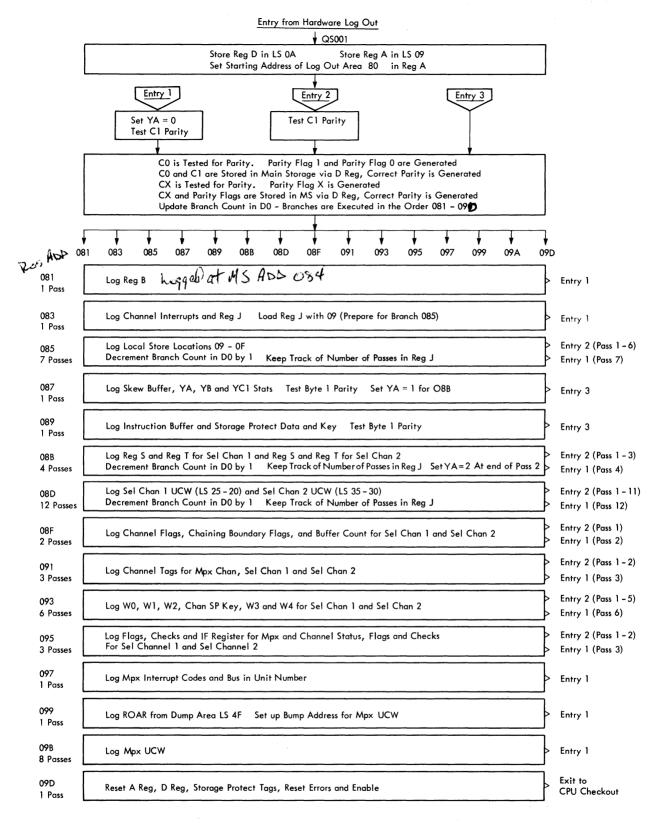

| 46       | Chart of Microprogram Log Out                  | 91         | 85           |                                              |       |

| 47       | Main Storage Allocation for Log Out (2 Sheets) | 92         | 30           | High Frequency Terminal Board Locations      | 133   |

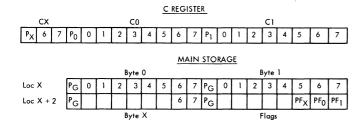

| 48       | C Register to Main Storage                     |            | Location     | ne                                           |       |

| 49       | Determining the Contents of the J Register     | 95         |              |                                              | 105   |

| 50       | Determining the Value of ROBAR from            | ٥٢         | 86<br>97     | SLT Gates A and B                            |       |

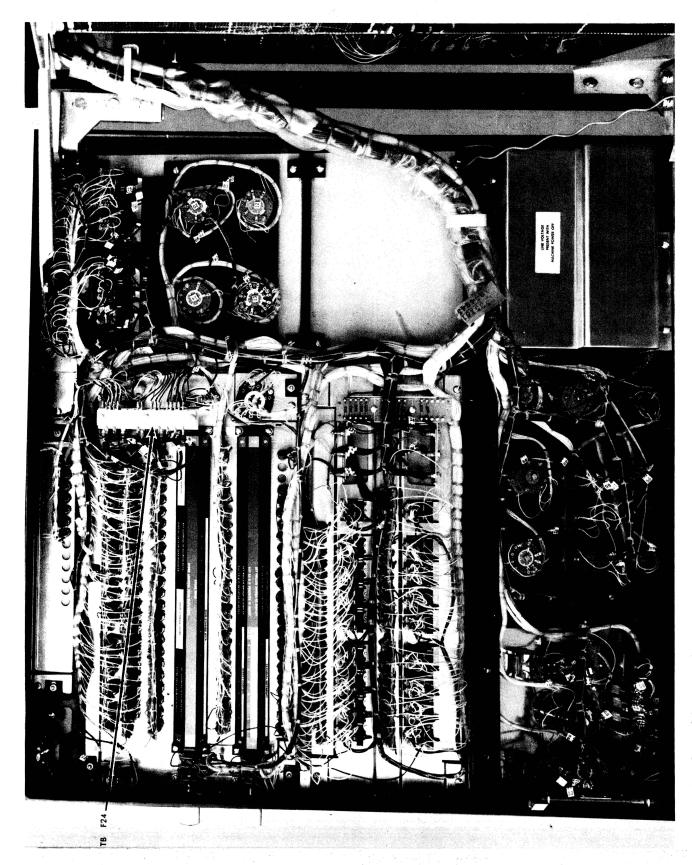

|          | Formatted Log Out                              | 95         | 87           | CPU — Right Side                             | 138   |

| FIGURE | TITLE                                | PAGE | FIGURE | TITLE                                   | PAGE |

|--------|--------------------------------------|------|--------|-----------------------------------------|------|

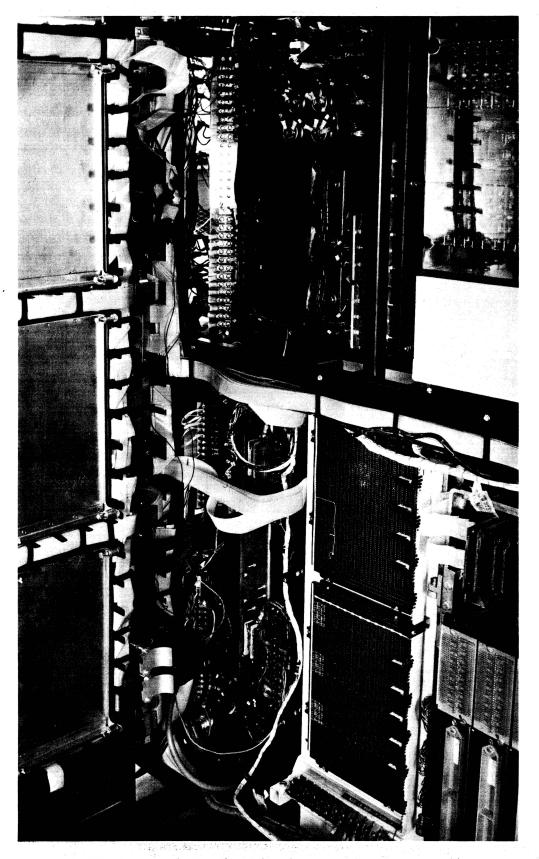

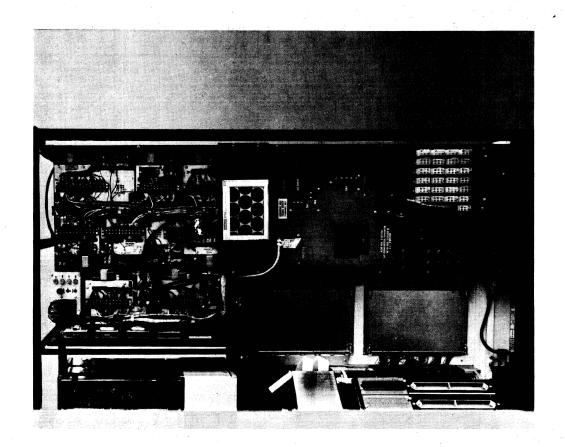

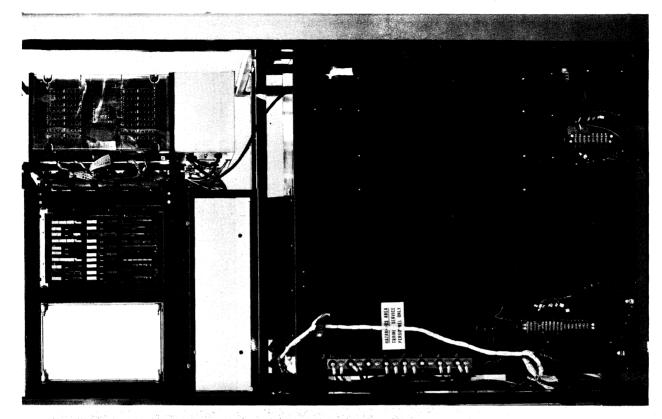

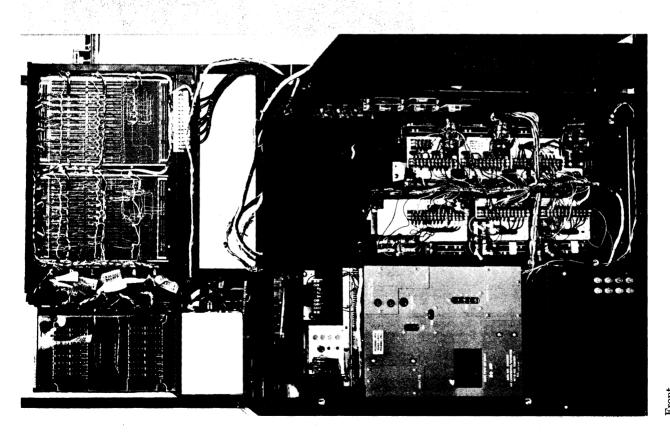

| 88     | CPU - Left Side and Tailgate         | 139  | 95     | High Frequency Power Supply             | 147  |

| 89     | CPU — Left Side                      | 140  | 96     | Wall Frame High Frequency Power Supply  | 148  |

| 90     | TROS Gates                           | 141  | 97     | Console Panel (Rear View)               | 149  |

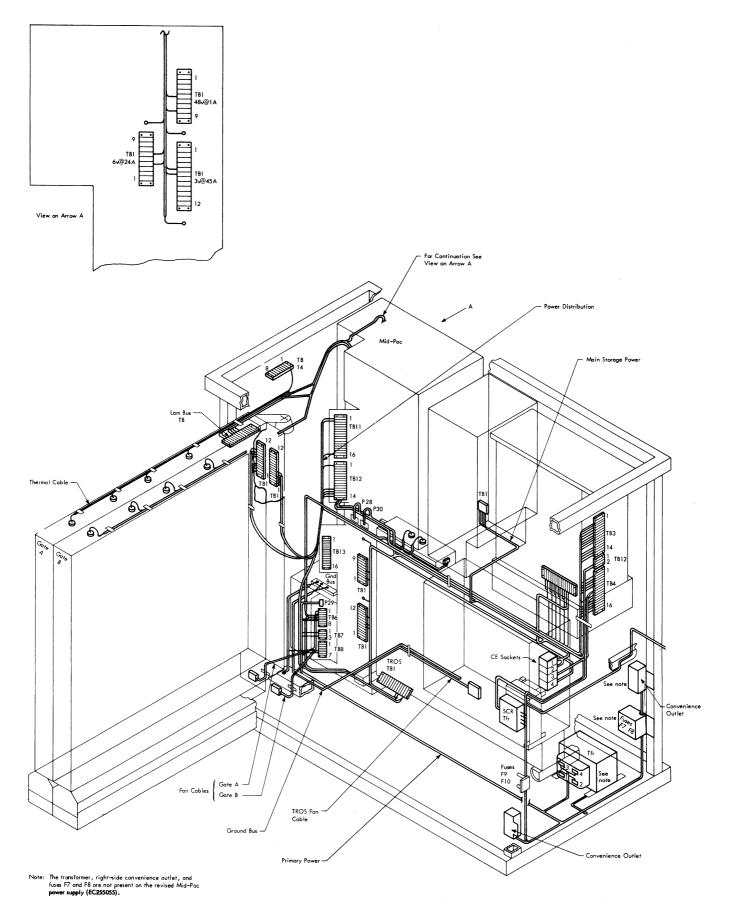

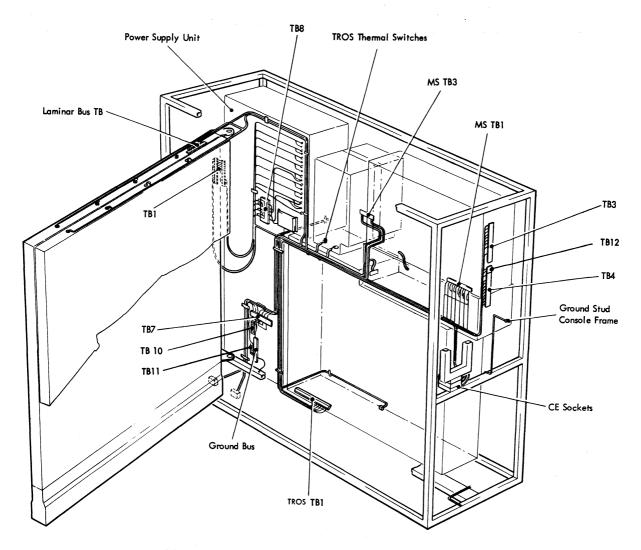

| 91     | Console End (Doors Open)             | 142  | 98     | Board Layout of CPU Logic Gates         | 151  |

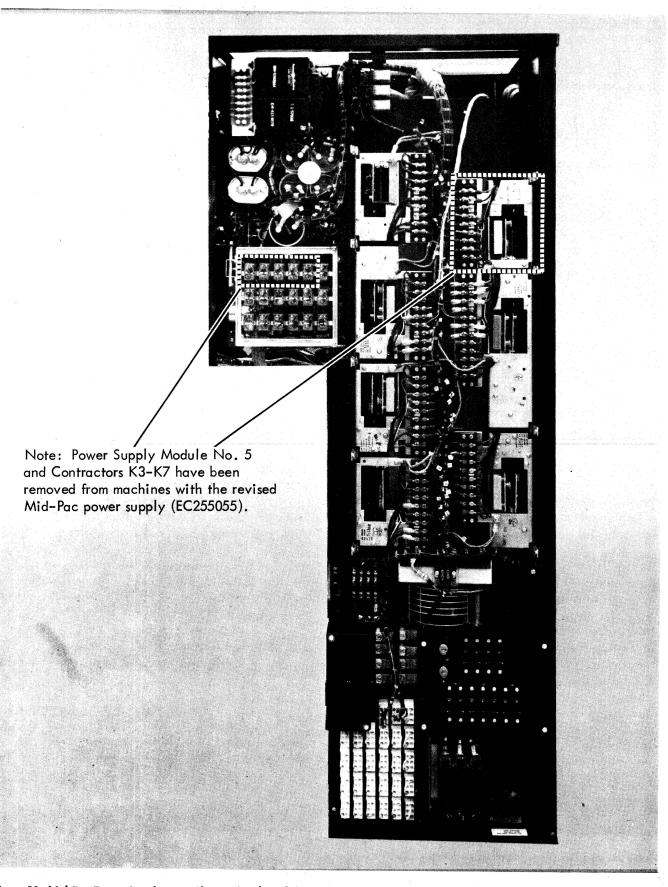

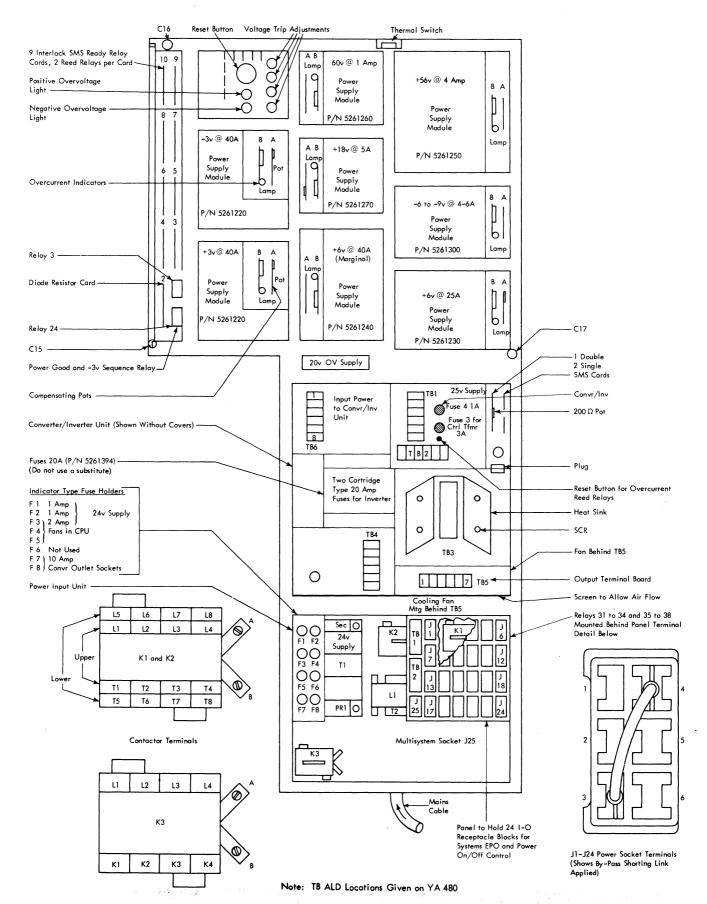

| 92     | Mid-Pac Power Supply Unit (2 Sheets) | 143  | 99     | SLT Card and Board Addressing Scheme    | 151  |

| 93     | Mid-Pac Power Supply                 | 145  | 100    | Version Numbers and Additive Card Codes | 152  |

| 94     | High Frequency Power Supply Unit     | 146  |        |                                         |      |

|        |                                      |      |        |                                         |      |

|        |                                      |      |        |                                         |      |

Safety cannot be overemphasized. To insure your personal safety and the safety of co-workers, make it an everyday practice to observe safety precautions at all times. You should be familiar with the general safety practices and procedures for performing artificial respiration outlined in IBM Form 124-0002.

Always use a reliable voltmeter to verify that power is actually off after using power-off switches.

Although all power supplies are provided with

bleeder resistors to drain off capacitor charges when power is dropped, it is wise to check all capacitors with a meter before attempting maintenance. A defective bleeder resistor could create an unexpected hazard.

Note: In a multi-system complex, if the EPO bypass switch must be activated to isolate a system, deactivate the switch as soon as possible. The proper procedure is outlined in "Dual/Multi-System Emergency Power Off (EPO)."

# **Abbreviations**

|                |                                           |                  | - 10 All David                           |

|----------------|-------------------------------------------|------------------|------------------------------------------|

| A0             | A Register byte 0                         | LSAR             | Local Storage Address Register           |

| A1             | A Register byte 1                         | LSD              | Least Significant Digit                  |

| AX             | A Register Extension                      | MAP              | Maintenance Analysis Procedure           |

| $\mathbf{ALU}$ | Arithmetic and Logic Unit                 | MC               | Machine Check                            |

| AMWP           | Bits 12-15 of the PSW                     | MDM              | Maintenance Diagram Manual               |

| A Reg          | A Register                                | MI               | Maskable Interrupt                       |

| ASCII          | American Standard Code for Information    | MS               | Main Storage                             |

|                | Interchange                               | MSC              | Machine Status Chart                     |

| В              | Base Register                             | MSD              | Most Significant Digit                   |

| BCD            | Binary Coded Decimal                      | MSS              |                                          |

| BCDIC          |                                           |                  | Manual Single Shot                       |

|                | Binary Coded Decimal Interchange Code     | OS               | Operating System                         |

| B Reg          | B Register                                | P                | Parity (bit)                             |

| CAS            | Control Automation System                 | PC               | Parity Check                             |

| CAW            | Channel Address Word                      | P <b>CI</b>      | Program Control Interrupt                |

| CC             | Chain Command                             | PG               | Parity Generation                        |

| CC             | Condition Code                            | PRI              | Program Interrupt                        |

| CCW            | Channel Command Word                      | Prg Chk          | Program Check                            |

| CDA            | Chain Data Address                        | PSA              | Protected Storage Address                |

| CE             | Channel End                               | PSW              |                                          |

| CI             | Command Immediate                         |                  | Program Status Word                      |

| CLD            | CAS Logic Diagram                         | Pty              | Parity                                   |

| CLFC           | Condensed Logic Flow Chart                | Rx               | Operand Register                         |

|                | _                                         | ROAR             | Read Only Address Register               |

| COBOL          | Common Business Oriented Language         | ROBAR            | Read Only Back-up Address Register       |

| CPU            | Central Processing Unit                   | ROS              | Read Only Storage                        |

| C Reg          | C Register                                | ROSCAR           | ROS Channel Address Register             |

| CSW            | Channel Status Word                       | RR               | Register-to-register operations          |

| CT             | Count                                     | R Reg            | R Register                               |

| CU             | Control Unit                              |                  |                                          |

| CX             | C Register Extension                      | RS               | Register-to-storage operations           |

| C0             | C Register byte 0                         | rtpt             | reinterpret                              |

| C1             | C Register byte 1                         | RX               | Register-to-indexed-storage operations   |

| D              | Displacement Address                      | RX               | R Register Extensions                    |

|                |                                           | R0               | R Register byte 0                        |

| D Reg          | D Register                                | R1               | R Register byte 1                        |

| D0             | D Register byte 0                         | R/W              | Read/write                               |

| D1             | D Register byte 1                         | SAB              | Storage Address Bus                      |

| DE             | Device End                                | SAT              | Storage Address Test                     |

| Decr           | Decrement                                 | SC               | Selector Channel                         |

| Del            | Delayed                                   | SER              | System Environment Recording             |

| Des            | Destination                               |                  |                                          |

| DM             | Diagnostic Monitor                        | SEREP            | System Environment Record Edit and Print |

| EBCDIC         | Extended Binary Coded Decimal Interchange | SI               | Storage-and-immediate-operand operation  |

| LDODIO         | Code                                      | SIO              | Start I/O (Input/Output)                 |

| EC             | Engineering Change                        | SILI             | Suppress Incorrect Length Indicator      |

| ECAD           | Error Checking Analysis Diagram           | SLT              | Solid Logic Technology                   |

|                | Environment Record Edit and Print         | SMS <sup>a</sup> | Standard Modular System                  |

| EREP           |                                           | SP               | Storage Protect                          |

| FNB            | Functional Branch                         | SPLS             | Storage Protect Local Storage            |

| FORTRAN        | Formula Translating System                | S Reg            | S Register                               |

| FP             | Floating Point                            | SS               | Storage-to-storage operation             |

| GP             | General Purpose (Registers)               | SSK              | Set Storage Key                          |

| HEX            | Hexadecimal                               | STATS            | Staticizer Latches                       |

|                |                                           | SVC              | Supervisor call (op code)                |

| HIO            | Halt I/O (Input/Output)                   | SX               | S Register Extension                     |

| I .            | Immediate Data (not in text)              | SO SO            | S Register byte 0                        |

| IB             | Instruction Buffer                        | S1               | •                                        |

| IC             | Instruction Count                         |                  | S Register byte 1                        |

| ICC            | Interface Control Check                   | TCH              | Test Channel                             |

| ID             | Inhibit Dump                              | TIC              | Transfer in Channel                      |

| IDQ            | Invalid Decimal Digit (on Q bus)          | TIO              | Test I/O (Input/Output)                  |

| IF             | Interface                                 | TROS             | Transformer Read Only Storage            |

| ILC            | Instruction Length Code                   | UBA              | Use Bump Address                         |

| I/O            | Input/Output                              | UCW              | Unit Control Word                        |

| IOCS           | Input/Output Control System               | Unobt            |                                          |

|                | Initial Program Load                      |                  | Unobtainable                             |

| IPL            |                                           | WLR              | Wrong Length Record                      |

| IR             | Interrupt Request                         | X                | Index Register                           |

| ISA            | Invalid Storage Address                   |                  | 9                                        |

| ISK            | Insert Storage Key                        | YC               | Carry Latch                              |

| IZT            | Integrated Zero Test                      | YCH 1, 3         | Selector Channel Stats 1, 3              |

| L              | Operand Length                            | YCI              | Indirect Function Carry Stat             |

| LDB            | Load Button                               | YCD              | Direct Function Carry Stat               |

| LS             | Local Storage                             | $\mu P$          | Microprogram                             |

| LS             | Local Storage                             | <b>~</b> ±       |                                          |

# **Maintenance Concepts**

The IBM System/360 Model 40 provides features to assist the customer engineer in: failure location, fault location, deferred maintenance and rapid repair.

#### **Fault Location**

After a system malfunction has been detected, the troubleshooting aids available to the customer engineer are: indicators and manual controls, internal diagnostics, external diagnostics, external maintenance programs and supporting documentation.

#### **Deferred Maintenance**

The log out facility allows deferred maintenance. Certain failures are such that long periods of time elapse between interruptions. Troubleshooting this type of fault is time-consuming. The failure is difficult to reproduce.

The customer often prefers to continue system operation and postpone maintenance activity. The log out feature, by providing the customer engineer with system information at the time of the error, allows deferred maintenance.

When the system detects an error, the current microroutine is stopped and the machine branches to the log out routine. A number of logic-controlled cycles followed by a micro-routine transfers machine data into main storage. Programs are available to produce a printed copy of this information.

The log out data contains the information obtainable by analyzing a hardstop condition from the console. A full description of the log out feature is given in "Log Out."

# Maintenance Compatibility Among System/360 Models

Basic maintenance philosophy is the same for all models. Where possible, the maintenance features are identical. Obviously, all logic circuit-dependent features have to be related to the specific model.

Principal non-compatible features are fault-locating facilities and the log out format.

Principal compatible features are: maintenance of components (SLT, ROS, Storages), maintenance of I/O equipment, format of documents, diagnostic monitors, reliability test programs, and I/O diagnostics.

# **Fault Location Philosophy**

The system normally cannot tell which component is failing. Error detection and maintenance features built into the system, with back-up documentation and external diagnostics, give powerful assistance if properly interpreted.

The normal trouble-shooting procedure is:

- 1. CE call

- 2. Collect error information

- 3. Interpret error

- 4. Determine machine unit that failed

- 5. Reproduce error; find smallest possible error environment

- 6. Localize failure

- 7. Repair and check

- 8. Reports

#### **Documentation**

# Diagrams Manual (DM)

The following paragraphs explain the philosophy behind the compilation of the DM and instructions for its use.

#### System Data Flow Diggram

This shows over-all data flow of the 2040 and shows exits and entries to channels.

#### Unit Data and Control Diggram (UDCD)

This expands each unit contained within the system data flow diagram to include major controls.

## I/O Operations Diagram

This is a positive logic diagram showing the over-all function of 1/0 operations.

#### Simplified Logic Diagrams (SLD)

These are logic diagrams of those complex areas of the system where the ALD's might confuse.

# Condensed Logic Flow Chart (CLFC)

These show in condensed form the concept of a particular routine to facilitate reading of CAS Logic Diagrams (CLD's).

#### Malfunction Analysis Procedure Diagram (MAP's)

MAP's are designed to supplement customer engineering training and experience.

They provide a planned approach to malfunction environment in the field.

7

#### Over-all System MAP's

The over-all system MAP provides the initial key to the general fault-analysis problem. The problem is one of determining the failing unit (CPU, channel, or I/O) and subsequently the failing sub-unit (main storage, local storage, read only storage, ALU, multiplex or selector channel).

## **Detailed MAP's**

The system unit MAP's supplement the over-all system MAP's and are produced for these areas:

- 1. Early checks

- 2. Control checks

- 3. Late checks

- 4. Main storage

- 5. Local storage

- 6. Read only storage

- 7. ALU

- 8. Channels

- 9. Power

These diagrams direct the customer engineer to a particular ALD sheet or ECAD and describe the procedures in detail.

# **Other Support Documentation**

#### Machine Status Charts (MSC)

Certain microprograms are supported by machine status charts (MSC'S). These charts record the valid machine status of various latches and registers at the end of each specified microinstruction in single-cycle mode. MSC'S are provided for: hardware system reset, CPU check-out microprogram, dump/undump, selector channel checkout and initial program load microprogram (IPL).

Hardware system reset must be executed successfully before entering CPU checkout. Thus, hardware system-reset status provides a basic checking point in machine operation.

This can be displayed on the console panel by depressing the system-reset pushbutton in single-cycle mode and the operation checked with the hardware system-reset machine status chart. System-reset is immediately followed by the CPU check-out microprogram. (Press system reset in process mode.)

Machine status charts also contain, where applicable, diagnostic hints in the form of descriptive notes.

#### **Address Lists**

The address lists are contained in the CLD's and provide cross-reference lists for all ROS locations indicating:

- 1. ROS address

- 2. Control field punching

- 3. CLD location

- 4. EC number

- 5. Version

#### Automated Logic Diagrams (ALD's)

ALD's are computer-generated schematics representing machine functions. Circuits are shown as blocks which symbolize logical functions. They are connected by printed lines to show electrical connections; inputs enter the circuit on the left, outputs leave at the right.

#### CAS Logic Diagrams (CLD's)

CLD's are printed drawings representing the various micro-routines. The micro-instructions are shown as blocks connected to each other to indicate actual micro-instruction sequence.

## **Error Check Analysis Diagram (ECAD's)**

- ECAD's assist in error analysis by indicating the logic that produces the error condition.

- ECAD's allow the user to start from the error indicator and work backwards.

These diagrams show simplified logic of each checking circuit and the logic of all incoming paths as far back as the previous check. The information provided by the CPU check-out machine status charts should, in case of logic-detected errors, be sufficient to identify the failing path.

These diagrams are effective fault-locating documents, as they show the way from console indicators (or log out information) directly to the circuitry affected.

Note: These simplified logic diagrams are actual machine circuits; they are therefore Ec-level sensitive.

# Timing Chart (TC)

Timing charts are diagrams depicting the timing conditions of applicable operations.

# **ROS Control Field Chart**

These are charts for every ROS control field which indicate bit configuration; ROS mnemonic used on CLD's; and function performed by the field.

#### **External Diagnostics**

External diagnostics (machine language programs stored on cards, tape, etc.) are provided to check and verify system operation from the operating level covered by internal (microprogram) diagnostics, to the level where the system can safely be handed over to the customer.

These programs should be used in:

Initial installation check-out Unscheduled maintenance (trouble-shooting) Scheduled maintenance EC and RPO verification

Check-out of specific system components (I/O units) during customer operation.

Like all programs for System/360, the maintenance programs are designed to run under control of a monitor program. The diagnostic monitor (DM) takes care of all common housekeeping operations, handles interrupts, and provides the interface between the customer engineer and the system.

The actual maintenance programs (diagnostic sections) contain only program segments (diagnostic routines) which deal with actual tests and diagnostics and can run only under DM control.

If the system is unable to run a diagnostic monitor, special bring up programs are provided to build it up from the point of successful running of internal diagnostics to the level where a DM can operate properly.

The various levels of external diagnostics and the system debug order are:

Bring up monitors

Diagnostic sections which can be run under the bring up monitor

DMA8 (Diagnostic Monitor A8) Remainder of CPU sections under DMA8 Channel and I/O sections under DMA8 MIDAS system test, if available.

## Diagnostic Monitors (DM's)

The diagnostic monitor program has these functions:

- 1. Searching for the required diagnostic program (from tape, disk, etc.).

- 2. Allocation of storage and 1/0 units for its use.

- 3. Loading and relocation.

- 4. Translation of output messages generated by the diagnostic program into a form suitable for the output device in use.

- 5. Translation of a standard set of input messages into a form appropriate to the program in use.

- 6. Provision of input subroutines, such as entering certain information patterns into storage.

- 7. Buffering of output messages for most efficient use of the system.

- 8. Providing for overlapping the execution of one diagnostic program with the loading of the subsequent ones.

- 9. Handling all interruptions while diagnostic programs are being run.

- 10. Protection of each program from interference by other diagnostic programs and external influences.

- 11. Provision of sub-routines common to several programs.

The use of diagnostic monitor programs has these advantages:

- 1. The diagnostic programs may be written by independent design groups.

- 2. One diagnostic program may be used with any monitor program in an appropriate system.

- 3. The customer engineer does not have to use different loading techniques for the different programs.

- 4. It allows fault-finding to take place under conditions similar to those encountered while customers' programs are being run.

- 5. There are several diagnostic monitor programs to satisfy the variable conditions that can occur throughout the System/360.

The basic difference between DM's is their amount of operating features (or, the number of main-storage locations they may occupy). DM's are program compatible among the various System/360 models, provided that the configurations specified are met. (Main parameter is the core storage size.)

The standard monitor for a smaller model may be used as a bring up monitor for a large system.

On the IBM 2040 the following monitors are used:

- 1. Bring up monitor for 2040 (DM1)

- 2. DMA8 Standard Programs

- 3. DMK Emulator Programs

DM1: The bring up DM uses the half-word instructions debugged by the bring up programs. This monitor can be used to debug the instructions necessary to provide the DMA instruction set (small binary).

DMA8: DMA8 is designed for small systems having a minimum of 16K main storage. DMA8 requires 8K on a 16K machine and 12K on 32K, and higher, machines.

Any standard diagnostic section runs under DMA. All types of interrupts can be handled; interrupts expected by the sections are returned to it, unexpected interrupts cause error messages. Loading and printing are not overlapped with execution of the section.

DMA8 uses a full complement of input messages that are entered through the 1052. A limited number of messages may be entered through the console if a 1052 is not present.

DMA8 is a stand-alone monitor and can only be loaded by IPL.

9

# **Diagnostic Sections**

Four types of programs are available.

## Functional Tests (Reliability Tests)

These tests are used to verify the overall reliability of the system. They are used to discover whether a general system area is fault free.

The design of these tests provides thorough detection coverage, short running time and minimal size. These programs do not locate faults at circuit level. However, a sufficient variety of numerical examples is provided to permit manual check-out of the failing instruction.

#### **Circuit Level Tests**

These programs are used as fault-locating tools for particular system components. They make available extensive information about any failures that these programs discover. This information, when analyzed, is sufficient to determine a relatively small area of circuitry.

Tests in this group make extensive use of the diagnose instruction, and are valid only on the model for which they are designed.

#### **Measurement Tests**

This is a group of I/O programs designed to measure a specific parameter, such as the length of inter-record gaps, or to facilitate manual adjustments, such as mechanical clearances and linkages.

# **Check-Circuit Tests**

10

These tests are designed to use logic and program facilities to give a positive test of checking circuits.

# **System Failure Detection**

- Error detection by logic circuits.

- Error detection by microprogram.

- Error detection by internal diagnostics.

- Error detection by external diagnostics.

## **Error Detection by Logic Circuits**

Reference to the System Data Flow Diagram in the IBM System/360 Model 40, 2040 Processing Unit, Field Engineering Diagrams Manual, Form 223-2842, shows the comprehensive checking provided in the IBM 2040 for both data and control paths. Each check is individually indicated on the console panel or internal CE panel and, where applicable, an over-all check light is also provided (i.e., two-wire checks).

The CPU is comprehensively checked mainly by parity check circuits. All data transfers between regis-

ters and between registers and main storage are checked. Good parity is always written into main storage.

Parity checking is also used on the Read Only Storage (ROS), both at the address and at the output. In addition, the ROS decoder outputs are checked for validity.

The ALU function decoder is parity checked. Inside the ALU, signals are generated independently in true and complement form and checks are made to ensure that these signals are correctly propagated throughout this unit (ALU two-wire checking).

To reduce maintenance time, the individual error checks are on'ed in groups by timing and function, into three over-all check latches: the control check latch, early check latch and late check latch. These over-all check latches are separately indicated.

The outputs of the three over-all check latches are on'ed together to produce the signal, Error Will Stop Clock, which stops the T clock on completion of the machine cycle in which the error was detected and raises several inhibit lines.

If the failure results in a control or early check, the nos inhibit line will be raised early enough in the cycle to prevent any change of the nos sense latch settings. The purpose of these inhibit lines is prevention of the loss of valuable diagnostic data.

The OR of the three over-all check latches is also used to set the master check latch.

#### **Error Detection by Microprogram**

Some machine errors are detected by the microprogram: in the CPU, by invalid branches of the microprogram to unused locations (the TROS tapes at these locations contain the function LOG); in the channels, by time out conditions on the interface signal-sequence. The microprogram sets the interface control check, which, in turn, causes the same sequence as an error detected by logic checks.

In all microprogram routines, various tests for programming errors and exceptional conditions are made. Included are tests for valid op code, valid specification of operands, storage protect violation, invalid addresses, and valid data. Arithmetic operations test for unusual conditions such as overflow and divide exceptions.

Detection of any of these conditions leads to a program check interrupt rather than to a possible machine check, greatly reducing the number of program or machine problems.

Errors detected by microprogram in the CPU raise one of these signals:

Start Log Out Stop T Clock

#### Start Log Out

A microprogram-generated control signal, log (cb = 2; cb = 3), is provided to give the signal, Start Log Out. log is used in all invalid microprogram words to give a log out, showing that an unused word has been addressed or an invalid branch taken.

Invalid branches also contain, as next address, the address of the branch that probably should have been taken. This allows the machine to continue processing the original instruction if it is in error disable mode.

When the signal, Start Log Out, is given in error disable mode, it is latched up as a control check and results in a log out when the machine is enabled.

#### Stop T Clock

A microprogram-generated control signal, Stop (CB = 5; CD = 3), is provided to give the signal, Stop T Clock. It is used only in diagnostic microprograms and results in a machine hardstop provided that errors are enabled. The signal is also or ed into the early check latch to make possible check restart during the CPU checkout diagnostic microprogram.

# **Error Detection by Internal Diagnostics**

Most of the circuits that are not continuously monitored by logic checking are periodically checked by the CPU check-out routine. This routine, of approximately 75 microinstructions, is executed when system power is brought up and every time initial program load or system reset on the console is pressed.

In addition, the check-out is performed during the machine check interrupt sequence and can be looped for trouble-shooting purposes.

Other diagnostic microroutines are built into the system to provide an easy way of checking some circuits. Routines included are:

Main storage worst pattern test Main storage addressing test Local storage worst pattern test Local storage addressing test Dump test

These tests are not executed automatically but are controlled from the console.

# **Error Detection by External Diagnostics**

These are detected by running maintenance programs. The programs, when run under diagnostic monitors, upon detection of an error, print out expected and actual results. The context of these results is program-dependent (it may represent a PSW, CSW, etc.). This may be determined from the diagnostic section write up or listing.

# **System Handling of Errors**

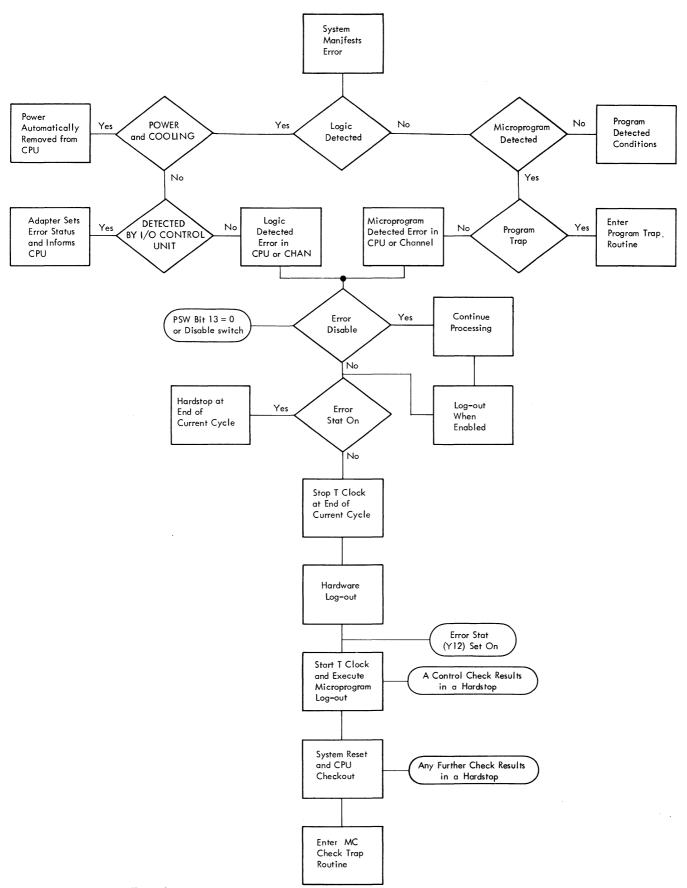

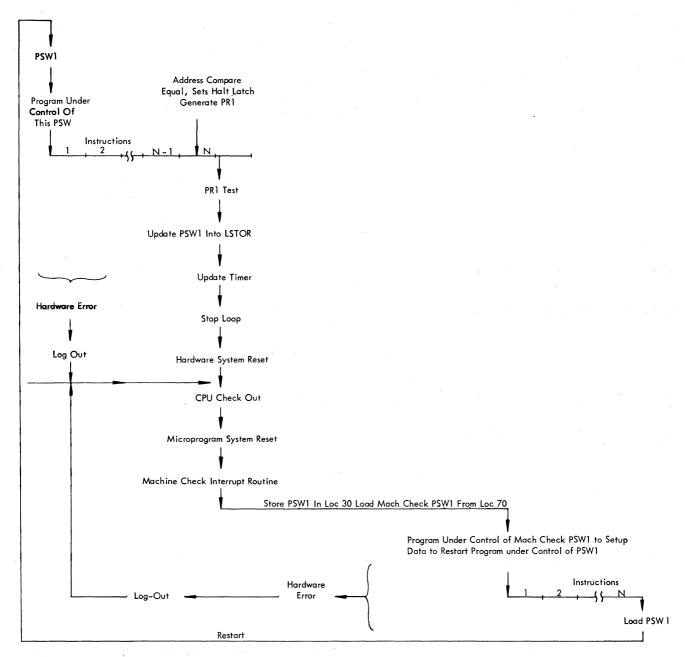

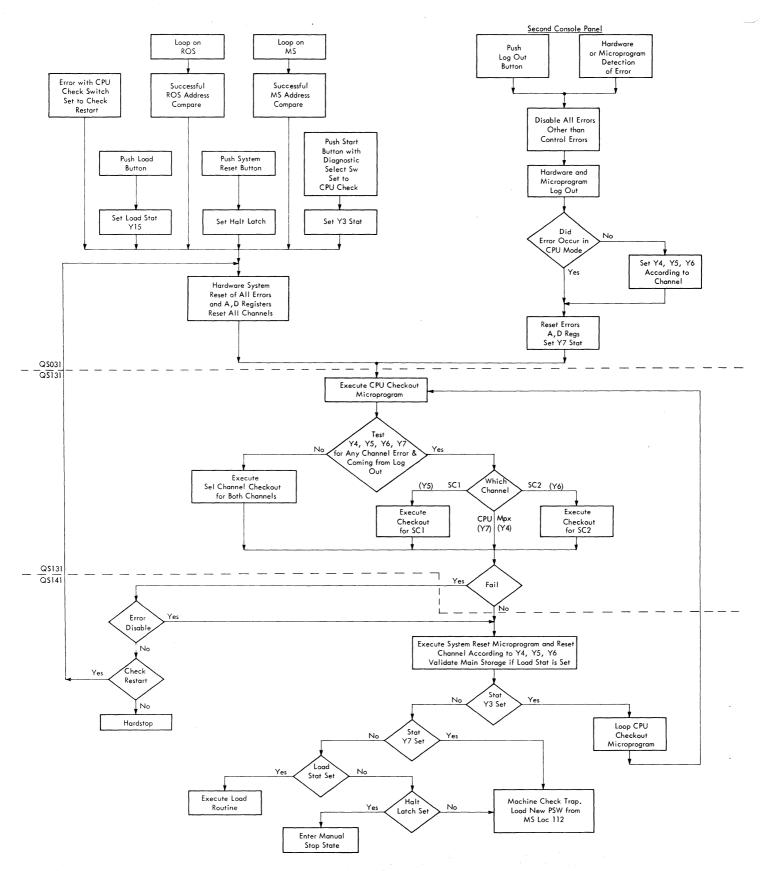

The sequence of events following the detection of an error is illustrated in Figure 1.

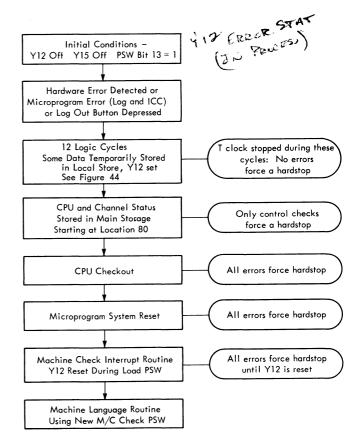

If the machine is in normal processing mode, the detection of an error stops the T clock at the end of the machine cycle in which the error is detected. Hardware and microprogram log out takes place, CPU check-out and system reset is executed, and finally the current PSW is replaced by the machine check program status word (PSW).

The program, normally the operating system supervisor, then determines the next action to be taken. Errors detected during CPU check-out, system reset, store and load PSW, bring the system into hardstop.

Log out and machine check interrupt can be disabled (console switch or PSW Bit 13 = 0). Errors are still detected and latched up until the machine is again enabled.

## **Error Stat**

The error stat is set by circuitry at the beginning of a log out. It is also set by system reset.

When the error stat is set, all dumps are inhibited and any subsequent errors result in a machine hardstop.

Reset is by microprogram.

#### **Error Resetting**

The following methods of error resetting are provided: System Reset can be initiated by a pushbutton from the console panel or forced by hardware. It resets all errors and returns the CPU and channels to their initial state.

Check Reset is controlled by a pushbutton on the console panel. It resets all check latches, but these latches may be set again by the error data on removal of the reset signal.

Reset Errors is a microprogram-generated control signal CR = 6 and Manual Stat (Y10). As it is active only with the T clock running, it is used only in error disable mode. It resets all check latches.

Other reset signals derived from the above are:

- 1. Error Reset = System Reset Latch or Check Reset or Reset Errors.

- 2. Reset Check Latches = Error Reset or Log Out Start T.

#### **Other Error Conditions**

The error-checking facilities described so far detail the possibilities for detecting system malfunctions before handling the system over to the customer. The ultimate tests are the correct answers of the customer's machine-language programs.

Figure 1. System Handling of Errors

The user's definition of error detection covers only those machine malfunctions which are indicated during execution of his jobs. In the 2040 CPU the checks provided are the hardware checks, micro-program checks and to a certain extent, the CPU check-out routine. These tests cannot give a full coverage of all malfunction possibilities; however, this error detection system is much more powerful in a Ros-controlled machine than in previous machine types, since parity checking not only affects the flow of data through the system but all handling of control information and the control itself.

Customer engineers should be aware of the following machine malfunctions which may occur. (Over-all checking philosophy deals only with single errors):

- 1. Parity checking discovers only single errors: i.e., dropping or picking of an even number of bits cannot be detected. This may be of special importance for the Ros output where there is one parity bit for 53 data bits.

- 2. There is limited checking of check circuits.

- 3. Microprogram B and C branch conditions are checked only by CPU check-out.

- 4. Invalid microprogram branches are detected only if the branch address is unused and contains the Log instructions.

- 5. The CPU check-out tests only basic circuit operations and has no provision for various data and operation patterns.

- 6. Storage protect compare circuits are not checked.

# **Diagnose Instruction**

The diagnose instruction:

- 1. Has the Rs format.

- 2. Provides access to any micro-instruction and to certain machine functions for diagnostic purposes.

- 3. R1 and R3 fields specify the setting of stats YA and YB.

- 4. B2 and D2 fields specify a ROS address where a diagnose function is to be performed, and the condition of the CPU, ISA, OT PSA.

- 5. Is operative only in supervisor state.

#### Utilization

The diagnose instruction is a tool for the diagnostic programmer, allowing him to enter the microprogram at any step he desires with the data he chooses. The customer engineer must understand thoroughly the microroutine he intends to enter before attempting to use diagnose. Diagnose is helpful on system faults that do not fail in single cycle mode. If the failure can be narrowed to a few micro-instructions, a scoping loop

can be set up. Since the instruction is a programming tool, there is no mnemonic.

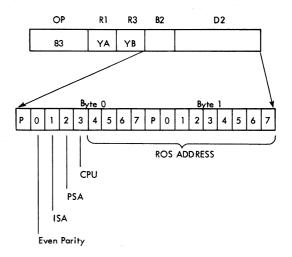

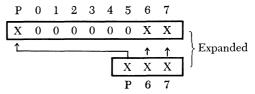

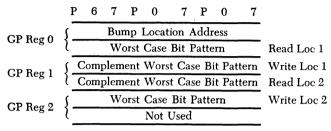

The Ros address entry is determined by the setting of the B2-D2 fields of the instruction. The B2 field must be used to accommodate the setting of ISA, PSA or CPU state bits. Setting of the B2-D2 fields require two bytes of data entered from the console switches. Byte 0 contains ISA, PSA, CPU, even parity bit and the high order hex digit of the Ros address.

Byte 1 switches enter the remaining two hex digits of the ROS address. Byte 1 is entered automatically with odd parity; this parity controls the parity of the entire ROS address.

Even parity is forced for the high order hex digit of the ROS address in byte 0. The bit position labeled even parity (Figure 2), is used to control odd parity for the ISA, PSA, or CPU bits; i.e., if these three bits are all off, the even parity bit must be entered.

Figure 2. Console Entry for Diagnose Instruction

The stat setting needed when entering a Ros address is forced by making R1-R3 equal to the YA-YB stats. When the diagnose instruction is executed, stats YA-YB are set and the desired Ros address is forced.

Unless the machine is set to stop on nos in the selected microprogram, it takes an incorrect branch, loops or traps, and the next I fetch is executed. For scoping loops this could be a branch back to the diagnose instruction.

To supply data for the ROS operations, the undump routine in the machine can be used. The dump area of local storage must be set up before the diagnose instruction is executed. An undump can be forced by addressing the ROS address of the undump routine used for multiplex operations. Setting ROAR section of the dump area provides an entry to another ROS address at the completion of undump. Resetting the

dump area after looping (it is empty after use) is also handled by diagnose.

The following program enables an entry at any desired microprogram step by manually setting a main storage area first with the data flow bytes required. Once the program is initiated, these bytes are set in the dump area as in a diagnose instruction.

A separate diagnose instruction is issued to initiate an undump routine and start the suspect microprogram routine at the required step. If the routine comes to a successful conclusion and takes the next sequential instruction, it restarts the loading of the dump area again. This also occurs if the machine check new PSW is ever used (initiated by an error, or loop on Ros), or an external interrupt occurs (from the interrupt key).

The program can be punched into four cards and loaded by the IPL routine.

## **Operating Instructions**

- 1. Disable the interval timer (if the feature is installed) by using the console key (panel C).

- 2. Press IPL this feeds all four cards and the machine goes into the wait state.

- 3. Switch storage select switch to IC and press the stop key — this should show that bits 4-7 of byte 0 of the storage data register have a hex value of 7.

- 4. Switch storage select switch to Ms and load address 5000 to 501B as shown in the following chart.

This is the dataflow storage area used by the program for data to be used on entry at the required microprogram step:

| HEX MS LOC         |          |               | HEX I | ATA  |      |

|--------------------|----------|---------------|-------|------|------|

| First Card (Col. 1 | 1-24)    |               |       |      |      |

| 0000               | 00       | 00            | 0000  | 0000 | 5040 |

| 0008               | 02       | 00            | 5028  | 4000 | 0050 |

| 0010               | 02       | 00            | 0048  | 0000 | 0050 |

| Second Card (Co    | l. 1-64) |               |       |      |      |

| 5028               | 80       | 06            | 0000  | 0600 | 5054 |

| 5030               | 01       | 00            | 0000  |      |      |

| 5034               | 00       | 00            | 0004  |      |      |

| 5038               | 01       | 06            | 0000  | 0700 | 0000 |

| 5040               | 48       | $\mathbf{F0}$ | 0052  |      |      |

| 5044               | 41       | $\mathbf{D}0$ | F200  |      |      |

| 5048               | 40       | D0            | 0052  |      |      |

| 504C               | 9C       | 00            | 00XX* |      |      |

| 5050               | 82       | 00            | F028  |      |      |

| 5054               | 91       | 04            | 0044  |      |      |

| 5058               | 47       | EO            | F050  |      |      |

| 505C               | 58       | 10            | F030  |      |      |

| 5060               | 58       | 30            | F034  |      |      |

| 5064               | 82       | 00            | F038  |      |      |

| Third Card (Col.   | . 1-56)  |               |       |      |      |

| 0048               | 00       | 00            | 0050  |      |      |

| 004C               | 00       | 00            | 0000  |      |      |

| 0050               | 02       | 00            | 5000  | 0000 | 0050 |

| 0058               | 01       | 04            | 0000  | 0100 | 5200 |

| *Input unit addre  | ess      |               |       |      |      |

| HEX MS<br>ADDRESS | вуте 0        | вути       | : <b>1</b> |

|-------------------|---------------|------------|------------|

| 5000              | Blank         |            | YC         |

| 5002              | YA YB         | CPU tag    | Skew Reg   |

| 5004              | Blank         | Blank      | AX         |

| 5006              | <b>A0</b>     | A)         |            |

| 5008              | Blank         | Bla        | nk         |

| 500A              | $\mathbf{D0}$ | D:         |            |

| .500 <b>C</b>     | Blank         | Blan       | nk         |

| 500E              | В0            | B          |            |

| 5010              | Blank         | Blank      | CX         |

| 5012              | C0            | C          |            |

| 5014              | Blank         | Blan       | nk         |

| 5016              | H             | J          |            |

| 5018              | Blank         | Blan       | nk         |

| 501A              |               | ROAR<br>7- |            |

|                   |               |            |            |

Note: The blank areas are used only to simplify loading a general purpose register before the storageto-storage transfer into the dump area.

Byte 501A contains the stored stats used in dump/ undump. The parity bit of byte 1 gives odd parity of ROAR bits 0-7. The parity bit of byte 0 gives even parity of ROAR bits 8-11. Bit 0 should be used to make odd parity of bits 0-3. Therefore, if ISA, PSA and CPU are all off, the even parity bit (bit 0) must be on to maintain good over-all parity (see byte configuration, Figure 2).

- 5. When the loading of the data flow storage area is completed, set up the storage data keys for the loop on Ros address as required. Switch to loop on Ros.

- 6. Press start to return the machine to the wait loop, then press the interrupt key to initiate the program operation.

- 7. Set CPU check switch to process or disable to avoid stopping on errors.

The program loads to:

#### DESCRIPTION

| 1st PSW used                                       |

|----------------------------------------------------|

| 1st CCW — read 80 bytes from 2nd card              |

| 2nd CCW — read 80 bytes from 3rd card              |

| 2nd CCW = read 60 bytes from 5rd card              |

|                                                    |

| Wait PSW - enabled for Mpx interrupts              |

| Update LSAR constant                               |

| Update MS constant                                 |

| Wait PSW — enabled for external interrupts         |

| Load base reg F                                    |

| Load main program address to reg D                 |

| Store reg D in CCW                                 |

| Start I/O CCW used in 0050                         |

|                                                    |

| Load wait PSW. Enabled for Mpx interrupt           |

| Check CSW for device end without errors            |

| Return to wait state if condition is not satisfied |

| Set up GP reg 1 for later use                      |

| Set up GP reg 3 for later use                      |

| Load wait PSW enabled for external interrupts      |

|                                                    |

|                                                    |

| CAW                                                |

| Not used                                           |

| CCW – data address later modified                  |

| External new PSW                                   |

External new PSW

| HEX MS LOC        |       |               | HEX I | DATA |      | DESCRIPTION                                                     |

|-------------------|-------|---------------|-------|------|------|-----------------------------------------------------------------|

| 0060              | 01    | 02            | 0000  | 0200 | 0000 | Supervisor call new PSW                                         |

| 0068              | 01    | 02            | 0000  | 0300 | 0000 | Program check new PSW                                           |

| 0070              | 01    | 04            | 0000  | 0400 | 5200 | Machine new PSW                                                 |

| 0078              | 01    | 04            | 0000  | 0500 | 5054 | I/O new PSW                                                     |

| Fourth Card (Col. | 1-48) |               |       |      |      |                                                                 |

| 5200              | 48    | 50            | F226  |      |      | Load reg 5 with diagnose constant                               |

| 5204              | 18    | $\mathbf{EF}$ |       |      |      | Load reg E with base address                                    |

| 5206              | 58    | 40            | F228  |      |      | Load reg 4 with count (to load dump area 49-4F)                 |

| 520A              | 58    | 00            | F22C  |      |      | Set up reg 0 with LSAR address of undump area                   |

| 520E              | 58    | 20            | E000  |      |      | Load reg 2 from data flow area                                  |

| 5212              | 83    | 01            | 5157  |      |      | Diagnose instruction to initiate main storage to LSTOR transfer |

| 5216              | 1A    | 01            |       |      |      | Update LSAR address of undump area                              |

| 5218              | 1A.   | <b>E3</b>     |       |      |      | Update MS address of data flow area                             |

| 521A              | 46    | 40            | F20E  |      |      | Branch back unless reg 4 is zero                                |

| 521E              | 83    | 00            | 500B  |      |      | Diagnose instruction into suspect routine (undump and process)  |

| <b>5222</b> .     | 47    | F0            | F200  |      |      | Unconditional branch back to loop                               |