# **DIAGNOSTICS**

# ADDENDUM DIAGNOSTIC MANUAL

The attached pages are new or replacement pages effective April 01, 1981.

#### DIAGNOSTIC DEPARTMENT

#### September 15, 1981

#### PRODUCT ENHANCEMENTS

FIXTST15 OP-1/15 Fix Data Switch Test (5300-1103-XX).

MINI96 96 TPI Mini-diskette Subsystem Test (5000-11118-2).

RAMSW15 OP-1/15 RAM/ROM Switch Test (5300-1109-X).

SERPR15 OP-1/15 Serial Printer Adapter (5300-1119-X).

R3750 Attribute Overlay for OP-1/RW (508-3750-004).

KBDTSTP5 OP-1/15 Phillips Keyboard Test.

KBDTSTKT OP-1/15 Keytronics Keyboard Test.

KBDP386 Tests Keyboards with PCO 386.

W3430 Attribute Overlay for WETTST (508-3430-002).

#### CORRECTED PRODUCT DEFICIENCIES

ASCTST Revised to run with PCO 199. (CRAB #70)

BSC2 Timing changed to run on OP-1/15.

DSKSTP3 Commands added to exercise Bad Track Latch Reset and Bad Track Format. (CRAB #66)

IOTST4 Revised to check 4 high order interrupt bits on OP-1/R when PCO 338 is implemented. (CRAB #60)

PDCIFL Revised to test 96 TPI Tandon mini drives.

RTCTST4 Revised to check 4 high order interrupt bits on OP-1/R when PCO 338 is implemented. (CRAB #60)

WRDTST Clear Screen command fixed. (CRAB #71)

#### OUTSTANDING COMPLAINTS

#### PAR #

- 394 Add test to check DTR with PCO 350.

- 396 Intermittant failures in AIOTST4, tests 3B,3C when run on OP-1/R with Sync Adapter.

- 397 Need Character Generator Fonts for visual observation in WETTST.

- 398 Need test to force and check for parity error.

- 401 Add select address test to AIOTST4.

#### OUTSTANDING COMPLAINTS

| CRAB | # | PROGRAM NAME   | BUG                                                  |

|------|---|----------------|------------------------------------------------------|

| 51   |   | IOTSTM         | Does not check DTR line                              |

| 61   |   | WETTST/RTEST   | Does not test PCO 352                                |

| 62   |   | AIOTST4        | Fails when used with sync adapter                    |

| 63   |   | VIDTST4/WETTST | Need character generator listings to compare to test |

| 65   |   | DSKTST         | Need test to force parity error                      |

#### PRODUCT DEFICIENCIES

None.

# ADDENDUM DIAGNOSTIC MANUAL SECTION I

The attached pages are new or updated pages effective April 01, 1981

## **DIAGNOSTICS**

## SECTION 1

# 09/15/81

## TABLE OF CONTENTS

| SECTION | PROGRAM<br>NAME    | TITLE                                              | DATE     |

|---------|--------------------|----------------------------------------------------|----------|

| 3       | DIATST             | Diablo Printer Test                                | 10/31/80 |

| 4C      | RAMCOM             | Multi-Algorithm Memory Test                        | 11/01/78 |

| 4E      | PARRAM             | Multi-Algorithm Memory Test with Parity Check      | 02/24/81 |

| 5       | PRNTST             | Centronics Printer Test                            | 12/02/80 |

| 5A      | PRNEX              | Centronics/Okidata/Printronix<br>Printer Exerciser | 02/15/78 |

| 6       | DSTTST             | Diskette Controller Test                           | 11/30/79 |

| 8A      | BSC2               | Binary Synchronous II Controller Test              | 10/31/80 |

| 10A     | SYN2               | Synchronous II Controller Test                     | 03/26/81 |

| 13      | WRDTST/<br>WRD210  | Word Mover Controller Test                         | 12/15/80 |

| 16      | ASCTST             | Asynchronous Controller Test                       | 12/15/80 |

| 17      | IOMTST/<br>WIOMTST | Input/Output Microprocessor Test                   | 04/15/78 |

| 18      | DSKTST             | Disk System Test                                   | 11/30/79 |

| 18A     | DISKEX             | Hard Disk Exerciser                                | 03/15/79 |

| 21      | KBDTST             | Universal Keyboard Test                            | 09/15/81 |

| 22      | WETTST             | Word & ETED Display Test                           | 09/15/81 |

| 23      | TROUBLE            | Universal Troubleshooting Tool                     | 03/15/79 |

# DIAGNOSTIC MANUAL (SECTION I)

September 15, 1981

# Supplement Filing Instructions

| Section I            | Remove     | Insert (total pages)                              | Description          |

|----------------------|------------|---------------------------------------------------|----------------------|

| Table of<br>Contents | April 1981 | September 1981 (2)                                | Table of<br>Contents |

| 21                   | 21-6       | 21-6 (1)                                          | KBDTST               |

| 22                   | None       | 22-10; 22-11 (2)                                  | WETTST               |

| 29A                  | None       | Cover Sheet; 29A-1 to 29A-6 (7)                   | MINI96               |

| 39                   | 39-1       | 39-1 (1)                                          | PDCIFL               |

| 42                   | None       | Cover Sheet; 42-1 to 42-3 (4)                     | RAMSW15              |

| 43                   | None       | Cover Sheet; 43-1 to 43-4; Figure 1; Figure 2 (7) | SERPR15              |

Note: These instructions should be inserted at the beginning of the DIAGNOSTIC Manual.

| SECTION | PROGRAM<br>NAME | TITLE                                                 | DATE     |

|---------|-----------------|-------------------------------------------------------|----------|

| 29      | MINTST          | Mini-Diskette Subsystem Test                          | 01/15/80 |

| 29A     | MINI96          | Mini-Diskette Subsystem Test (96 TPI)                 | 09/15/81 |

| 37      | MPDCTST         | Micro-Programmable Diskette<br>Controller Test        | 07/15/80 |

| 39      | PDCIFL          | Sub-Assembly Programmable Diskette<br>Controller Test | 09/15/81 |

| 40      | DSPSW           | OP-1/15 Display Switch Test                           | 02/24/81 |

| 41      | LFI15           | OP-1/15 Line Frequency Interrupt Test                 | 03/23/81 |

| 42      | RAMSW15         | OP-1/15 RAM/ROM Switch Test                           | 09/15/81 |

| 43      | SERPR15         | OP-1/15 Serial Printer Adaptor Test                   | 09/15/81 |

,

1

# ADDENDUM DIAGNOSTIC MANUAL SECTION II

The attached pages are new or updated pages effective April 01, 1981

# DIAGNOSTICS 4K

# SECTION II

09/15/81

# TABLE OF CONTENTS

| SECTION | PROGRAM<br>NAME                            | TITLE                                    | DATE     |

|---------|--------------------------------------------|------------------------------------------|----------|

| 1       | VIDTST4                                    | 4K Display Microprocessor Test           | 02/24/81 |

| 2       | RTCTST4                                    | Real Time Clock Test                     | 09/15/81 |

| 3       | FIXTST4/<br>FIXTST15                       | Fixed Data Switch Test                   | 09/15/81 |

| 5       | PRNTST4                                    | Printer Adapter Test                     | 12/02/80 |

| 6       | IOTST4/IOTSTM<br>IOTST15/IOT2WM<br>IOT2W15 | Asynchronous I/O Adapter Test            | 09/15/81 |

| 7       | AIOTST4                                    | Alternate I/O Adapter Test               | 03/11/81 |

| 8       | SIOTST4                                    | Synchronous I/O Adapter Test for OP-1/RS | 12/02/80 |

# DIAGNOSTIC 4K MANUAL (SECTION II)

September 15, 1981

## Supplement Filing Instructions

| Section II           | Remove     | Insert (total pages) | Description          |

|----------------------|------------|----------------------|----------------------|

| Table of<br>Contents | April 1981 | September 1981 (2)   | Table of<br>Contents |

| 2                    | 2-1        | 2-1 (1)              | RTCTST4              |

| 3                    | 3-1; 3-4   | 3-1; 3-4 (2)         | FIXTST4/FIXTST15     |

| 6                    | 6-1 to 6-3 | 6-1 to 6-3           | IOTST4               |

Note: These instructions should be inserted at the beginning of the DIAGNOSTIC 4K Manual.

## BOOTSTRAPS

## SECTION III

# 10/31/80

# TABLE OF CONTENTS

| SECTION | PROGRAM<br>NAME | TITLE                            | DATE     |

|---------|-----------------|----------------------------------|----------|

| 1       | SPR8BOOT        | Bootstrap loader for 8080 SUPER8 | 10/31/80 |

| 2       | EIGHTWAY/TENWAY | Multiflavor Self Test Boot       | 10/31/80 |

| 3       | SPDPBT          | MDOS SP/DP Self Test Boot        | 10/31/80 |

## **APPENDICES**

# 04/01/81

| SECTION | PROGRAM<br>NAME | TITLE                                                                    | DATE       |

|---------|-----------------|--------------------------------------------------------------------------|------------|

| Α       | Appendix A      | Run Modification Feature                                                 | 06/15/77   |

| В       | Appendix B      | 4K Format Test Module Run Options/<br>Loading the 4K Diagnostic Programs | _ 09/01/78 |

| С       | Appendix C      | RUN, RUNSS, RUNXP                                                        | 10/31/80   |

| D       | Appendix D      | SEND                                                                     | 10/31/80   |

| E       | Appendix E      | SENDS                                                                    | 10/31/80   |

| F       | Appendix F      | Limited Distribution                                                     | 10/31/80   |

| G       | Appendix G      | Archived Diagnostics                                                     | 07/15/80   |

| Н       | Appendix H      | (A)synchronous or (S)ynchronous                                          | 10/31/80   |

|         | Addendum        |                                                                          |            |

# DIATST DIABLO PRINTER TEST

#### DIATST - DIABLO PRINTER TEST PROGRAM

#### Applicable Assemblies

| 5000-1127-X | Byte String Controller Board | (X=1-4) |

|-------------|------------------------------|---------|

| 5000-1136-1 | Character Printer Board      |         |

5000-1170-1 Word Mover Controller Board

#### General Description

The purpose of the DIATST program is to determine if the Diablo Printer, the Character Printer board and the print portion of the Byte String Controller or Word Mover Controller are working properly and, if not, to give an indication of which print functions are incorrect. The program requires assistance from the operator to perform certain actions and analyze the PRINTOUT (See Figure 1) at the end of the last test.

16K of memory is required to run DIATST.

This manual applies only to the 8080 version of DIATST.

#### Loading Procedure

DIATST can be loaded into memory using any conveniently available loading method. It is a completely self-contained program. If DIATST loads properly, it will identify itself and wait for operator action.

#### **Operator Action**

At the end of the wait period, DIATST needs to know if there is an Asynchronous or Synchronous adapter. Respond by typing an (A) for Asynchronous or (S) for Synchronous adapter.

DIATST will then ask for the serial number of the printer being tested. Enter the serial number and type a carriage return or to bypass it completely, just type a carriage return.

All tests including Test 01 operate automatically. Test 01 displays a message on the screen requesting the operator to perform a certain task. The operator indicates compliance by typing the SPACE bar after performing the requested task. When the space code is sensed DIATST continues to the next part of Test 01 or to the next test.

When the entire test has been completed, the prompt "Type Space to Repeat DIATST" will be displayed. If a space is typed on the keyboard, DIATST will restart.

#### **Errors**

All program detectable errors are indicated by an appropriate error message on the screen and the simultaneous activation of the bell. The bell will ring only to notify the operator of an error. The error message on the screen attempts to give a description of the nature of the problem. In most cases, this message should be adequate in diagnosing the problem. Otherwise, refer to the detailed description of each test to determine the purpose and results for the displayed error message.

After an error message is displayed, the operator has three ways to proceed. Typing the SPACE bar will continue testing on the next test, typing the R key (without the SHIFT key) will repeat the current test and depressing PROG will restart the program.

Even if DIATST proceeds from Test 00 to Test 16 without a displayed error, there could still be a printed error, since DIATST has no way to examine the characters printed or to ascertain if paper movement commands are functioning properly. After the final test the operator must compare the printout produced by the tests to the correct PRINTOUT in Figure 1.

#### Test Description

All test operations are described in this section. The program will halt and the specified error message will be displayed if expected results are not obtained.

On the following pages, each test is listed with a brief description of what it is testing for on the top of each page. Below the description, all possible error messages are listed, with an explanation of the cause of the message. However, in addition to the specified messages, other messages may be displayed. These messages are general to all the tests and are listed below:

#### PLEASE MAKE PRINTER READY

This condition could be caused by improper data cable hook-up, lack of ribbon in printer, lack of power to printer, lack of printer controller board in OP-1, lack of paper (optional), cover open (optional) or printer carriage motion impeded by the left or right hard stops or by a foreign object.

A restore command may be issued from the keyboard by typing a shifted prog. This will make the printer ready if the not ready condition was caused by the carriage exceeding the left or right margins.

After righting the cause of the not ready condition, type space to continue.

TEST 00 Test that the print portion of the Byte String Controller does not respond to incorrect select address, does respond to correct select address and INIT de-selects a selected Byte String Controller.

#### CONTROLLER SELECTED WITH WRONG ADDRESS (XX)

IFL to one of the addresses 034, 0B0, 094 or 0A4 gave a result other than OFF (open bus). XX is the incorrect select address.

#### CONTROLLER IS NOT SELECTED WITH CORRECT ADDRESS (B4)

IFL to the correct Byte String Controller addresss(OB4) gave a result of OFF (open bus).

#### INIT DOES NOT DESELECT CONTROLLER

After an INIT to the selected Byte String Controler, IFL did not get a result of OFF (open bus).

TEST 01 Tests that NOT READY bit from Printer can be read by software.

#### NOT READY FLAG LOOKS READY

NOT READY bit low as if printer is powered up, instead of being powered down and/or disconnected from the OP-1.

#### NOT READY FLAG LOOKS NOT READY

NOT READY bit high as if printer is not connected, or in a fault condition.

TEST 02 Tests whether Controller NOT BUSY bit (IFL bit 7) is set when DVCL and INIT commands are issued.

Expected IFL Status: 080

Multiple ERROR messages as below are possible.

#### IFL BIT 7 NG NOT BUSY FLAG

NOT BUSY FLAG low when it should be high.

IFL BIT 1 NG NOT READY

NOT READY FLAG high when it should be low.

IFL BIT 0 NG PRINTER BUSY

PRINTER BUSY FLAG high when it should be low.

TEST 03 Test that COM2 and COM3 do not cause the printer to activate.

A simple move is executed by issuing a COM2 (Byte String Controller) and a COM3 (Byte String and Word Mover Controller). If either of these caused the printer busy line to go busy the test will fail.

(C.

COM2 CAUSES PRINTER BUSY TO GO ACTIVE.

COM3 CAUSES PRINTER BUSY TO GO ACTIVE.

Tests if NOT BUSY bit (IFL bit 7) is set by a DVCL and INIT cleared for the duration of a print command (COM1) and is set upon completion of printing; also, test if PRINTER BUSY bit (IFL bit 0) is reset before a print command and is set during execution of the print command. In addition, test if locations PCAH (0823) and PCAL (0822) are initialized to the contents of PSAH (0821) and PSAL (0820) by a print command and eventually increment till they equal PTAH (0825) and PTAL (0824) upon print completion.

NOT BUSY IS NOT SET BY DVCL AND INIT

After a DVCL and INIT, IFL bit 7 was low when it should be high.

PRINTER BUSY IS SET BEFORE PRINT COMMAND ISSUED

Before a print command, IFL bit 0 washigh when it should be low.

CONTROLLER BUSY FLAG DOES NOT LOOK BUSY DURING A PRINT

After a print command, IFL bit 7 was high when it should be low.

PRINTER BUSY FLAG DOES NOT LOOK BUSY DURING A PRINT

After a print command, IFL bit 0 was low when it should be high.

CURRENT ADDRESS NOT INITIALIZED PROPERLY

After a print command, PCAH and PCAL were not loaded to the address in PSAH and PSAL.

#### CONTROLLER NOT BUSY FLAG STAYS BUSY TOO LONG

After about one second, IFL bit 7 is still low when it should be high.

#### CURRENT ADDRESS DID NOT STOP AT CORRECT ADDRESS

After the print command is finished, PCAH and PCAL are not equal to PTAH and PTAL.

TEST 05

Tests that locations PCAH and PCAL increment until they point to a character matching the character in PTC if PTAH bit 7 is low, but increment until they equal PTAH and PTAL if PTAH bit 7 is high.

#### PRINT DID NOT STOP AT TERMINATING CHARACTER

During a print command with PTAH bit 7 low, PCAH and PCAL incorrectly incremented past a character that matches the character in PTC.

#### PRINT DID NOT STOP AT TERMINATING ADDRESS

During a print command with PTAH bit 7 high, PCAH and PCAL did not increment up to PTAH and PTAL.

TEST 06 Tests for check mechanism fault from extended carriage movement in either direction.

#### NOT READY FLAG LOOKS READY

After issuing either of the print commands predetermined to cause a fault, the NOT READY bit did not go high.

TEST 07 Tests if the RESTORE command functions properly.

#### RESTORE COMMAND DID NOT RETURN CARRIAGE COMPLETELY

After issuing a restore command, an attempt is made to print a line requiring the full platen width (13.20 inches). However, printing was aborted and the NOT READY bit went high, presumably because the carriage hit against the right hard stop.

TEST 08 Tests if during print functions, the PRINTER BUSY signal holds off data transfer from the printer controller.

#### PRINTER BUSY SIGNAL DOES NOT HOLD OFF DATA TRANSFER

During a print command, PCAH and PCAL continuously incremented, with no hold off pause, until they reached PTAH and PTAL.

TEST 09 Tests all horizontal carriage movement bits.

#### BIT X IS NOT FUNCTIONING PROPERLY

A horizontal carriage movement bit was not moving its appropriate distance: 2 raised to the power of bit X (X represents the bit number from 0 to 9).

This test is performed by moving the carriage a total of 13.2 inches (792 increments). The carriage is moved the maximum number of times its appropriate distance is a divisor of 792 increments. The remainder of the 13.2 inches is comprised of one movement using the bits already verified. After this the NOT READY bit must go from low to high when the carriage is extended one sixth of an inch to the right, since it should hit the right hard stop causing a fault.

TEST 10 Visual test of vertical paper movement bits.

No possible error messages, refer to Figure 1 for verification.

TEST 11 Tests if the fast move bit causes carriage movement and printing to speed up by more than 25 percent.

#### FAST MOVE IS TOO SLOW

The speed of carriage movement in conjunction with printing was not increased sufficiently by setting the fast move bit.

TEST 12 Visual test of forward and backward carriage movement, and the printability of all capital letters on print wheel.

The message "THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS" is printed twice.

No possible error messages, refer to Figure 1 for verification.

#### TEST 13

Test the half space capability of increasing every carriage movement by 1/120th of an inch.

#### HALF SPACING IS NOT FUNCTIONING PROPERLY

A print line of many small movements is calculated to cause a total carriage move of 11.33 inches. The half spacing capability should increase the total movement of the print line to 13.2 inches. After this the NOT READY bit must go from low to high when the carriage is extended one sixth of an inch to the right, since it should hit the right hard stop causing a fault.

#### TEST 14

Visual test of ribbon dropping capability.

On single color ribbons the second line should appear lighter. On dual color ribbons the two lines should differ in color.

No possible error messages, refer to Figure 1 for verification.

#### TEST 15

Visual test of print wheel alignment.

The vertical lines should just touch and be accurately aligned with a skew of no more than 0.005 inch.

No possible error messages, refer to Figure 1 for verification.

#### TEST 16

Visual test that all 96 characters on the print wheel are printable.

All ASCII characters between 020 and 07F Hexadecimal are printed.

No possible error messages, refer to Figure 1 for verification.

TEST NUMBER 05 TEST TERMINATING CHARACTER ( TEST TERMINATING ADDRESS TEST NUMBER 06 TEST NUMBER 07 TEST NUMBER 08 TEST OF BUSY SIGNAL TEST NUMBER 09 6 7 9 TEST NUMBER 10 **Q**23 7 TEST NUMBER 11 TEST FAST MOVE BIT TEST FAST MOVE BIT TEST NUMBER 12

THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS

THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS TEST NUMBER 14 TEST RIBBON UP \* \* \* \* \* TEST NUMBER 15

6

c!\*#\$\$&\*()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[\]^ `abcdefghijklmnopqrstuvwxyz[|]~q!\*\$\$&&\*()\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPQRSTUVWXYZ[\]^ `abcdefghijklmnopqrstuvwxyz[|]~q DIATST COMPLETE, FOR DIABLO PRINTER SERIAL NUMBER 01234-ABCD

TEST NUMBER 16

$\overline{\phantom{a}}$ TEST NUMBER 04 TEST TERMINATING CHARACTER ( TEST TERMINATING ADDRESS Page 3-19. TEST NUMBER 05 TEST NUMBER 07 TEST OF BUSY SIGNAL 0 TEST NUMBER 09 ر  $\mathcal{L}$ 0 C C C TEST NUMBER 10 TEST FAST MOVE BIT TEST FAST MOVE BIT TEST NUMBER 11

THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS

THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS TEST NUMBER 13

TEST RIBBON UP \* \* \* \* \*

TEST RIBBON DROP \* \* \* 0 TEST NUMBER 14 TEST NUMBER 15 TEST NUMBER | ] 6!\*8\$\$&'()\*+,-./0123456789:;<=>7#ABCDEFCRIJKLMNOPORSTUVMXYS(\)]^\_\*abcdefghijklmnopgrstuvwxys(i)-~ 6!\*\$\$\$&'()\*+,-./0123456789:;<=>?#ABCDEFGHIJKLMNOPORSTUVMXYS(\)]^\_\*abcdefghijklmnopgrstuvwxys(i)-~ DIATST COMPLETE, FOR DIABLO PRINTER SERIAL NUMBER 01234-ABCD ALL TESTS PASSED WITH NO PROGRAM DETECTABLE ERRORS

# RAMCOM MULTI-ALGORITHM MEMORY TEST

#### RAMCOM - MULTI-ALGORITHM MEMORY TEST

| Program | Applicable Machine Assemblies                  |

|---------|------------------------------------------------|

| RAMCOM  | 8080 DOS, OP-1/R 8K Chips and OP-1/R 16K Chips |

| RAMH80  | 8080 HDOS                                      |

| RAMH80  | 8080 4K Memory Board                           |

| RAMR8   | OP-1/R 8K Chips                                |

| RAMR16  | OP-1/R 16K Chips                               |

| RAM08   | 8008 DOS                                       |

#### Applicable Assemblies

| 5000-1107-X     | 8K Memory Board        | (X=1,2)               |

|-----------------|------------------------|-----------------------|

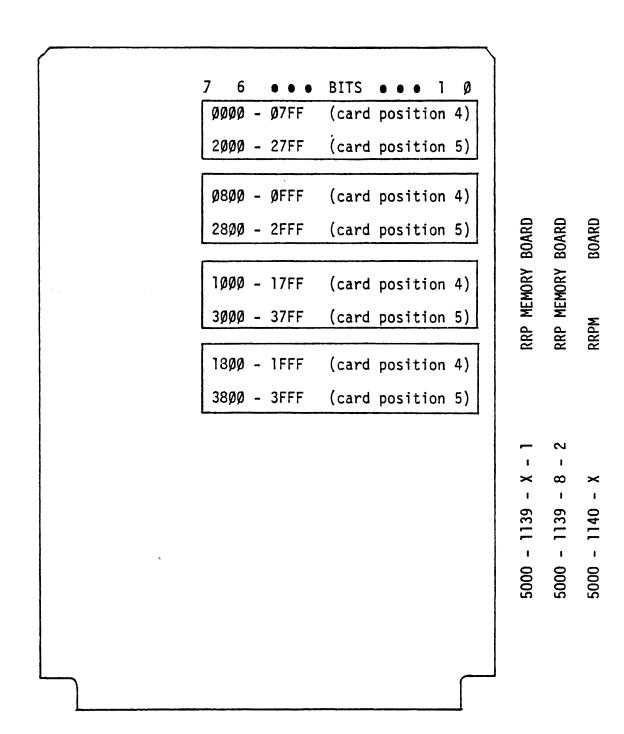

| 5000-1139-X-1   | RRP Memory Board       | (X=1-7)               |

| 5000-1139-8-2   | RRP Memory Board       |                       |

| 5000-1140-X     | RRPM Board             | (X=1-8)               |

| 5000-1142-X-Y   | 32K RAM Board          | (X=1-8, Y=1,2)        |

| 5000-1155-X-Y-Z | Universal Memory Board | (X=1-5, Y=0-4, Z=0-4) |

#### General Description

The purpose of the RAMCOM program (and subsets) is to determine if the Read/Write Random Access Memory (RAM) is working properly and, if not, to give an indication of which addresses and bits are incorrect. The program requires no operator interaction unless it is desired to change the test parameters which, upon loading, default to test all existing RAM with no stop on error detection.

RAMCOM is a multi-algorithm RAM test that is also self relocatable. The algorithms used are a "marching ones and zeros" and "RAM leakage with neighboring bits refreshed". To facilitate testing all portions of RAM equally, RAMCOM changes it's location after every loop.

2K of memory (addresses 0800 to 0FFF) is required to run RAMCOM. This 2K block is known to exist as RAM in all hardware configurations since there must be RAM at addresses 0800 to 0868 for the Display and Input/Output Microprocessors, and RAM must exist in 1K (minimum) blocks at 1K address boundaries.

This manual applies to both 8008 and 8080 versions of RAMCOM.

#### Loading Procedure

RAMCOM can be loaded into memory using any conveniently available loading method. It is a completely self-contained program. If RAMCOM loads properly, it will identify itself and wait five seconds before testing all existing RAM. This delay is necessary to allow all hardware vectors to stick.

#### Operator Action

The total 64K range of memory is divided into 64 blocks, each of 1K length. For operator convenience, these blocks are displayed as 16 groups of 4 on the second line of the display screen, as shown in Figure 1. Each group of 4, representing a block of length 4K, is delimited by a reversed hexadecimal digit representing the most significant digit of the beginning address of the 4K block. Within a 4K block marked with the reversed digit X, the 4 individual 1K blocks correspond to addresses X000 to X3FF, X400 to X7FF, X800 to XBFF, and XC00 to XFFF. To serve as a reminder to the operator, the digits 0, 4, 8, and C are displayed in the last 4K block (marked with a reversed F) but only if this last block does not exist as RAM. Portions of memory to be tested are indicated by an asterisk (\*) in the appropriate position(s) on the second line of the display screen while areas of non-existant RAM or of existing ROM or PROM memory (which cannot be tested by RAMCOM) are denoted by the absence of asterisks. The 2K block in which the program resides is marked by reversed P's.

Now, when RAMCOM is first loaded, a cursory RAM existance check is performed and asterisks are automatially filled in for every 1K block which is determined to consist of RAM. After this, testing commences.

At any time while RAMCOM is testing, the operator may change the portion of memory to be tested and continue either with or without a stop on error detection. However, a pause might be discerned after the operator types "SHIFTED HOME" and before RAMCOM beeps to acknowledge that the operator has control.

The following is a list of valid test parameter commands:

Home (with SHIFT key) will give operator control and allow the operator to change test parameters.

Cursor Right ( key) - Stop testing and move the cursor, consisting of a continuously changing character on the second line of the display screen, one position to the right. This is in preparation for changing the character at the cursor from a space to an asterisk or vice versa.

Cursor Left ( key) - Stop testing and move the cursor one position to the left.

Asterisk (\* and SHIFT keys) - Stop testing, write an asterisk at the cursor position, and move the cursor one position to the right. The asterisk signifies that the IK block so marked will be tested when testing resumes.

Space (SPACE bar) - Stop testing, clear the character at the cursor position, and move the cursor one position to the right. The absence of an asterisk signifies that the 1K block so marked will be skipped when testing resumes.

Restart (PROG key) - Return to the beginning of RAMCOM, re-search and mark all existing RAM with asterisk, clear the loop count, error count, and actual, expected, and over-write error values, and commence testing with no stop on error detection and relocation enabled.

Go (G key without SHIFT key) - Continue testing the 1K blocks that are currently marked with an asterisk and do not stop testing on error detection. If any asterisks were changed from their previous positions, clear the loop count, error count, and actual, expected, and over-write error values. The Go mode is useful if the opertor wishes to determine the overall integrity of the RAM memory.

Stop (S key without SHIFT key) - Continue testing the 1K blocks that are currently marked with an asterisk but halt testing and beep if an error is detected. If any asterisks were changed from their previous positions, clear the loop count, error count, and actual, expected, and over-write error values. The stop mode is useful if the operator wished to analyze the various address and data values existing when an error is detected.

No Relocating (N key without SHIFT key) - Continue testing without relocating the program after each loop. Typing the N key will put an "N" on the screen between Errors and Address. Can only be reset by typing the PROG key.

#### **Errors**

All errors are indicated by RAMCOM incrementing the error count and updating the actual, expected, and over-write values displayed on the top line of the display screen, as shown in Figure 1. Also if the Stop mode is in effect, each error will beep and halt testing, thereby allowing the operator to examine the updated error information.

Errors are of two types: Data errors and Address errors. Data errors are caused by failure of a RAM chip to "hold" the data written into it by a previous write pass. This could be the result of a faulty or marginal chip, incorrect insertion of a chip in it's socket, or grounded, floating, or interconnected data lines. A faulty or incorrectly inserted chip or a bad data line will generate very many errors (over 0400 hex for each 1K block) per loop. A marginal chip will usually have only a few errors recorded for each loop. All data errors are characterized by having the actual and expected values differ by at most only a few bits, i.e. ACT=DE, EXP=FF, OVRWRT=00.

Address errors are caused by the writing of correct data at an incorrect location. This subsequently shows up when the data is read. Address errors could be the result of grounded, floating, or interconnected addressing lines. Address errors tend to generate very many errors (over 0400 for each 1K block) per loop and are characterized by having the actual and overwrite values differ by at most a few bits, i.e. ACT=F7, EXP=00, OVRWRT=FF. Also, since addressing lines are common for a whole memory board, a bad Addressing line will usually cause errors for all RAM on the board.

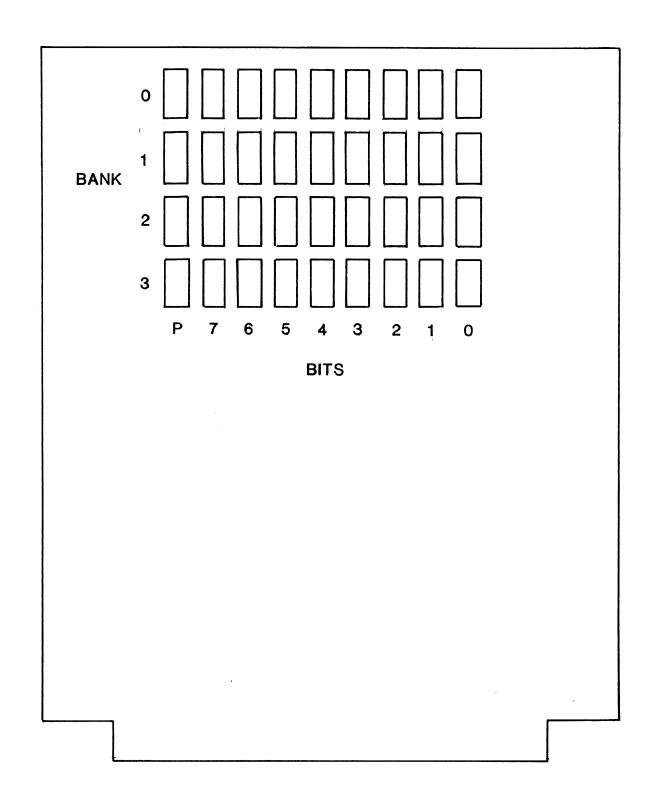

In addition to the individual error values updated each time an error is detected, "stuck" data bits are displayed on lines 3 and 4 of the display screen. There are 16 stuck bits displays, one for each 4K block in the 64K memory. The horizontal position of any asterisk(\*) above each stuck bits display has nothing whatever to do with the interpretation of the information displayed in the bits; asterisks merely specify which 1K block(s) are participating in the test and hence the address range represented by the stuck bits.

Each stuck bits display shows the accumulated errors for all eight data bits of the 4K block which is displayed above it. The individual bits are easily identified; bits 7, 6, 5, and 4 are displayed from left to right on display line 3, while bits 3, 2, 1, and 0 are displayed immediately below them on display line 4. Each bit is displayed as one of the following characters:

| CHARACTER  | MEANING                                                       |

|------------|---------------------------------------------------------------|

| - (hyphen) | The bit was always correct.                                   |

| 0          | The bit was incorrectly low when it should have been high.    |

| 1          | The bit was incorrectly high when it should have been low.    |

| X          | The bit was both incorrectly low and high at different times. |

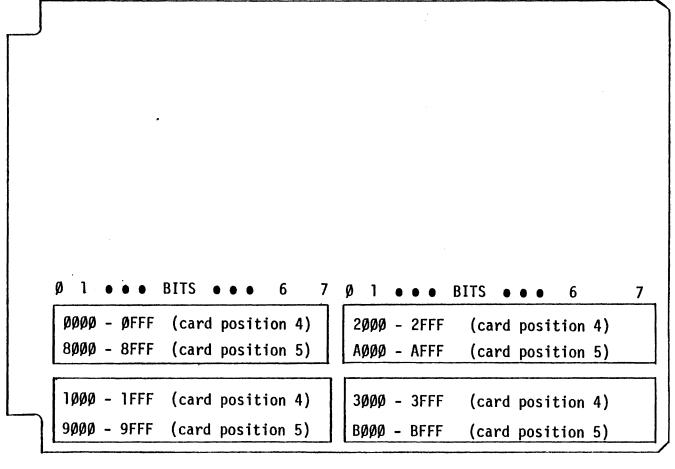

An error at a known bit and in a known address range can be mapped to a particular chip using the appropriate Figure 2, 3, 4, or 5. Assume that the error shown in Figure 1 is detected, i.e. bit 2 in address range 1000 to 17FF is stuck high. Then, if an RRP Memory Board is being used, Figure 3 shows that the bad chip is third up in the second leftmost block of 8 chips on the board in slot 4, holding the board with the connector "fingers" on the left. If, however, a 32K RAM Board is being used, Figure 4 indicates that the bad chip is located on the top half of the board, the third chip in from the left hand side, and in the second row of chips on the board in slot 4.

#### Test Description

When RAMCOM is first loaded, or when the PROG key is depressed by the operator, a cursory RAM existence check is performed in order to fill in the initial asterisks. This cursory check uses the following algorithm:

- 1. One location in the 1K block to be checked is read.

- 2. The inverse of the original contents is written to the location.

- 3. The location is read again and the new contents is compared with the original contents. If the new contents and the original contents differ, even if only by one bit out of the eight bits, the 1K block is assumed to exist as RAM and an asterisk is written in the appropriate location on the display screen. If the new and original contents are identical, the assumption is made that the 1K block is non-existant RAM or existing ROM or PROM and no asterisk is written.

- 4. Steps 1 through 3 are repeated for all 1K blocks which could exist as RAM. Thus, if an 8K maximum length memory board such as an 1107, 1139, or 1140 is plugged into slot 4, steps 1 through 3 are performed only for the first 16 1K blocks. If a 32K maximum length board such as an 1142, or 1155 is plugged into slot 4, steps 1 through 3 are performed for all 64 1K blocks.

After the cursory RAM existance check, testing commmences. A multi-algorithm testing sequence is used which proceeds as follows:

- 1. Load 00 into all locations in all 1K blocks under test.

- 2. Read from the first location in the first 1K block and compare the actual value with the expected value. Update any errors to the display screen.

- 3. Over-write the inverse of the expected value to the current location.

- 4. Repeat steps 2 and 3 for all locations in all 1K blocks under test, with the current location going forward (from low addresses to high addresses).

- 5. Read from the last location in the last IK block and compare the actual with the expected value (which is now the inverse of the value in step 1).

- 6. Over-write the inverse of the expected value to the current location.

- 7. Repeat steps 5 and 6 for all locations in all 1K blocks under test, with the current location going backward (from high addresses to low addresses).

- 8. Repeat steps 1 through 7 seven times with the hex values 01, 03, 07, 0F, 1F, 3F, 7F.

- 9. Load OFF hex into all locations in all 1K blocks under test.

- 10. Overwrite the inverse of the original value to the current location.

- 11. Refresh the contents of the 8 surrounding bits on each 4K chip.

- 12. Check the value of the current location on each 4K chip to verify no leakage occurred into or out of the bit under test on each 4K chip.

- 13. Repeat steps 10, 11, and 12 for all groups of 4K chips under test.

- 14. Repeat steps 10 through 13 for all 4K locations in a 4K chip.

- 15. Repeat steps 9 through 14 with the hex value 00.

- 16. a). Overwrite the activity flag (flashing asterisk) with an R signifying relocating in process.

- b). Starting with the program location, search the RAM under test for two contiguous IK blocks that remain error free up to this point (wrapping around to the beginning if necessary).

- c). After a new destination for the program is located, re-write the program to this location.

- d). Overwrite the R with the activity flag once again.

- e). Increment the loop counter on the display and continue testing from this new area.

- Load OFF hex into all locations in all IK blocks under test.

- 18. Read from the first location in the first 1K block and compare the actual value with the expected value. Update any errors to the display screen.

- 19. Over-write the inverse of the expected value to the current location.

- 20. Repeat steps 18 and 19 for all locations in all 1K blocks under test, with the current location going forward (from low addresses to high addresses).

- 21. Read from the last location in the last 1K blocks under test, with the current location going forward (from low addresses to high addresses).

- 22. Over-write the inverse of the expected value to the current location.

- 23. Randomly select and de-select the IK blocks under test.

- 24. Repeat steps 17 through 28 seven times with the hex values 01, 03, 07, 0F, 1F, 3F, 7F, FE, FC, F8, F0, E0, C0, 80, 00, 01, .... (Note that after 16 values, the values repeat).

- 25. Repeat steps 9 through 25 until operator intervention.

Page 4C-7.

RAMCOM DISPLAY SCREEN

Figure 1

| 7 6 • • •                  | BITS • • • 1 Ø                                 |

|----------------------------|------------------------------------------------|

| 0000 - 07FF                | (card position 4)                              |

| 2000 - 27FF                | (card position 5)                              |

| Ø8ØØ - ØFFF                | (card position 4)                              |

| 2800 - 2FFF                | (card position 5)                              |

| 1000 - 17FF                | (card position 4)                              |

| 3000 - 37FF                | (card position 5)                              |

| 1000 1555                  | (and position A)                               |

| 1800 - 1FFF<br>3800 - 3FFF | <pre>(card position 4) (card position 5)</pre> |

```

Ø 1

BITS

6

Ø

BITS

6

7

•••

•••

•••

•••

ØØØØ - ØFFF

(card position 4)

2000 - 2FFF

(card position 4)

8000 - 8FFF

(card position 5)

AØØØ - AFFF

(card position 5)

1000 - 1FFF

(card position 4)

3000 - 3FFF

(card position 4)

9ØØØ - 9FFF

(card position 5)

BØØØ - BFFF

(card position 5)

BITS

BITS

600 6

600 6

4000 - 4FFF

(card position 4)

6000 - 6FFF

(card position 4)

CØØØ - CFFF

(card position 5)

EØØØ - EFFF

(card position 5)

5000 - 5FFF

(card position 4)

7ØØØ - 7FFF

(card position 4)

DØØØ - DFFF

(card position 5)

FØØØ - FFFF

(card position 5)

5000 - 1142 - X - Y

32K RAM BOARD

```

5000 - 1155 - X - Y - Z

UNIVERSAL MEMORY BOARD

# **PARRAM**

# MULTI-ALGORITHM MEMORY TEST WITH PARITY CHECK

# Applicable Assemblies

5000-11114 CPU-M Card

# General Description

The purpose of the PARRAM program is to determine if the Read/Write Random Access Memory (RAM) and the Memory Parity Error Detection is functioning correctly, and if not, to give an indication of which addresses and bits are incorrect. The program requires limited operator interaction while the program is running.

PARRAM is a multi-algorithm RAM test that is self-relocatable or can be operator forced relocatable. The algorithms used in this program are "marching ones and zeros" and "RAM leakage, with neighboring bits refreshed". This program will relocate after each loop to make sure that all portions of memory are tested. Also after each loop, the characters will reverse so that they are not burned permanently on the screen.

16K of memory (addresses 00 to 3FFFH) is required to run PARRAM. This 16K block is known to exist as RAM in all hardware configurations since there must be RAM at addresses 0800H to 0868H for the Display and Input/Output microprocessors, and RAM must exist in 16K (minimum) blocks.

#### Loading Procedure

PARRAM can be loaded into memory using any convenient available method. When PARRAM loads the screen will go blank for five seconds to allow all hardware vectors to stick.

#### **Operator Action**

Once five seconds have elapsed, three command lines will appear (see Figure 1), and an audible beep will be generated. At this time the program is waiting for a "Y", "N" or shifted "HOME", meaning, YES, test memory parity error detection, NO, do not test memory parity error detection, or, shifted "HOME", give the operator control of the test parameters. Also if 'NO' is typed and the error message 'Parity Malfunction' appears, IFL bit 5 is stuck low.

The total range of memory is divided into 4 blocks, each of 16K length. These blocks are displayed as 4 groups on the second and third lines of the display screen, as shown in Figure 1. Each group representing a block of 16K is delimited by a reversed hexadecimal digit representing the most significant digit of the beginning address of that 16K block. The portions of RAM to be tested are indicated by an (\*) on the second line, corresponding to the most significant digit of the beginning address of that 16K block. Areas of non-existent RAM or of existent ROM or PROM (which cannot be tested by PARRAM) are denoted by the absence of an (\*). The beginning address of the program is displayed at "Program Location" on the second line of the display screen as shown in Figure 1.

Before the user indicates whether or not to check the Memory Parity Error Detection a cursory RAM check is performed, and asterisks are automatically filled in for every 16K block which consists of RAM. After the Memory Parity Error Detection question is answered, testing commences.

At any time while PARRAM is testing, the operator may change the portion of memory to be tested and continue either with or without a stop on error detection. However, a pause might be discerned after the operator types "SHIFTED HOME" and before PARRAM beeps to acknowledge that the operator has control.

The following is a list of valid test parameter commands:

Home (with SHIFT key) - Will give operator control and allow the operator to change test parameters.

Cursor Right (C3 key) - Stop testing and move the cursor on the second line of the display screen, one position to the right. This is in preparation for changing the character at the cursor from a space to an asterisk or vice versa.

Cursor Left (C1 key) - Stop testing and move the cursor one position to the left.

Asterisk (unshifted) - Stop testing, write an asterisk at the cursor position, and move the cursor one position to the right. The asterisk signifies that the 16K block so marked will be tested when testing resumes.

Space (SPACE bar) - Stop testing, clear the character at the cursor position, and move the cursor one position to the right. The absence of an asterisk signifies that the 16K block so marked will be skipped when testing resumes.

Restart (PROG key) - Return to the beginning of PARRAM, wait for a "Y" or "N", meaning whether or not to test Memory Parity Error Detection; re-search and mark all existing RAM with an asterisk, clear the loop count, error count, actual and expected values, and commence testing with no stop on error detection and relocation enabled.

Relocate (R key, unshifted) - Immediately forces relocation to occur to the next chip currently marked with an asterisk, and which does not have any errors reported in it. An "R" will replace the asterisk in the activity flag during this process, and an asterisk will replace the R after the operation is complete.

Go on error (G key, unshifted) - Continue testing the 16K blocks that are currently marked with an asterisk and do not stop testing on error detection. The Go mode is useful if the operator wishes to determine the overall integrity of the RAM.

Stop (S key, unshifted) - Continue testing the 16K blocks that are currently marked with an asterisk but halt testing and beep if an error is detected. The stop mode is useful if the operator wished to analyze the various address and data values existing when an error is detected. An "S" will appear on the first line of the display screen (see Figure 1) to indicate Stop on error mode. This mode can be reset by typing "G" for "Go on error", or the PROG key to restart the program.

No Relocating (N key, unshifted) - Continue testing without relocating the program after each loop. Typing the N key will put an "N" on the first line of the display screen (see Figure 1). This can only be reset by typing the PROG key.

#### **Errors**

All errors except one are indicated by PARRAM by incrementing the error count and updating the actual and expected values displayed on the first line of the display screen, as shown in Figure 1. Also if the Stop mode is in effect, each error will beep and halt testing, thereby allowing the operator to examine the updated error information on the third line of the display screen. To continue testing where the error occurred the key marked "C" has to be depressed.

The exception to this type of error is if the Memory Parity Error Detection hardware does not work correctly. If the operator decides to test the Parity Hardware and there is a malfunction an error message will be displayed on the third line of the display screen. At this time the operator has to re-evaluate the integrity of the hardware, and can try again by depressing one of the three keys described in the Operator Action section.

Data errors are caused by failure of a RAM chip to "hold" the data written into it by a previous write pass. This could be the result of a faulty or marginal chip, incorrect insertion of a chip in it's socket, or grounded, floating, or interconnected data lines. A faulty or incorrectly inserted chip or bad data line will generate very many errors (over 0400 hex for each 16K block) per loop. A marginal chip will usually have only a few errors recorded for each loop. All data errors are characterized by having the actual and expected values differ by at most only a few bits, i.e. ACT=DE, EXP=FF.

In addition to the individual error values updated each time an error is detected, "stuck" data bits are displayed on line 3 of the display screen. There are 4 stuck bits displays, one for each 16K block in the 64K memory.

Each stuck bits display shows the accumulated errors for the parity bit and all eight data bits of the 16K block that is characterized by a reversed hexadecimal digit representing the most significant digit of the beginning address of that 16K block, which is displayed to the left of each group. The individual bits are easily identified; P for parity, bits 7,6,5,4,3,2,1 and 0 are displayed from left to right on the second display line as shown in Figure 1. Each bit is displayed as one of the following characters:

# CHARACTER MEANING

| - (hyphen) | The bit was always correct.                                |

|------------|------------------------------------------------------------|

| 0          | The bit was incorrectly low when it should have been high. |

| 1          | The bit was incorrectly high when it should have been low. |

| X          | The bit was incorrectly low and high at different times.   |

An error at a known bit and in a known address can be mapped to a particular chip using Figure 2. Assume that the error shown in Figure 1 is detected, i.e., P bit at address 3FFFH is stuck low.

When looking at Figure 2

Bank 0 = addresses 00000-3FFFH Bank 1 = addresses A000H-7FFFH Bank 2 = addresses 8000H-BFFFH Bank 3 = addresses C000H-FFFFH

on a 64K machine. The address shown in Figure 1 (3FFFH) is located in Bank 1, and the bit that caused the error was bit P.

#### **Test Description**

When PARRAM is first loaded, or when the PROG key is depressed by the operator, a cursory RAM existence check is performed in order to fill in the initial asterisks. The cursory check uses the following algorithm:

- 1. One location in the 16K block to be checked is read.

- 2. The inverse of the original contents is written to the location.

- 3. The location is read again and the new contents are compared with the original contents. If the new contents and the original contents differ, even if only by one bit out of the eight bits, the 16K block is assumed to exist as RAM and an asterisk is written in the appropriate location on the display screen. If the new and original contents are identical, the assumption is made that the 16K block is non-existant RAM or existing ROM or PROM and no asterisk is written.

- 4. Steps 1 through 3 are repeated for all 16K blocks which could exist as RAM.

After the cursory RAM existance check is complete, the Memory Parity Error Detection hardware is checked only if the operator decided to do so. This hardware check is done using the following algorithm:

- 1. Parity is changed from odd (normal state) to even parity.

- 2. A value is written into a memory location.

- 3. Parity is changed back to the normal state (from even to odd).

- 4. The value is read back from that same location, causing an expected error. If no error occurred then an error message is put on the display screen and PARRAM jumps back to the initial parity question to try again.

After the Memory Parity Error Detection question is answered, testing commences. A multi-algorithm testing sequence is used which proceeds as follows:

- 1. Load 00 into all locations in all 16K blocks under test.

- 2. Read from the first location in the first 16K block and compare the actual value with the expected value. Update any errors to the display screen.

Page 4E-5.

- 3. Over-write the inverse of the expected value to the current location.

- 4. Repeat steps 2 and 3 for all locations in all 16K blocks under test, with the current location going forward (from low addresses to high addresses).

- 5. Read from the last location in the last 16K block and compare the actual with the expected value (which is now the inverse of the value in step 1).

- 6. Over-write the inverse of the expected value to the current location.

- 7. Repeat steps 5 and 6 for all locations in all 16K blocks under test, with the current location going backward (from high addresses to low addresses).

- 8. Repeat steps 1 through 7 seven times with the hex values 01, 03, 07, 0F, 1F, 3F, 7F.

- 9. Load OFF hex into all locations in all 16K blocks under test.

- 10. Overwrite the inverse of the original value to the current location.

- 11. Refresh the contents of the 8 surrounding bits on each chip.

- 12. Check the value of the current location on each chip to verify no leakage occurred into or out of the bit under test on each chip.

- 13. Repeat steps 10, 11 and 12 for all groups of 16K chips under test.

- 14. Repeat steps 10 through 13 for all 16K locations in each 16K chip.

- 15. Repeat steps 9 through 14 with the value 00H.

- 16. a) Overwrite the activity flag (flashing asterisk) with an R signifying relocating in process.

- b) Starting with the program location, search the RAM under test for the next 16K block that remained error free up to this point (wrapping around to the beginning if necessary).

- c) After a new destination for the program is located, re-write the program to this location.

- d) Overwrite the R with the activity flag once again.

- e) Increment the loop counter on the display and continue testing from this new area.

- 17. Repeat steps 1 through 16 until operator intervention.

# PARRAM SCREEN DISPLAY

- Figure 1 -

CPU-M. CARD FIGURE 2

# PRNTST CENTRONICS PRINTER TEST

#### PRNTST - CENTRONICS/OKIDATA PRINTER TEST

# Applicable Assemblies

| 5000-1101-1 | Printer Controller Board     |         |

|-------------|------------------------------|---------|

| 5000-1127-X | Byte String Controller Board | (X=1-4) |

| 5000-1185-1 | Printer Controller Board *   |         |

#### General Description

The purpose of the PRNTST program is to determine if the Centronics or Okidata printer and the Printer Controller are working properly and, if not, to give an indication of which print functions are incorrect. The program requires assistance from the operator to perform certain actions and analyze the PRINTOUT (see Figures 1-4) at the end of the last test.

8K of memory is required to run PRNTST.

This manual applies to both 8008 and 8080 versions of PRNTST.

#### Loading Procedure

PRNTST can be loaded into memory using any conveniently available loading method. It is a completely self-contained program. If PRNTST loads properly, it will identify itself and immediately start Test 00.

#### Operator Action

The operator must answer three questions after PRNTST initially loads by depressing the proper key. These questions are the type of Printer (Okidata or Centronics), column width (80 or 132) and whether an 1185-1 board.

The first three tests (Tests 00, 01 and 02) ask the operator to manually control the printer. A message appears on the display screen and PRNTST waits for the operator to follow the direction. The operator indicates compliance by typing the space bar after performing the requested operation. When the space code is sensed, PRNTST continues to the next part of the test or to the next test.

After Test 02, all tests except Test 12 execute automatically. When the entire test has been completed, the prompt "TEST COMPLETED, TYPE SPACE TO REPEAT PRNTST" will be displayed. If a space is typed on the keyboard, PRNTST will be re-run.

Refer to Appendix A for specialized test run options.

\* NOTE: 5000-1185-1 Board requires a COMTST8 Diagnostic Plug to execute Test 12.

#### **Errors**

All program detectable errors are indicated by an appropriate error message on the display screen and the simultaneous activation of the bell. The bell will ring only to notify the operator of an error. The error message displayed on the screen attempts to give a description of the nature of the problem. In most cases, this message should be adequate to diagnose and fix the error. Otherwise, refer to the detailed description of the specific test to determine the purpose and expected results for the displayed error message.

After an error message is displayed, the operator has three ways to proceed. Typing the SPACE bar will continue testing on the next test, typing the R key (without the SHIFT key) will repeat the current test, and depressing the PROG key will restart the program.

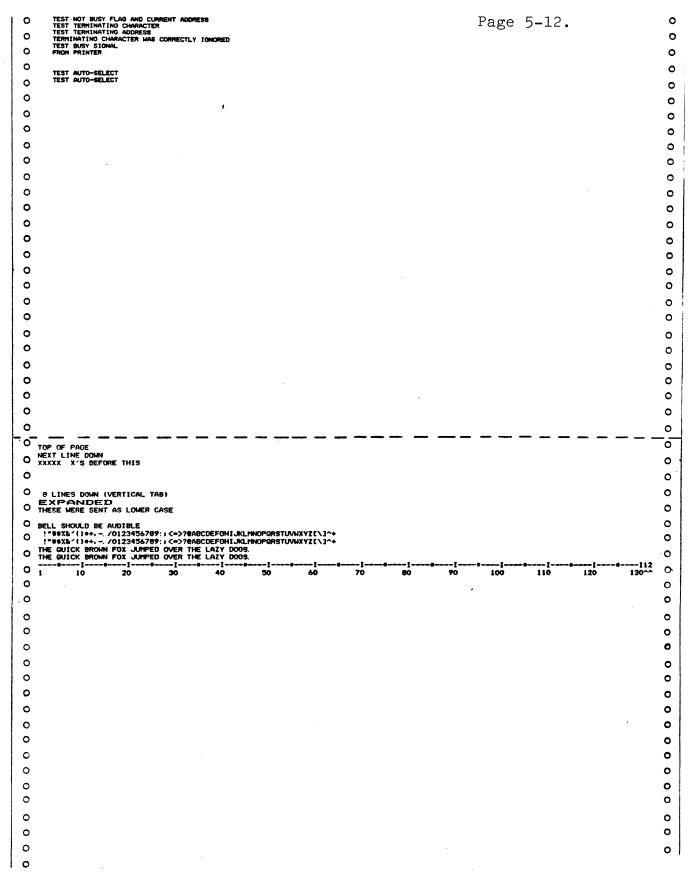

Even if PRNTST proceeds from Test 00 to Test 10 without a displayed error, there could still be a printed error since PRNTST has no way to examine the characters printed by the Printer. After the final test the operator must compare the print-out produced by the tests to the correct corresponding PRINTOUT shown in Figures 1-4. Also, during Test 08, the operator must listen for the Printer to beep as the line "BELL SHOULD BE AUDIBLE" is printed.

#### Test Description

All test operations are described in this section. The program will halt and the specified error message is displayed if expected results are not obtained.

On the following pages, each test is listed with a brief description of what is being tested. Below the description, all possible error messages are listed, with an explanation of the cause of the message. However, in addition to the specified messages, other messages may be displayed. These messages are general to all the tests and are listed below:

#### PLEASE MAKE PRINTER READY

(Turn on printer, plug printer into OP-1, select printer with "Select" pushbutton).

#### PLEASE SELECT PRINTER

(Select printer with "Select" pushbutton).

#### Test 00 - Test of Controller Select

Tests that the Printer Controller does not respond to an incorrect select address, does respond to the correct address, and INIT de-selected a selected Printer Controller. The correct device select address is OB4 hex. The incorrect select addresses are those single byte addresses whose high order nibbles "or-ed" with their low order nibbles do not result in OF hex. This is derived from the fact that a 4 input AND gate performs the device selection from the address bits of the select address bits of the select address. Thus a select address of OFF hex would attempt to select all devices.

#### CONTROLLER SELECTED WITH INCORRECT ADDRESS (XX)

IFL to the select address XX hex gave a result other than OFF hex (open bus).

#### CONTROLLER IS NOT SELECTED WITH CORRECT ADDRESS (B4)

IFL to the correct Printer Controller address (OB4 hex) gave a result of OFF hex (open bus).

#### INIT DOES NOT DESELECT CONTROLLER

After an INIT to the selected Printer Controller, IFL did not get a result of OFF hex (open bus).

#### Test 01 - Test of Printer Selected Flag

Tests that the Select bit (IFL bit 6) from the printer "Select" pushbutton can be read by the software.

ACTUAL IFL BITS = XXXX,XXXX ERROR DETECTED AT IFL BIT 6: SELECTED

Either IFL bit 6 was low when it should have been high, or high when it should have been low.

#### Test 02 - Test of Printer Not Ready Flag

Tests that the Not Ready bit (IFL bit 1) from the printer hardware can e read by the software.

ACTUAL IFL BITS = XXXX,XXXX

ERROR DETECTED AT IFL BIT 6: SELECTED

Either IFL bit 6 was low when it should have been high, or high when it should have been low.

#### ERROR DETECTED AT IFL BIT 1: NOT READY

Either IFL bit 1 was low when it should have been high, or high when it should have been low.

#### Test 03 - Test of Controller Not Busy Flag and Current Address

Test that the Not Busy bit (IFL bit 7) is set by a DVCL and INIT, cleared for the duration of a print command (COM1), and is set upon completion of print. Also, test that locations PCAH (0823) and PCAL (0822) are initialized to PSAH (0821) and PSAL (0820) by a print command and eventually increment til they equal PTAH (0825) and PTAL (0824) upon print completion.

#### NOT BUSY FLAG IS NOT SET BY INIT AND DVCL

After an INIT and DVCL, IFL bit 7 was low when it should have been high.

#### COM1 DOES NOT RESET NOT BUSY FLAG

After a print command, IFL bit 7 was high when it should have been low.

#### CURRENT ADDRESS IS NOT INITIALIZED CORRECTLY

After a print command, PCAH and PCAL were not loaded to the address in PSAH and PSAL.

#### NOT BUSY FLAG DOES NOT SET AFTER A PRINT

About two seconds after the print command was given, IFL bit 7 was still low when it should have been high.

#### CURRENT ADDRESS DOES NOT STOP AT CORRECT ADDRESS

After the print command is finished, PCAH and PCAL are not equal to PTAH and PTAL. (Note that the print message is set up such that termination on character and address will occur at the same location.)

Tests that no interrupt is generated when the Not Busy flag is low, the interrupt mask is set to allow an interrupt only from the Printer Adapter, and the interrupts are enabled - disabled. If this test fails, the interrupt priority for the slot that the board is in should be checked with that entered during initialization. If the interrupt priorities match then the interrupt is bad.

Tests 18-21 are visual tests.

Tests 18-1B should be run in sequence.

Test 18

Test of Form Feed. Paper should advance to top of form. "TOP OF FORM" should be printed on top line.

Test 19

Test of carriage return/line feed. Paper should advance one line "NEXT LINE DOWN" should be printed.

Test 1A

Test of Carriage Return. On Okidata Printer the issuing of a Carriage Return also causes a line feed to occur. The message printed should be:

On Centronics Printers the internal buffer is printed and the print head is positioned at the beginning of that line. The message printed should be "XXXXXX ERROR IF NOT X's BEFORE THIS".

On the Printronix Printer the internal line buffer is not printed and the internal buffer pointer is positioned to the start of the buffer. The message: "///// ERROR IF X's BEFORE THIS".

Test 1B

Test of Vertical Tab. The paper should advance to the sixth line and the message printed should be: "6 LINES BELOW TOP OF FORM". The vertical tab on the Printronix requires the use of the VFO therefore, three carriage return/line feeds are issued and the Vertical Tab is not tested.

Test IC

Tests that all characters are printable.

SECTION 1 6 slewed lines of upper case characters ASCII codes 20-5F hex.

SECTION 2 6 slewed lines of lower case characters ASCII codes 60-7E hex, repeated.

If the printer does not support lower case characters, Section 2 will be printed in upper case.

R:A-12/02/80

# Test 04 - Test of Controller Terminating Character and Address

Tests that locations PCAH and PCAL increment until they point to a character matching the character in PTC if PTAH bit 7 is low, but increment until they equal PTAH and PTAL if PTAH bit 7 is high.

#### CURRENT ADDRESS DOES NOT STOP AT TERMINATING CHARACTER

After a print command with a terminating character before the terminating address, PCAH and PCAL are not equal to the address of the terminating character.

#### CURRENT ADDRESS DOES NOT STOP AT TERMINATING ADDRESS

After a print command which had a character equal to PTC, but also had PTAH bit 7 high, PCAH and PCAL are not equal to PTAH and PTAL.

#### Test 05 - Test of Controller Hold Off after Print Command

Tests that during a time consuming printer function such as Carriage Return (with data in the Printer internal line buffer), the printer does not acknowledge receipt of the next character, thereby holding off data transfer from the printer controller.

#### PRINTER BUSY SIGNAL DOES NOT HOLD OFF CONTROLLER

During a print command with a Carriage Return and Line Feed in the middle, PCAH and PCAL continuously incremented, with no hold off pause, until they reached PTAH and PTAL.

# PRINTER BUSY SIGNAL HOLDS OFF CONTROLLER AT INCORRECT ADDRESS

During a print command with a Carriage Return and Line Feed in the middle, PCAH and PCAL paused somewhere between PSAH, PSAL and PTAH, PTAL but not at the correct place (the address of the Carriage Return.)

# Test 06 - Test of INIT and DVCL and COM1

Tests that INIT and DVCL clear the Printer internal line buffer. Also tests that INIT, DVCL, and COM1 abort any previously unfinished print command.

#### INIT DOES NOT CLEAR PRINTER BUFFER

A message left in the Printer internal line buffer was not annihilated by an INIT.

# DVCL DOES NOT CLEAR PRINTER BUFFER

A message left in the Printer internal line buffer was not annihilated by a DVCL.

# DE-SELECT COMMAND DOES NOT DE-SELECT PRINTER

Sending a De-select control (ASCII control DC3) in the middle of a print lien did not reset IFL bit 6.

#### COM1 DOES NOT RESET NOT BUSY FLAG

Attempt to make Not Busy Flag (IFL bit 7) stick low by seding a De-select control (ASCII control DC3) in the middle of a print line was unsuccessful. IFL bit 7 was high.

# INIT DOES NOT ABORT A PRINT JOS REAL TESTALOG BALL TO 1990 character, thereby building out data .rely

4384

INIT did not make a stuck low IFL bit 7 go high.

# DVCL DOES NOT ABORT A PRINTERSAMENT NOT THE CASE WORLD TO ABOUT TAKEN TO

DVCL did not make a stuck low IFL bit 7 go high.

# COM1 DOES NOT ABORT A PRINT CASE STORE COMES TO SECOND

A new print command issued during a previously unfinished command did not re-initialize PCAH and PCAL to PSAH and PSAL (1980) a risky kramnoo falbo a garayo - Derma DAN the MANN, allbaim seit to

# AUTO-SELECT COMMAND DOES NOT SELECT PRINTER

Sending, to a De-selected Printer, a Select control (ASCII control DCl) as the first character in a print message did not make IFL bit 6 go high.

#### Test 07 - Test of Controller Interrupt

Tests that with master interrupt enabled and printer interrupt mask bit set, the Printer Controller Interrupts with the Not Busy bit (IFL bit 7) set, and does not interrupt with the Not Busy bit reset.

#### PRINTER CONTROLLER DOES NOT INTERRUPT WITH NOT BUSY FLAG SET

No interrupt is generated with the printer interrupt mask bit set, master interrupt enabled, and IFL bit 7 high.

#### DE-SELECT COMMAND DOES NOT DE-SELECT PRINTER

An attempt to make the printer busy by sending a De-select control (ASCII control DC3) in the middle of a print line did not reset IFL bit 6.

#### COM1 DOES NOT RESET NOT BUSY FLAG

Attempt to make Not Busy flag (IFL bit 7) stick low by sending a De-select control (ASCII control DC3) in the middle of a print line was unsuccessful. IFL bit 7 was high.

#### PRINTER CONTROLLER INTERRUPTS WITH NOT BUSY FLAG RESET

An interrupt is generated with the printer interrupt mask bit set, master interrupt enabled, and IFL bit 7 low.

#### COM1 DOES NOT ABORT A PRINT

A new print command issued during a previously unfinished command did not re-initialize PCAH and PCAL to PSAH and PSAL.

#### AUTO-SIELECT COMMAND DOES NOT SELECT PRINTER

Sending, to a De-selected Printer, a Select control (ASCII control DCl) as the first character in a print message did not make IFL bit 6 go high.

į

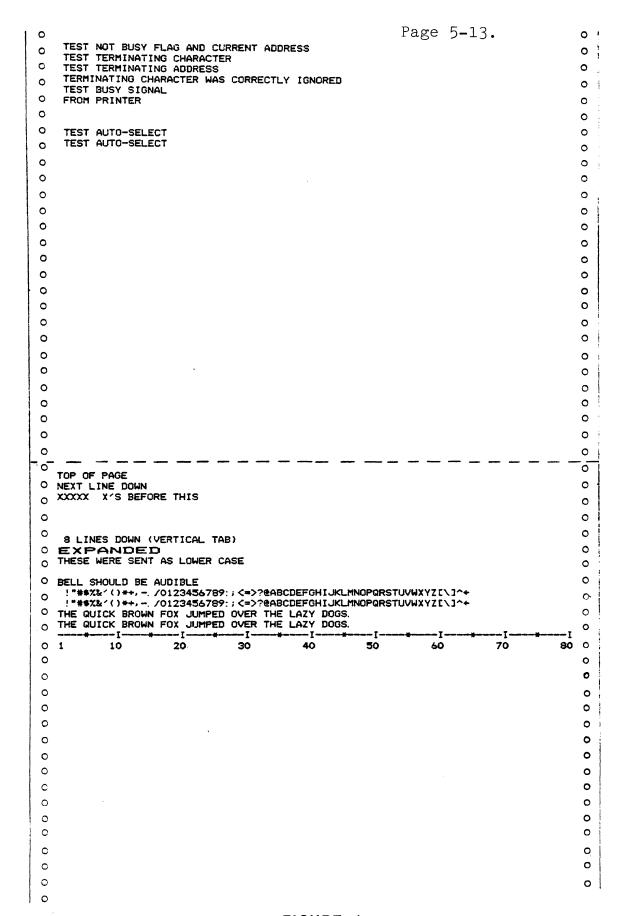

# Test 08 - Test of Printer with only Visual Error Detection

Visual and Audible test of all printer control codes as listed below:

Form Feed (ASCII FF) - move to top of next sheet of paper.

Carriage Return (ASCII CR) - print all characters in internal line buffer.

Line Feed (ASCII LF) - move paper up one line.

Vertical Tab (ASCII VT) - for the Centronics, move to the next group of eight lines on the paper. For the Okidata, move forward the number of lines specified (5).

Expanded (ASCII SO) - print the following line in double width.

Delete (ASCII DEL) - clear internal line buffer.

Bell (ASCII BEL) - ring bell.

Also, for the Centronics Printer, one line is written with overstruck characters to confirm that the Centronics Printer does not automatically line feed upon receiving a CR. For both Printers, another line is written in lower case ASCII characters to confirm that lower case characters are being printed as their upper case equivalents on the Centronics Printer, but in lower case on the Okidata Printer.

No error messages are possible.

# Test 09 - Test of Printer with only Visual Error Detection

Visual test of printing all 64 printable upper case ASCII characters. The characters are printed twice.

and the complete program of the complete program is the complete program of the complete program is the complete program of the complete program is the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program is the complete program in the complete program in the complete program in the complete program is the complete program in th

No error messages are possible.

#### Test 10 - Test of Printer with only Visual Error Detection.

Visual test of printing the foxer message. The following message is printed twice:

THE OUICK BROWN FOX JUMPED OVER THE LAZY DOGS.

No error messages are possible.

# Test 11 - Test of Printer with only Visual Error Detection

Visual test that all columns are printable.

No error messages are possible.

# Test 12 - Testing SYD and L2

This test is only executed if the Printer Controller is an 1185-1. It is first verified that the SYD and L2 signals can be raised and lowered by appropriate COM3 commands. The operator is then asked to insert a diagnostic plug. The plug takes the SYD and L2 outputs and reroutes them into the HWA and BUSY inputs. This allows the program to verify that SYD and L2 signals can be successfully outputted off the controller into the external environment.

#### SYD STUCK HIGH

A COM3 command with bit 1 low did not lower IFL bit 4.

#### SYD STUCK LOW

A COM3 command with bit 1 high did not raise IFL bit 4.

#### L2 STUCK HIGH

A COM3 command with bit 0 low did not lower IFL bit 5.

#### L2 STUCK HIGH

A COM3 command with bit 0 high did not raise IFL bit 5.

#### SYD OFFBOARD OUTPUT STUCK HIGH

Raising SYD did not lower HWA.

#### SYD OFFBOARD OUTPUT STUCK LOW

Lowering SYD did not raise HWA.

#### L2 OFFBOARD OUTPUT STUCK HIGH

Raising L2 did not lower BUSY.

#### L2 OFFBOARD OUTPUT STUCK LOW

Lowering L2 did not raise BUSY.

#### TEST 13 - Testing COM2 with only Visual Error Detection

This test is only executed if the controller is an 1185-1. The test is identical to Test 10, except that a COM2 rather than a COM1 is used to start a print operation.

```

Page 5-10.

TEST NOT BUSY FLAG AND CURRENT ADDRESS

TEST TERMINATING CHARACTER

TEST TERMINATING ADDRESS

TERMINATING CHARACTER WAS CORRECTLY IGNORED

TEST BUSY SIGNAL

FROM PRINTER

0

0

0

0

0

0

0

0

TEST AUTO-SELECT

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

O

O NEXT LINE DOWN

0

0

0

0

O

0

C

8 LINES DOWN (VERTICAL TAB)

C EXPANDED

these were sent as lower case

0

0

O

0

0

0

110

129

0

. 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

```

FIGURE 1

132 COLUMN OKIDATA

```

0

0

Page 5-11.

TEST NOT BUSY FLAG AND CURRENT ADDRESS

0

0

TEST TERMINATING CHARACTER

TEST TERMINATING ADDRESS

C

0

TERMINATING CHARACTER WAS CORRECTLY IGNORED

0

0

TEST BUSY SIGNAL

0

FROM PRINTER

0

0

0

0

TEST AUTO-SELECT

0

0

TEST AUTO-SELECT

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

ō

ō

TOP OF PAGE

0

0

NEXT LINE DOWN

0

0

0

0

0

0

0

0

O 8 LINES DOWN (VERTICAL TAB)

0

O these were sent as lower case

0

0

0

BELL SHOULD BE AUDIBLE

0

!"#$%&^<\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPGRSTUVWXYZ[\]+_

!"#$%&^<\*+,-./0123456789:;<=>?@ABCDEFGHIJKLMNOPGRSTUVWXYZ[\]+_

0

THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS.

O THE QUICK BROWN FOX JUMPED OVER THE LAZY DOGS.

0

0

0

50

0

0

0

0

0

0

0

0

0

0

O

0

0

0

C

0

0

0

0

0

0

0

0

0

0

0

0

```

FIGURE 3

132 COLUMN CENTRONICS

FIGURE 4

80 COLUMN CENTRONICS

# **PRNEX**

CENTRONICS / OKIDATA / PRINTRONIX PRINTER EXERCISER

#### PRNEX - PRINTER EXERCISE PROGRAM

# Applicable Assemblies

5000-1101-1 Printer Controller 5000-1127-X Byte String Controller 5000-1170 Word Mover Controller

#### General Description

PRNEX is an operator usable printer exercise program that allows for visual inspection of all printable characters on a Centronics, Printronix or Okidata Printer.

# Loading Procedure

PRNEX can be loaded into memory using any conveniently available loading procedure. When loaded properly, it will identify itself and await operator input. At this point, the printer should be plugged in, turned on and selected.

#### Operator Action

The following message is displayed on the screen when PRNEX has been loaded:

#### "TYPE 1 FOR 80 COLS OR 2 FOR 132 COLS"

If "1" is typed, the buffer size for all printed lines will be 80 characters. If "2" is typed, the buffer size will be 132 characters.

The next message to appear on the screen will be:

#### "INPUT: SPACE - ALL CHARS, RETURN - OPEN BUFFER, PROG - RESTART"

If the SPACE bar is typed, the printer will commence printing successive lines of all printable ASCII characters (20H-7EH) and will continue until the PROG key is depressed. The first character on the first line will be 20H (ASCII SPACE). The first character on the next line will be 21H (ASCII !), the next, 22H, etc., producing a skewed column effect.

If a printable ASCII character other than SPACE is typed, the printer will commence printing successive lines of that character and will continue until the PROG key is depressed.

Typing the RETURN key allows the operator to then type ASCII characters, including control characters; to the buffer visible on the display screen. The following control characters are recognized:

Bell (07H) - control 'G' Vertical Tab (0BH) - control 'K' Form Feed (0CH) - control 'L' Expanded Mode (0EH) - control 'N' Delete (7FH) - shifted 'DEL'

Printable alphabetic characters typed to the buffer will be upper case when the F0 key is lighted.

When the RETURN key is typed again, the printer will commence printing successive lines consisting of the characters in the screen buffer. The printing operation will continue until the PROG key is depressed.

# DSTTST DISKETTE CONTROLLER TEST

#### DSTTST - DISKETTE CONTROLLER TEST

# Applicable Assemblies

5000-1135-1

Diskette Controller Board

#### General Description

The purpose of the DSTTST program is to determine if the Diskette Drives and Diskette Controller are working properly and, if not, to give an indication of which functions are incorrect. The program requires assistance from the operator to perform certain actions in the IFL test section.

16K (or more) of memory is required to run DSTTST.

This manual applies to the 8080 versions of DSTTST only.

# Loading Procedure

DSTTST can be loaded into memory using any conveniently available loading method. It is a completely self-contained program. If DSTTST loads properly, it will identify itself and pause before requesting test parameters.

# Operator Action

On line 3 of the display screen the message "Type (S)ynchronous; (A)synchronous" will appear. At this time type an (S) if there is a Synchronous adapter or an (A) if there is an Asynchronous adapter. After answering the previous question, the following messages appear on the display screen and permit the operator to change the test parameters or to leave the defaults as they are:

#### \*SKIP IFL TESTS (Y OR N)? =Y

This option skips the lengthy operator interactive "IFL tests" (Tests 0-9) and proceeds immediately to the "run time test" (Test 10) which continuously exercises the diskette. This section must be run at least once through.

#### \*STOP AT AN ERROR (Y OR N)? =N

Tests 8, 9, and 10 will not stop at an error unless the operator answers Yes. When DSTTST does stop at an error, the operator is given control.

#### \*NUMBER OF SECTORS (1-16)? =16

The number of the highest sector at which an operation will start in Test 10. The legal values are dependent on buffer size and are listed in Figure 1.

#### \*DRIVE TO BE TESTED (0-3)? =1

All tests are performed using this drive.

#### \*TRACKS TO BE TESTED (MIN-0, MAX-76)? =0,2,4,32,76

The tracks at which operations will be performed in Test 10. Single tracks must be separated by a comma or a space. If a hyphen separates two numbers, all tracks between and including the two numbers are selected.

# \*BUFFER SIZE (256 BYTE BLOCKS)? =16

This specifies a buffer length of 256 bytes times the inputted number to be used for operations in test 10. A range of 1-17 is permitted.

#### \*OPERATIONS (A-ALL R-READ W-WRITE)? =A

Operations of read only, write only, or both write and read can be specified for test 10.

#### RETRY ATTEMPTS BEFORE ERROR? =0